Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Шинные формирователи и буферные регистрыСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте Шинные формирователи (ШФ), называемые также приемопередатчиками, шинными драйверами или магистральными вентиль - буферами, включаются между источником информации и шиной. Они усиливают сигналы по мощности при работе на шину, отключают источник информации от шины, когда он не участвует в обмене, формируют при необходимости требуемые уровни сигналов логической 1 или 0. Двунаправленные ШФ позволяют в зависимости от сигнала управления передавать сигналы в шину или, напротив, принимать их с шины и передавать приемнику данных. Буферные регистры. Буферные регистры служат для подключения к магистрали внешнего устройства. В отличие от ШФ, буферные регистры способны хранить данные. Благодаря этому они могут выполнять временную буферизацию данных, что составляет важнейшую функцию портов. Буферные каскады с тремя состояниями на выходах регистра обеспечивают портам возможность отключения от магистрали под действием управляющих сигналов, а также необходимую нагрузочную способность. Через порты ввода данные от ВУ поступают в магистраль, а через порты вывода данные с магистрали передаются тому или иному модулю. Порты ввода-вывода могут выполнять обе указанные операции.

Параллельные периферийные адаптеры Сложные операции по передаче данных по шине выполняются периферийными адаптерами. Программируемость адаптеров обеспечивает им широкую область применения вследствие изменяемости процедур обмена без изменений в схеме (с помощью команд программы), в том числе и во время работы микропроцессорной системы. Параллельный периферийный адаптер (ППА, PPI) типа Intel 8255А, имеющий отечественный аналог К580ВВ55а (Рисунок 42) имеет три двунаправленных 8-разрядных порта РА, РВ и PC, причем порт PC разделен на два четырехразрядных канала: старший РСH и младший PCL. Обмен информацией между каналами А, В, С и шиной данных МПС производится через буфер данных BD в соответствии с сигналами управления. Блок управления чтением/записью получает стробы чтения и записи

Рисунок 42 - Структура параллельного периферийного адаптера

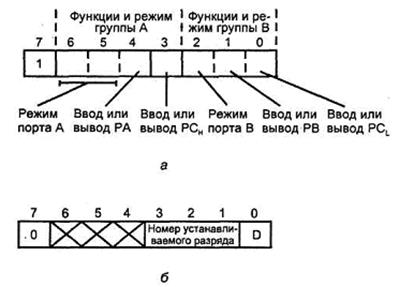

Адресация и направление передач информации определяются согласно таблице 1. Как видно из таблицы, адрес A1A0 = 11 соответствует передаче управляющих слов РУС (УС1) или BSR (УС2), причем чтение по этому адресу запрещено, допускается только запись. Передача двух разных УС при одном и том же адресе возможна только потому, что признаком того или иного УС служит значение старшего бита слов D7. Таким образом, этот бит выполняет дополнительную адресацию управляющих слов. Работа адаптера начинается после загрузки с ШД в РУС управляющего слова УС1, задающего портам адаптера один из трех возможных режимов и направленность порта (ввод или вывод). Возможны три режима работы портов: 0, 1 и 2, причем порт А может работать в любом из трех режимов, порт В только в двух (0 и 1), а режим порта С зависит от режимов портов А и В. Порт С имеет особенности, в отличие от портов А и В, которые оперируют со словами в целом, разряды порта С могут программироваться и использоваться поодиночке. В частности, любой из восьми разрядов порта С может быть установлен или сброшен программным способом. Это нужно для передач сигналов квитирования при обмене через порты А и В в режимах 1 и 2. При работе порта в режиме 1 для него требуются три линии под сигналы управления, в режиме 2 - пять. Режимы работы портов: - режим 0 - однонаправленный ввод/вывод без квитирования, в этом режиме могут работать порты А и В, а также свободные (не занятые передачей служебных сигналов для портов А и В) линии порта С;

Таблица 1

- режим 1 - однонаправленный ввод/вывод с квитированием; - режим 2 - двунаправленный ввод/вывод с квитированием. Квитирование, как известно, позволяет вести асинхронный обмен с учетом готовности абонента к передаче, т.е. иметь переменный темп обмена соответственно возможностям внешнего устройства.

Рисунок 43 - Форматы управляющих слов параллельного периферийного адаптера

Режим 0 В режиме 0 осуществляется прямой однонаправленный ввод-вывод данных без сигналов их сопровождения. Каждый из 4-х портов может быть использован для ввода или вывода независимо от других, так что возможны 16 вариантов режима 0. При вводе поступающая из ВУ информация адаптером не фиксируется и должна присутствовать на его входе во время действия сигнала чтения. При выводе информация от МП фиксируется в буферном регистре порта по заднему фронту сигнала записи и сохраняется до нового цикла вывода или смены режима работы порта. При вводе информация выдается на ШД при выполнении микропроцессором команды IN port, при выводе - при выполнении команды OUT port. Такой вариант соответствует работе "с раздельной шиной", при которой внешним устройствам принадлежит отдельное адресное пространство. Не исключается и организация обращения к портам, как к ячейкам памяти (интерфейс "с общей шиной"). Режим 1 В режиме 1 каждая из двух 12-разрядных групп (А и В) может быть запрограммирована на однонаправленный ввод или вывод с квитированием. При этом входные и выходные данные фиксируются адаптером. По линиям портов Сн и CL передаются управляющие сигналы. Раздельная установка разрядов порта С позволяет ему играть роль схемы управления процедурами ввода-вывода, причем битам порта придается определенное функциональное назначение. Режим 1 рассмотрим в полном объеме, т. к. он хорошо иллюстрирует принципы работы адаптера. При вводе используются следующие управляющие сигналы: - - IBF (Input Buffer Full) - входной буфер полон, сигнал подтверждения загрузки данных; - INT - запрос прерывания. Имея данные для ввода в порт, ВУ при условии IBF = 0 вырабатывает сигнал готовности информации При выводе используются следующие управляющие сигналы: - - - INT — запрос прерывания. При выводе выполняется команда OUT port, и процессор устанавливает адрес порта и данные на ШД. При разрешенных прерываниях далее вырабатывается сигнал Режим 2 Особенности функциональной схемы порта А допускают его применение для двунаправленной передачи между ШД и ВУ. При этом 5 линий порта С передают управляющие сигналы. Двунаправленный асинхронный обмен через порт А выполняется как последовательность нескольких независимых этапов: записи с ШД в адаптер, ввода в адаптер из ВУ, чтения на ШД, вывода в ВУ, некоторые из которых могут совмещаться во времени. Используются сигналы управления: Ввод в адаптер управляющих слов УС1 и УС2 производится программным способом с помощью последовательности команд непосредственной загрузки аккумулятора и вывода данных в адресованный порт. На языке ассемблера фрагмент программы имеет вид: MVI A, b2 OUT port, где загружаемый в аккумулятор байт b2 представляет собою вводимое в адаптер слово УС1 или УС2, a port - адрес регистров управления, шесть старших разрядов которого дают номер (адрес) адаптера, а два младших содержат единицы. Указанный фрагмент программы повторяется столько раз, сколько необходимо для задания адаптеру режима и функций, а выходам порта С нужных значений. Улучшенный вариант адаптера ВВ55А отличается от предшественника ВВ55 работой с расширенным стробом записи, свойственным, в частности, и микропроцессору К1821ВМ85А. Для связи с периферийными устройствами, удаленными от МПС (на расстояние не более 15м), применяется интерфейс ИРПР (интерфейс радиальный параллельный), осуществляющий однонаправленные асинхронные передачи по 8-или 16-разрядной шине (в базовом варианте). Логические требования интерфейса ИРПР могут быть выполнены при использовании адаптера ВВ55/55А.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-19; просмотров: 1465; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.214 (0.008 с.) |

и

и  (это сигналы

(это сигналы  и

и  стандартного интерфейса), сигнал сброса RESET, сигнал выбора адаптера

стандартного интерфейса), сигнал сброса RESET, сигнал выбора адаптера  , получаемый декодированием старших разрядов его адреса, и два младших разряда адреса A1 и А0 для адресации внутренних регистров. Адресуемых объектов 5: три порта (А, В и С), регистр управляющего слова РУС и команда установки/сброса битов порта С BSR (Bit-Set/Reset).

, получаемый декодированием старших разрядов его адреса, и два младших разряда адреса A1 и А0 для адресации внутренних регистров. Адресуемых объектов 5: три порта (А, В и С), регистр управляющего слова РУС и команда установки/сброса битов порта С BSR (Bit-Set/Reset).

- строб загрузки данных в регистр (по заднему фронту);

- строб загрузки данных в регистр (по заднему фронту); (Output Buffer Full) — выходной буфер полон, строб вывода новых данных;

(Output Buffer Full) — выходной буфер полон, строб вывода новых данных; (Acknowledge) — подтверждение приёма внешним устройством;

(Acknowledge) — подтверждение приёма внешним устройством;