Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Архитектура микропроцессора. КлассификацияСодержание книги

Поиск на нашем сайте

Тема 1.2 Организация управления процессом обработки информации План: 1 Структура микропроцессора 2 Аппаратный принцип управления выполнением операций 3 Микропрограммный принцип управления выполнением операций Структура микропроцессора Структура микропроцессора определяет состав и взаимодействие основных устройств и блоков, размещенных на его кристалле. В эту структуру входят: центральный процессор (процессорное ядро), состоящее из устройства управления (УУ), одного или нескольких операционных устройств (ОУ), структурная схема приведена на рисунке 2; внутренняя память (РЗУ, кэш-память, блоки оперативной и постоянной памяти); интерфейсный блок, обеспечивающий выход на системную шину и обмен данными с внешними устройствами через параллельные или последовательные порты ввода/вывода; периферийные устройства (таймерные модули, аналого-цифровые преобразователи, специализированные контроллеры); различные вспомогательные схемы (генератор тактовых импульсов, схемы для выполнения отладки и тестирования, сторожевой таймер и ряд других).

Рисунок 2 – Структурная схема процессора

Операционное устройство (ОУ) - устройство, в котором выполняются операции. Оно включает в качестве узлов регистры, сумматоры, арифметико–логическое устройство (АЛУ), каналы передачи информации, мультиплексоры для коммутации каналов, шифраторы, дешифраторы и т.д. Арифметико–логическое устройство (АЛУ) предназначено для выполнения арифметических и логических операций. Управляющее устройство (УУ) координирует действия узлов операционного устройства; оно вырабатывает в некоторой временной последовательности управляющие сигналы, под действием которых в узлах операционного устройства выполняются требуемые действия. Процесс функционирования операционного устройства распадается на последовательность элементарных действий в его узлах: 1) установка регистра в некоторое состояние (например, запись в регистр R1 числа 0, обозначаемая R1 <− 0); 2) инвертирование содержимого разрядов регистра (например, если регистр R2 содержал двоичное число 101101, то после инвертирования его содержимое будет равно 010010; такое действие обозначают R2 <− ( 3) пересылка содержимого одного узла в другой (например, пересылка содержимого регистра R2 в регистр R1, обозначаемая R1 <− (R2)); 4) сдвиг содержимого узла влево, вправо (например, сдвиг на один разряд влево содержимого регистра R1, обозначаемый R1 <− СдвЛ (R1); 5) счет, при котором число в счетчике (регистре) возрастает или убывает на единицу (Сч<− (Сч ± 1)); 6) сложение (например, R2 <− (R2) + (R1)); 7) сравнение содержимого регистра на равенство с некоторым числом; результат сравнения: лог. 1 (при выполнении равенства) либо лог.0 (при невыполнении равенства); 8) некоторые логические действия (поразрядно выполняемые операции конъюнкции, дизъюнкции и др.). Каждое такое элементарное действие, выполняемое в одном из узлов ОУ в течение одного тактового периода, называется микрооперацией. В определенные тактовые периоды одновременно могут выполняться несколько микроопераций, например R2 <− 0, Сч <− (Сч) - 1. Такая совокупность одновременно выполняемых микроопераций называется микрокомандой, а весь набор микрокоманд, предназначенный для решения определенной задачи, - микропрограммой. Таким образом, если в операционном устройстве предусматривается возможность исполнения п различных микроопераций, то из управляющего устройства выходят п управляющих цепей, каждая из которых соответствует определенной микрооперации. И если необходимо в операционном устройстве выполнить некоторую микрооперацию, достаточно из управляющего устройства по определенной управляющей цепи, соответствующей этой микрооперации, подать сигнал (например, напряжение уровня лог. 1). В силу того, что управляющее устройство определяет микропрограмму, т.е. какие и в какой временной последовательности должны выполняться микрооперации, оно получило название микропрограммного автомата. Формирование управляющих сигналов y1,... ,yп для выполнения микрокоманд может происходить в зависимости от состояния узлов операционного устройства, определяемого сигналами х1,... xs, которые подаются с соответствующих выходов операционного устройства на входы управляющего устройства. Управляющие сигналы y1,..., yп могут также зависеть от внешних сигналов xs+1,..., xL. Для сокращения числа управляющих цепей, выходящих из управляющего устройства (в тех случаях, когда оно конструктивно выполняется отдельно от операционного), микрокоманды могут кодироваться. Существует два принципиально разных подхода к проектированию микропрограммного автомата (управляющего устройства): - использование принципа схемной логики; - использование принципа программируемой логики. В первом случае в процессе проектирования подбирается некоторый набор цифровых микросхем (обычно малой и средней степени интеграции) и определяется такая схема соединения их выводов, которая обеспечивает требуемое функционирование (т.е. функционирование процессора определяется тем, какие выбраны микросхемы и по какой схеме выполнено соединение их выводов). Устройства, основанные на таком принципе схемной логики, способны обеспечивать наивысшее быстродействие при заданном типе технологии элементов. Недостаток этого принципа построения процессора состоит в трудности использования БИС и СБИС. Второй подход предполагает построение процессора с использованием одной или нескольких БИС некоторого универсального устройства, в котором требуемое функционирование (т.е. специализация устройства на выполнение определенных функций) обеспечивается занесением в память устройства определенной программы (или микропрограммы). В зависимости от введенной программы такое универсальное управляющее устройство способно обеспечивать требуемое управление операционным устройством при решении самых разнообразных задач. В этом случае число типов БИС, необходимых для построения управляющего устройства, окажется небольшим, а потребность в БИС каждого типа высокой, что обеспечит целесообразность их выпуска промышленностью. При построении операционных устройств целесообразно широко использовать БИС с таким набором узлов и схемой соединения, которые обеспечили бы решение разнообразных задач. Независимо от решаемой задачи может быть использовано одно и то же универсальное операционное устройство, функционирующее под действием микропрограммы, хранящейся в управляющем устройстве. Следует иметь в виду, что наивысшее быстродействие достигается в процессорах, в которых управляющее устройство строится с использованием принципа схемной логики, а операционное устройство выполняется в виде устройства, специализированного для решения конкретной задачи.

Рисунок 5 - Типовая структура микропроцессорной системы

Разрядность шины адреса определяет максимальный объем адресуемой процессором внешней памяти. Например, 16-разрядная шина А обеспечивает адресацию памяти объемом до 64 Кбайт, а 32-разрядная шина-до 4 Гбайт. В некоторых системах для уменьшения числа необходимых линий связи и соответствующих выводов и контактов используется мультиплексирование линий адреса и данных. В таких системах для передачи адреса и данных используются одни и те же линии связи, на которые сначала выдается адрес, а затем поступают данные. Обмен информацией по мультиплексированной шине AD требует введения отдельного регистра для хранения адреса в процессе пересылки данных. Разрядность шины управления С определяется организацией работы системы, возможностями реализации различных режимов ее функционирования, используемыми методами контроля микропроцессора и других устройств. Поэтому набор передаваемых по шине С управляющих сигналов является индивидуальным для каждой модели микропроцессора. В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы: выполнение основной программы; вызов подпрограммы; обслуживание прерываний и исключений; прямой доступ к памяти. Рассмотрим основные принципы реализации этих режимов.

Режим вызова программы Обращение к подпрограмме реализуется при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR - Jump-to-SubRoutine), которая указывает адрес первой команды вызываемой подпрограммы. Этот адрес загружается в PC, обеспечивая в следующем командном цикле выборку первой команды подпрограммы. Предварительно выполняется процедура сохранения в специальном регистре или ячейке памяти текущего содержимого PC, где хранится адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнения подпрограммы. Возврат к основной программе реализуется при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. По этой команде сохранявшееся содержимое PC снова загружается в программный счетчик, обеспечивая выполнение команды, которая в исходной программе следовала за командой CALL.

Рисунок 7 - Последовательный вызов (вложение) подпрограмм

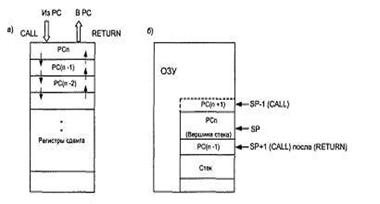

Для реализации этой процедуры используется стек - специальная память магазинного типа, работающая по принципу «последний пришел - первый ушел» (стек типа LIFO -«Last In-First Out»). Существуют различные варианты реализации стека. Регистровый стек (Рисунок 5) реализуется с помощью реверсивных сдвиговых регистров. Каждая команда CALL вызывает ввод в стек очередного содержимого PC. По команде RETURN направление сдвига изменяется и производится извлечение из стека последнего поступившего содержимого PC. Таким образом, обеспечивается выполнение вложенных подпрограмм. Возможное число вложенных подпрограмм определяется глубиной стека, т.е. разрядностью используемых регистров сдвига. Если число вложений превышает глубину стека, первые из введенных в стек значений PC теряются, т.е. возврат к основной программе не будет обеспечен. Поэтому при использовании регистрового стека необходим строгий контроль за числом вложений. Такая реализация стека применяется в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10-20). Значительно более широкие возможности вложения подпрограмм обеспечивает реализация стека в ОЗУ (Рисунок 8). В этом случае часть ОЗУ выделяется для работы в качестве стека. Адресация к ячейкам стека производится с помощью специального регистра - указателя стека SP (Stack Pointer), который вводится в состав УУ процессора. Регистр SP содержит адрес верхней заполненной ячейки стека, в которой хранится значение PC, записанное при выполнении команды CALL.

Рисунок 8 - Варианты реализации стека: регистровый стек (а) и стек, реализуемый в ОЗУ (б)

При поступлении новой команды CALL (операция PUSH) содержимое SP автоматически уменьшается на 1, адресуя следующую, еще незаполненную ячейку стека. Полученный адрес SP-1 выдается на шину А, а на шину D поступает содержимое PC, которое должно сохраняться в стеке. Таким образом, производится последовательное заполнение ячеек стека «снизу-вверх», при этом SP всегда адресует вершину стека. По команде RETURN (операция POP) текущее содержимое SP выдается на шину А, и по шине D производится считывание с вершины стека последнего записанного значения PC. После этого содержимое SP увеличивается на 1, адресуя предыдущее значение PC, хранящееся в стеке. Так как ОЗУ обычно имеет значительный объем, то для размещения стека можно выделить достаточно большое количество ячеек памяти, обеспечивая необходимый уровень вложения подпрограмм.

Рисунок 9 - Реализация конвейерного исполнения команд при идеальной (а) и реальной (б) загрузке 6-ступенчатого конвейера

Реализация каждого этапа занимает один такт машинного времени и производится устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполняется соответствующая микрооперация. При последовательной загрузке в конвейер выбираемых команд каждая его ступень реализует определенный этап выполнения очередной команды. В идеальном варианте при полной загрузке конвейера на его выход в каждом такте будет поступать результат выполнения очередной команды (Рисунок 9, а). В этом случае производительность процессора (операций/с) будет равна его тактовой частоте (тактов/с). Реально отдельные ступени конвейера могут оказаться незагруженными, находясь в состоянии ожидания или простоя. Ожиданием называется состояние исполнительной ступени, когда она не может выполнить требуемую микрооперацию, так как еще не получен необходимый операнд, являющийся результатом выполнения предыдущей команды. Простоем называется состояние ступени, когда она вынуждена пропустить очередной такт, так как поступившая команда не требует выполнения соответствующего этапа. На рисунке 8,б показан пример работы 6-ступенчатого конвейера при выполнении фрагмента реальной программы, когда отдельные ступени оказываются в состоянии ожидания (ОЖ) или простоя (ПР). При использовании в программе разноформатных команд, содержащих различное количество байтов, число состояний простоя и ожидания, которые приходится вводить в процессе выполнения команд, значительно увеличивается. Поэтому принятый во многих RISC-процессорах стандартный 4-байтный формат команд обеспечивает существенное сокращение числа ожиданий и простоев конвейера, что позволяет значительно повысить производительность. Другой причиной снижения эффективности конвейера являются команды условного ветвления. Если выполняется условие ветвления, то приходится производить перезагрузку конвейера командами из другой ветви программы, что требует выполнения дополнительных рабочих тактов и вызывает значительное снижение производительности. Поэтому одним из основных условий эффективной работы конвейера является сокращение числа его перезагрузок при выполнении условных переходов. Эта цель достигается с помощью реализации различных механизмов предсказания направления ветвления, которые обеспечиваются с помощью специальных устройств - блоков предсказания ветвления, вводимых в структуру процессора. Возможность повышения производительности процессора достигается также при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной. В этих процессорах реализуется параллельная работа нескольких исполнительных конвейеров, в каждый из которых поступает для выполнения одна из выбранных и декодированных команд. В идеальном случае число одновременно выполняемых команд равно числу операционных устройств, включенных в исполнительные конвейеры. Однако при выполнении реальных программ трудно обеспечить полную загрузку всех исполнительных конвейеров, поэтому на практике эффективность использования суперскалярной структуры оказывается несколько ниже. Современные суперскалярные процессоры содержат до 4 до 10 различных операционных устройств, параллельная работа которых обеспечивает выполнение за один такт в среднем от 2 до 6 команд. Эффективная одновременная работа нескольких исполнительных конвейеров обеспечивается путем предварительной выборки-декодирования ряда команд и выделения из них группы команд, которые могут выполняться одновременно. В современных суперскалярных процессорах производится выборка нескольких десятков команд, которые декодируются, анализируются и группируются для параллельной загрузки в исполнительные конвейеры. Вывод: Большинство микропроцессорных систем имеет магистрально-модульную структуру, в которой отдельные устройства (модули), входящие в состав системы, обмениваются информацией по общей системной шине – магистрали (фон Неймановская архитектура). Системная шина содержит несколько десятков проводников, которые в соответствии с их функции-ональным назначением подразделяются на отдельные шины - адреса А, данных D и управления С. В процессе функционирования микропроцессорной системы реализуются следующие основные режимы ее работы: выполнение основной программы; вызов подпрограммы; обслуживание прерываний и исключений; прямой доступ к памяти. В микропроцессорах с Гарвардской архитектурой и физическим разделением памяти команд и данных, реализуется конвейерный принципвыполнения команд, обеспечивая высокую производительность.При этом процесс выполнения команды разбивается на ряд этапов: выборка очередной команды (ВК); декодирование выбранной команды (ДК); формирование адреса операнда (ФА); прием операнда из памяти (ПО); выполнение операции (ВО); размещение результата в памяти (РР). Повысить производительность процессора можно при введении в структуру процессора нескольких параллельно включенных операционных устройств, обеспечивающих одновременное выполнение нескольких операций. Такая структура процессора называется суперскалярной. Контрольные вопросы: 1 Что представляет собой архитектура процессора фон Неймана типа? 2 Каков состав общей шины в структуре процессора? 3 Какие режимы при работе процессора? 4 Объяснить принцип конвейерной обработки команд. 5 Каков принцип работы процессора с суперскалярной структурой?

Тема 1.4 Ассемблерная мнемоника. Структура и форматы команд. Виды адресации. Система команд микропроцессора

План: 1 Язык ассемблера. Основные понятия 2 Символы языка ассемблера 3 Типы операторов ассемблера 4 Директивы ассемблера 5 Система команд процессора Язык ассемблера. Основные понятия Язык ассемблера - это символическое представление машинного языка. Все процессы в машине на самом низком, аппаратном уровне приводятся в действие только командами (инструкциями) машинного языка. Отсюда понятно, что, несмотря на общее название, язык ассемблера для каждого типа компьютера свой. Программа на ассемблере представляет собой совокупность блоков памяти, называемых сегментами памяти. Программа может состоять из одного или нескольких таких блоков-сегментов. Каждый сегмент содержит совокупность предложений языка, каждое из которых занимает отдельную строку кода программы. Предложения ассемблера бывают четырех типов: 1) команды или инструкции, представляющие собой символические аналоги машинных команд. В процессе трансляции инструкции ассемблера преобразуются в соответствующие команды системы команд микропроцессора; 2) макрокоманды -оформляемые определенным образом предложения текста программы, замещаемые во время трансляции другими предложениями; 3) директивы, являющиеся указанием транслятору ассемблера на выполнение некоторых действий. У директив нет аналогов в машинном представлении; 4) строки комментариев, содержащие любые символы, в том числе и буквы русского алфавита. Комментарии игнорируются транслятором. Рисунок 11 - Формат директив

Рисунок 12 - Формат команд и макрокоманд

На этих рисунках: имя метки - идентификатор, значением которого является адрес первого байта того предложения исходного текста программы, которое он обозначает; имя - идентификатор, отличающий данную директиву от других одноименных директив. В результате обработки ассемблером определенной директивы этому имени могут быть присвоены определенные характеристики; код операции (КОП) и директива - это мнемонические обозначения соответствующей машинной команды, макрокоманды или директивы транслятора; операнды - части команды, макрокоманды или директивы ассемблера, обозначающие объекты, над которыми производятся действия. Операнды ассемблера описываются выражениями с числовыми и текстовыми константами, метками и идентификаторами переменных с использованием знаков операций и некоторых зарезервированных слов. Синтаксические диаграммы помогаютнайти и затем пройти путь от входа диаграммы (слева) к ее выходу (направо). Если такой путь существует, то предложение или конструкция синтаксически правильные. Если такого пути нет, значит эту конструкцию компилятор не примет.

Символы языка ассемблера Допустимыми символами при написании текста программ являются: 1) все латинские буквы: A-Z, a-z. При этом заглавные и строчные буквы считаются эквивалентными; 2) цифры от 0 до 9; 3) знаки?, @, $, _, &; 4) разделители ,. [ ] () < > { } + / * %! ' "? \ = # ^. Предложения ассемблера формируются из лексем, представляющих собой синтаксически неразделимые последовательности допустимых символов языка, имеющие смысл для транслятора. Лексемами являются: 1) идентификаторы - последовательности допустимых символов, использующиеся для обозначения таких объектов программы, как коды операций, имена переменных и названия меток. Правило записи идентификаторов заключается в следующем: идентификатор может состоять из одного или нескольких символов; 2) цепочки символов - последовательности символов, заключенные в одинарные или двойные кавычки; 3) целые числав одной из следующих систем счисления: двоичной, десятичной, шестнадцатеричной. Отождествление чисел при записи их в программах на ассемблере производится по определенным правилам: 4) десятичные числа не требуют для своего отождествления указания каких-либо дополнительных символов, например 25 или 139. Для отождествления в исходном тексте программы двоичных чисел необходимо после записи нулей и единиц, входящих в их состав, поставить латинское “ b ”, например 10010101 b. 5) шестнадцатеричные числа имеют больше условностей при своей записи: Во-первых, они состоят из цифр 0...9, строчных и прописных букв латинского алфавита a, b, c, d, e, f или A, B, C, D, E, F. Во-вторых, у транслятора могут возникнуть трудности с распознаванием шестнадцатеричных чисел из-за того, что они могут состоять как из одних цифр 0...9 (например, 190845), так и начинаться с буквы латинского алфавита (например, ef15). Для того чтобы "объяснить" транслятору, что данная лексема не является десятичным числом или идентификатором, программист должен специальным образом выделять шестнадцатеричное число. Для этого на конце последовательности шестнадцатеричных цифр, составляющих шестнадцатерич-ное число, записывают латинскую букву “ h ”. Это обязательное условие. Если шестнадцатеричное число начинается с буквы, то перед ним записывается ведущий ноль: 0 ef15 h. Практически каждое предложение содержит описание объекта, над которым или при помощи которого выполняется некоторое действие. Эти объекты называются операндами. Их можно определить так: операнды - это объекты (некоторые значения, регистры или ячейки памяти), на которые действуют инструкции или директивы, либо это объекты, которые определяют или уточняют действие инструкций или директив. Возможно, провести следующую классификацию операндов: постоянные или непосредственные операнды; адресные операнды; перемещаемые операнды; счетчик адреса; регистровый операнд; базовый и индексный операнды; структурные операнды; записи. Операнды являются элементарными компонентами, из которых формируется часть машинной команды, обозначающая объекты, над которыми выполняется операция. В более общем случае операнды могут входить как составные части в более сложные образования, называемые выражениями. Выражения представляют собой комбинации операндов и операторов, рассматриваемые как единое целое. Результатом вычисления выражения может быть адрес некоторой ячейки памяти или некоторое константное (абсолютное) значение.

Типы операторов ассемблера Перечислим возможные типы операторов ассемблера и синтаксические правила формирования выражений ассемблера: арифметические операторы; операторы сдвига; операторы сравнения; логические операторы; индексный оператор; оператор переопределения типа; оператор переопределения сегмента; оператор именования типа структуры; оператор получения сегментной составляющей адреса выражения; оператор получения смещения выражения.

Директивы ассемблера

Директивы ассемблера бывают: 1) Директивы сегментации. В ходе предыдущего обсуждения мы выяснили все основные правила записи команд и операндов в программе на ассемблере. Открытым остался вопрос о том, как правильно оформить последовательность команд, чтобы транслятор мог их обработать, а микропроцессор - выполнить. При рассмотрении архитектуры микропроцессора мы узнали, что он имеет шесть сегментных регистров, посредством которых может одновременно работать: с одним сегментом кода; с одним сегментом стека; с одним сегментом данных; с тремя дополнительными сегментами данных. Физически сегмент представляет собой область памяти, занятую командами и (или) данными, адреса которых вычисляются относительно значения в соответствующем сегментном регистре. Синтаксическое описание сегмента на ассемблере представляет собой конструкцию, изображенную на рисунке 13:

Рисунок 13 - Синтаксическое описание сегмента на ассемблере

Важно отметить, что функциональное назначение сегмента несколько шире, чем простое разбиение программы на блоки кода, данных и стека. Сегментация является частью более общего механизма, связанного с концепцией модульного программирования. Она предполагает унификацию оформления объектных модулей, создаваемых компилятором, в том числе с разных языков программирования. Это позволяет объединять программы, написанные на разных языках. Именно для реализации различных вариантов такого объединения и предназначены операнды в директиве SEGMENT. 2) Директивы управления листингом. Директивы управления листингом делятся на следующие группы: общие директивы управления листингом; директивы вывода в листинг включаемых файлов; директивы вывода блоков условного ассемблирования; директивы вывода в листинг макрокоманд; директивы вывода в листинг информации о перекрестных ссылках; директивы изменения формата листинга.

Система команд процессора

Система команд процессора представлена на рисунке 14. Рассмотрим основные группы команд.

Рисунок 14 - Классификация команд ассемблера

Команды бывают: 1 Команды пересылки данных. Эти команды занимают очень важное место в системе команд любого процессора. Они выполняют следующие важнейшие функции: загрузка (запись) содержимого во внутренние регистры процессора; сохранение в памяти содержимого внутренних регистров процессора; копирование содержимого из одной области памяти в другую; запись в устройства ввода/вывода и чтение из устройств ввода/вывода. В некоторых процессорах все эти функции выполняются одной единственной командой MOV (для байтовых пересылок - MOVB ) но с различными методами адресации операндов. В других процессорах помимо команды MOV имеется еще несколько команд для выполнения перечисленных функций. Также к командам пересылки данных относятся команды обмена информацией (их обозначение строится на основе слова Exchange). Может быть предусмотрен обмен информацией между внутренними регистрами, между двумя половинами одного регистра (SWAP) или между регистром и ячейкой памяти. 2 Арифметические команды. Арифметические команды рассматривают коды операндов как числовые двоичные или двоично-десятичные коды. Эти команды могут быть разделены на пять основных групп: команды операций с фиксированной запятой (сложение, вычитание, умножение, деление); команды операций с плавающей запятой (сложение, вычитание, умножение, деление); команды очистки; команды инкремента и декремента; команда сравнения. 3 Команды операций с фиксированной запятой работают с кодами в регистрах процессора или в памяти как с обычными двоичными кодами. Команды операций с плавающей запятой (точкой) используют формат представления чисел с порядком и мантиссой (обычно эти числа занимают две последовательные ячейки памяти). В современных мощных процессорах набор команд с плавающей запятой не ограничивается только четырьмя арифме-тическими действиями, а содержит и множество других более сложных команд, например, вычисление тригонометрических функций, логарифмических функций, а также сложных функций, необходимых при обработке звука и изображения. 4 Команды очистки предназначены для записи нулевого кода в регистр или ячейку памяти. Эти команды могут быть заменены командами пересылки нулевого кода, но специальные команды очистки обычно выполняются быстрее, чем команды пересылки. 5 Команды инкремента (увеличения на единицу) и декремента (уменьшения на единицу) также бывают очень удобны. Их можно в принципе заменить командами суммирования с единицей или вычитания единицы, но инкремент и декремент выполняются быстрее, чем суммирование и вычитание. Эти команды требуют одного входного операнда, который одновременно является и выходным операндом. 6 Команда сравнения предназначена для сравнения двух входных операндов. По сути, она вычисляет разность этих двух операндов, но выходного операнда не формирует, а всего лишь изменяет биты в регистре состояния процессора по результату этого вычитания. Следующая за командой сравнения команда (обычно это команда перехода) будет анализировать биты в регистре состояния процессора и выполнять действия в зависимости от их значений. В некоторых процессорах предусмотрены команды цепочечного сравнения двух последовательностей операндов, находящихся в памяти. 7 Логические команды. Логические команды выполняют над операндами логические (побитовые) операции, то есть они рассматривают коды операндов не как единое число, а как набор отдельных битов. Этим они отличаются от арифметических команд. Логические команды выполняют следующие основные операции: логическое И, логическое ИЛИ, сложение по модулю 2 (Исключающее ИЛИ); логические, арифметические и циклические сдвиги; проверка битов и операндов; установка и очистка битов (флагов) регистра состояния процессора (PSW). Команды логических операций позволяют побитно вычислять основные логические функции от двух входных операндов. Кроме того, операция И используется для принудительной очистки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие очистки, установлены в нуль). Операция ИЛИ применяется для принудительной установки заданных битов (в качестве одного из операндов при этом используется код маски, в котором разряды, требующие установки в единицу, равны единице). Операция «Исключающее ИЛИ» используется для инверсии заданных битов (в качестве одного из операндов при этом применяется код маски, в котором биты, подлежащие инверсии, установлены в единицу). Команды требуют двух входных операндов и формируют один выходной операнд. 8 Команды сдвигов позволяют побитно сдвигать код операнда вправо (в сторону младших разрядов) или влево (в сторону старших разрядов). Тип сдвига (логический, арифметический или циклический) определяет, каково будет новое значение старшего бита (при сдвиге вправо) или младшего бита (при сдвиге влево), а также определяет, будет ли где-то сохранено прежнее значение старшего бита (при сдвиге влево) или младшего бита (при сдвиге вправо). Циклические сдвиги позволяют сдвигать биты кода операнда по кругу (по часовой стрелке при сдвиге вправо или против часовой стрелки при сдвиге влево). При этом в кольцо сдвига может входить или не входить флаг переноса. В бит флага переноса (если он используется) записывается значение старшего бита при циклическом сдвиге влево и младшего бита при циклическом сдвиге вправо. Соответственно, значение бита флага переноса будет переписываться в младший разряд при циклическом сдвиге влево и в старший разряд при циклическом сдвиге вправо. 9 Команды переходов. Команды переходов предназначены для организации всевозможных циклов, ветвлений, вызовов подпрограмм и т.д., то есть они нарушают последовательный ход выполнения программы. Эти команды записывают в регистр-счетчик команд новое значение и тем самым вызывают переход процессора не к следующей по порядку команде, а к любой другой команде в памяти программ. Некоторые команды переходов предусматривают в дальнейшем возврат назад, в точку, из которой был сделан переход, другие не предусматривают этого. Если возврат предусмотрен, то текущие параметры процессора сохраняются в стеке. Если возврат не предусмотрен, то текущие параметры процессора не сохраняются. Команды переходов без возврата делятся на две группы: команды безусловных переходов; команды условных переходов. В обозначениях этих команд используются слова Branch (ветвление) и Jump (прыжок). Команды безусловных переходов вызывают переход в новый адрес независимо ни от чего. Они могут вызывать переход на указанную величину смещения (вперед или назад) или же на указанный адрес памяти. Величина смещения или новое значение адреса указываются в качестве входного операнда. Команды условных переходов вызывают переход не всегда, а только при выполнении заданных условий. В качестве таких условий обычно выступают значения флагов в регистре состояния процессора (PSW). То есть условием перехода является результат предыдущей операции, меняющей значения флагов. Всего таких условий перехода может быть от 4 до 16. Несколько примеров команд условных переходов: переход, если равно нулю; переход, если не равно нулю; переход, если есть переполнение; переход, если нет переполнения; переход, если больше нуля; переход, если меньше или равно нулю. Если условие перехода выполняется, то производится загрузка в регистр-счетчик команд нового значения. Если же услов

|

||||

|

Последнее изменение этой страницы: 2016-04-19; просмотров: 407; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 52.15.113.71 (0.015 с.) |

));

)); Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм, т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (Рисунок 7). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм, т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (Рисунок 7). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.