Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Микропрограммный принцип управления выполнением операцийСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

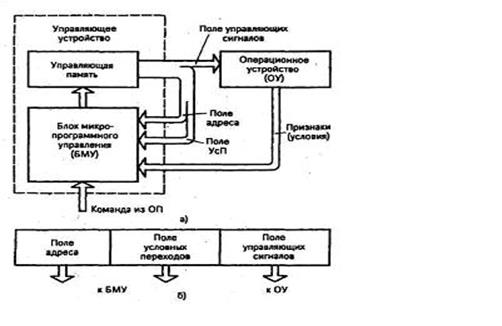

Мы рассмотрели выполнение операций процессором в виде последовательности микрокоманд. Можно предусмотреть другой способ формирования управляющих сигналов, под действием которых в операционном устройстве выполняются микрокоманды. Управляющие сигналы у1,...., уп на выходе управляющего устройства в каждом тактовом периоде имеют уровни лог. 0 и лог. 1. Таким образом, каждой микрокоманде на выходе управляющего устройства соответствует некоторая кодовая комбинация. Такие кодовые комбинации, называемые кодовыми комбинациями микрокоманд (или просто микрокомандами), можно хранить в специально предназначенной для них управляющей памяти. При этом выполнение операции сводится к выборке из управляющей памяти последовательно микрокоманд микропрограммы и выдаче с их помощью управляющих сигналов у1,...., уп в операционное устройство. В управляющей памяти можно хранить много микропрограмм, предназначенных для выполнения различных операций. По выбранной из оперативной памяти команде в управляющей памяти находится соответствующая команде микропрограмма. Далее путем последовательного считывания микрокоманд найденной микропрограммы и их выполнения в операционном устройстве реализуется предусматриваемая командой операция. Такой способ реализации операций называется микропрограммным, а построенное на этом способе управляющее устройство - управляющим устройством с программируемой логикой. На рисунке 4 изображена структурная схема процессора с управляющим устройством, построенным по принципу программируемой логики. Функции блока микропрограммного управления (БМУ) сводятся к определению адреса очередной микрокоманды (МК) в управляющей памяти (УП). Поступающая из оперативной памяти (ОП) команда содержит адрес первой МК той микропрограммы, которая реализует предусматриваемую командой операцию. Так решается задача поиска в УП микропрограммы, соответствующей данной команде. Адреса всех последующих МК определяются в БМУ следующим образом. В формате МК (Рисунок 3) предусматривается поле адреса, которое содержит адрес очередной МК. Считав из УП микрокоманду, по содержимому ее поля адреса определим адрес следующей МК. Но так можно получить адреса МК при отсутствии в алгоритме разветвлений, т.е. условных переходов (УсП). Для реализации условных переходов в МК надо предусмотреть поле условных переходов, в котором указывается, имеет ли место условный или безусловный переход и при условном переходе - на значения каких условий следует ориентироваться при определении адреса очередной МК.

Рисунок 4 – Структурная схема процессора с микропрограммным принципом управления

Пусть поле условных переходов построено следующим образом. Один из разрядов поля указывает вид перехода (например, 0 в этом разряде означает безусловный переход, 1 - условный переход). Кроме того, для каждого условия в поле условных переходов имеется разряд, указывающий участие данного условия в определении адреса. Если условный переход осуществляется по некоторому условию, то адрес очередной МК будем формировать замещением младшего разряда содержимого поля адреса текущей МК значением соответствующего условия (такую операцию называют модификацией адреса). Получается разветвление на два направления. В зависимости от значения условия образуются два различающихся в младшем разряде адреса и очередная МК считывается из одной либо другой ячейки УП. Если модифицировать два разряда содержимого поля адреса, то можно осуществить разветвление на четыре направления. Поле управляющих сигналов МК используется для подачи управляющих сигналов в операционное устройство (ОУ). Таким образом, микрокоманда может быть разбита на две части: одна часть - поле адреса и поле условных переходов - определяет функционирование БМУ при нахождении адреса очередной МК и может быть названа микрокомандой БМУ; другая часть - поле управляющих сигналов - определяет функционирование ОУ и может быть названа микрокомандой ОУ. Машинное представление команды в памяти микроконтроллера называется объектным кодом. Организация работы процессора состоит из фаз: 1) выборка очередной команды (ВК); 2) декодирование выбранной команды (ДК); 3) формирование адреса операнда (ФА); 4) прием операнда из памяти (ПО); 5) выполнение операции (ВО); 6) размещение результата в памяти (РР). Реализация каждого этапа занимает один такт машинного времени и производится устройствами и блоками процессора, образующими ступени исполнительного конвейера, на каждой из которых выполняется соответствующая микрооперация. При последовательной загрузке в конвейер выбираемых команд каждая его ступень реализует определенный этап выполнения очередной команды. Время для исполнения одной команды называется командным циклом. Основное содержание фазы выборки состоит в считывании первого байта (слова) команды из памяти микроконтроллера и его ввод в специальный регистр команд IR (Instruction Register). Независимо от архитектуры процессора в нем имеются кроме памяти программ CSEG (Code Segment) и памяти данных DSEG (Data Segment), программно доступные регистры RSEG (Register Segment). Внутренняя логическая организация RSEG очень разнообразна и играет определяющую роль в классификации архитектур. Одним из основных является регистр PC (Program Counter)-программный счетчик. Он связан с с адресацией памяти программ и служит указателем следующего элемента программной последовательности, подлежащей выборке и исполнению. Считывание байта происходит по адресу, хранящемся в программном счетчике PC. Одновременно с этим содержимое PC увеличивается на 1 или 2, указывая на следующий элемент объектного кода. Фаза выборки одинакова для всех команд. Вывод: Существует два принципиально разных подхода к проектированию микропрограммного автомата (управляющего устройства) процессора с использованием схемной логики и с использованием программируемой логики. В первом случае в процессе проектирования подбирается некоторый набор цифровых микросхем (обычно малой и средней степени интеграции) и определяется такая схема соединения их выводов, которая обеспечивает требуемое функционирование (т.е. функционирование процессора определяется тем, какие выбраны микросхемы и по какой схеме выполнено соединение их выводов). Устройства, основанные на таком принципе схемной логики, способны обеспечивать наивысшее быстродействие при заданном типе технологии элементов. Недостаток этого принципа построения процессора состоит в трудности использования БИС и СБИС. Второй подход предполагает построение процессора с использованием одной или нескольких БИС некоторого универсального устройства, в котором требуемое функционирование (т.е. специализация устройства на выполнение определенных функций) обеспечивается занесением в память устройства определенной программы (или микропрограммы). В зависимости от введенной программы такое универсальное управляющее устройство способно обеспечивать требуемое управление операционным устройством при решении самых разнообразных задач. В этом случае число типов БИС, необходимых для построения управляющего устройства, окажется небольшим, а потребность в БИС каждого типа высокой, что обеспечит целесообразность их выпуска промышленностью. Контрольные вопросы: 1 Пояснить структуру процессора. 2 В чем суть аппаратного принципа управления операциями микропро-цессора? 3 Пояснить работу микропроцессора с микропрограммным управлением. 4 Каково назначение управляющего устройства микропроцессора? 5 Что представляет собой операционное устройство? 6 Каковы преимущества принципа микропрограммного управления микропроцессором?

|

||||

|

Последнее изменение этой страницы: 2016-04-19; просмотров: 558; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.129.73.6 (0.009 с.) |