Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Программируемые связные адаптерыСодержание книги

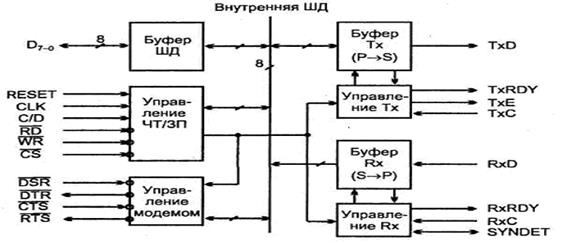

Поиск на нашем сайте При увеличении расстояний, на которые передаются данные, параллельные связи становятся неприемлемо сложными и дорогими. В этом случае применяют преобразование параллельных данных в последовательные для их передачи по одной сигнальной линии. Тракт передачи последовательных данных в общем случае включает в себя источник и приемник данных, программируемые связные адаптеры (ПСА). На рисунке 44 показана структура ПСА (PCI, Programmable Communication Interface) типа 8251А фирмы Intel, аналогом которого является отечественный ПСА К580ВВ51А. Согласно типу реализуемых протоколов этот ПСА называют универсальным синхронно-асинхронным приемопередатчиком (УСАПП), чему в английской терминологии соответствует USART - Universal Synchronous/Asynchronous Receiver/Transmitter. Адаптеры, в которых реализуются только асинхронные протоколы, называются УАПП (UART - Universal Asynchronous Receiver/Transmitter). В МПС адаптер используется как ВУ, программируется процессором для работы с различной аппаратурой, принимает от процессора символы в параллельной форме и преобразует их в последовательную для передачи или получает последовательные данные и преобразует их в параллельные символы для процессора. Кроме того, адаптер сигнализирует процессору о готовности принять новый символ для передачи или о том, что получил символ для процессора. В любое время процессор может читать слово состояния адаптера.

Рисунок 44 - Структура программируемого связного адаптера

Буфер ШД - двунаправленный, восьмиразрядный, с тремя состояниями. Он связывает адаптер с системной шиной данных и принимает данные по командам OUT port, выдает - по командам IN port. Через буфер передаются также управляющие и командные слова и слово состояния адаптера. В буфере имеются регистры данных (входной и выходной), команд и состояния. Блок управления чтением/записью принимает сигналы от системной шины данных и генерирует сигналы управления работой всех блоков адаптера. Выводы и сигналы ПСА. Выводы и сигналы ПСА имеют следующее назначение: - RESET - установка адаптера в исходное состояние, после него адаптер находится в бездействии до записи нового набора управляющих слов для определения задаваемых ему функций. В состояние бездействия адаптер вводится также программой по команде сброса; - CLK - вход тактовой частоты для внутреннего тактирования процессора. Внешние входы и выходы адаптера не привязаны к тактам сигнала CLK, но частота этого сигнала должна быть выше битовой частоты передачи данных не менее чем в 30 раз; - - C/D (Control/Data) - указывает на тип передаваемой информации, при единичном значении этого сигнала вводятся управляющие слова или выводится слово состояния адаптера, при нулевом - передаются данные. Вместе с сигналами

Таблица 2

Адаптер имеет набор управляющих входных и выходных сигналов для управления модемом. Модем указан здесь как наиболее типичное устройство, работающее во взаимодействии с ПСА, хотя, в сущности, это сигналы общего назначения, которые могут быть использованы и для управления другими устройствами. Для управления модемом (терминалом) имеются две пары сигналов квитирования: - - - - Передатчик ПСА. Буфер передатчика адаптера (буфер Тх) принимает параллельные данные от буфера ШД, преобразует их в поток последовательных битов, вводит в этот поток служебные символы или биты и выдает составленный необходимым образом поток битов на вывод TxD по отрицательным фронтам импульсов частоты ТхС. Передача начинается после ее разрешения и при условии - TxRDY - этот выходной сигнал указывает процессору на готовность передатчика адаптера принять символ данных. Сигнал может проверяться чтением слова состояния или использоваться как запрос прерывания (он может маскироваться битом TxEN командного слова). Автоматически сбрасывается передним фронтом строба записи WR, когда символ данных загружается из процессора; - ТхЕ - сигнал устанавливается, когда адаптер не имеет символа для передачи (входной буфер в блоке "буфер ШД" пуст, и после выхода символа из сдвигающего регистра передатчика этот регистр будет нечем загрузить). Сбрасывается после получения символа от процессора, если передача разрешена, и остается высоким, если передача запрещена соответствующим битом командного слова. Сигнал может быть использован для индикации конца режима передачи и оповещения процессора о моменте переключения линии передачи на другое направление в полудуплексном режиме работы. В синхронном режиме высокий уровень сигнала показывает, что символ не был загружен и в поток данных следует вводить синхросимволы. Пока передаются синхросимволы, высокий уровень сигнала сохраняется; - ТхС и RxC - сигналы синхронизации передатчика и приемника, задающие скорость следования последовательных битов. При синхронных передачах бодовая скорость равна частоте ТхС (RxC), при асинхронных она является частью частоты ТхС (RxC) (это 1, или 1/16 или 1/64 от ТхС или RxC). Очень часто частоты ТхС и RxC идентичны. Их синхронности с сигналом CLK не требуется. Приемник ПСА. Буфер приемника принимает последовательные данные, преобразует их в параллельные, проверяет биты или символы, специфичные для посылок данного типа и посылает принятый символ в процессор. Вывод RxD служит входом последовательных данных. Блок управления приемником Rx обеспечивает управление всеми действиями, связанными с приемом информации. Схемы этого блока предотвращают восприятие неиспользуемой линии данных как L-активной в режиме паузы. Для начала приема требуется появление высокого уровня (марки) на входе RxD после сброса системы. Если это выполняется, то разрешается поиск отрицательного фронта входного сигнала (старт-бита). Истинность старт-бита устанавливается проверкой уровня сигнала в его середине. Ошибки работы адаптера устанавливают соответствующие биты в слове состояния (четности, формата или переполнения, если новая информация замещает старую раньше, чем она была использована). RxRDY - выходной сигнал, показывающий, что адаптер имеет символ, готовый к выводу в процессор. Может проверяться чтением слова состояния или использоваться как запрос прерывания для процессора. Если команда разрешения приема RxEN отсутствует, то сигнал RxRDY находится в состоянии сброса. Отсутствие чтения принятого символа из выходного регистра адаптера до появления следующего ведет к загрузке нового символа и потере старого. Устанавливается ошибка переполнения. SYNDET (SYNC Detect/Break Detect) этот вывод в синхронном режиме используется как SYNDET и может быть входом или выходом в зависимости от программирования адаптера. При внутренней синхронизации является выходом и устанавливается как признак выявления синхросимвола в режиме приема. Если запрограммированы два синхросимвола, SYNDET установится в середине последнего бита второго синхросимвола. Сигнал автоматически сбрасывается после операции чтения состояния. Когда используется как входной (режим внешней синхронизации), его появление заставляет адаптер начать прием данных. В асинхронном режиме вывод используется для сигнала Break Detect, который устанавливается при низком уровне на интервалах стоп-битов в двух последовательных посылках. Сигнал может быть выявлен чтением слова состояния. Сбрасывается при сбросе адаптера или возвращении входного сигнала к нормальному состоянию (появлению единиц на интервалах стоп-битов).

|

|||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-19; просмотров: 819; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.108 (0.007 с.) |

,

,  и

и  - сигналы, смысл которых уже известен (стробы чтения и записи и сигнал выбора микросхемы);

- сигналы, смысл которых уже известен (стробы чтения и записи и сигнал выбора микросхемы); (Data Set Ready) - запрос готовности передатчика терминала, сигнал связан с одноразрядным портом и может быть проверен процессором чтением слова состояния. Низкий уровень этого сигнала говорит о том, что модем (терминал) имеет информацию для передачи процессору;

(Data Set Ready) - запрос готовности передатчика терминала, сигнал связан с одноразрядным портом и может быть проверен процессором чтением слова состояния. Низкий уровень этого сигнала говорит о том, что модем (терминал) имеет информацию для передачи процессору; (Data Terminal Ready) - этот сигнал является реакцией на запрос

(Data Terminal Ready) - этот сигнал является реакцией на запрос  (Request to Send) - сигнал связан с одноразрядным выходным портом. Является запросом от адаптера готовности приемника терминала принять данные. Задается программированием соответствующего бита в командном слове, когда процессором разрешен обмен с модемом;

(Request to Send) - сигнал связан с одноразрядным выходным портом. Является запросом от адаптера готовности приемника терминала принять данные. Задается программированием соответствующего бита в командном слове, когда процессором разрешен обмен с модемом; (Clear to Send) - сигнал готовности приемника терминала принять данные. Низкий уровень этого сигнала разрешает адаптеру передачу последовательных данных, если установлен бит TxEN в командном слове. При снятии TxEN или

(Clear to Send) - сигнал готовности приемника терминала принять данные. Низкий уровень этого сигнала разрешает адаптеру передачу последовательных данных, если установлен бит TxEN в командном слове. При снятии TxEN или