Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Программируемые интервальные таймерыСодержание книги

Поиск на нашем сайте

Программируемые интервальные таймеры (ПИТ, PIT) выполняют операции связанные с временами, частотами и интервалами. ПИТ ВИ54 серий К1821 и К1860 (аналог микросхемы Intel 8254), входящий также в состав современных интегрированных периферийных СБИС и библиотек для СБИС программируемой логики, - трехканальный, содержит три 16-разрядных счетчика с независимыми режимами работы при изменениях входной частоты от нулевой до 10МГц (для разных модификаций максимальные частоты 5; 8 и 10 МГц). Таймеры могут работать в шести режимах в двоичной или двоично-десятичной системах счисления. Структура ИС ВИ54. Структура ИС ВИ54 показана на рисунок 60, а. Двунаправленный буфер данных БД с тремя состояниями выхода связывает ПИТ с шиной данных системы. Блок управления чтением-записью принимает от шин МПС сигналы

Рисунок 50 - Структура интервального таймера (а) и одного из его каналов (б)

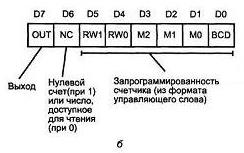

Внутренняя структура счетчика CTRi приведена на рисунок 50,б. Регистр управляющего слова РУС хранит загруженные в таймер сведения о назначенных режимах работы счетчиков. Регистр состояния PC вместе с защелкой ЗРС (защелкой регистра состояния) содержат текущее состояние РУС, состояние выхода OUT и флажок нуля счета. Собственно счетчик, обозначенный как СЭ (счетный элемент) - 16-разрядный синхронный вычитающий, со сбросом. Его состояние отслеживается двумя 8-разрядными защелками счетного элемента ЗСЭ для старшего (Н) и младшего (L) байтов числа, формируемого в счетчике. Имеется команда Counter Latch, по которой текущее число СЭ фиксируется в защелках до его считывания процессором, после чего защелки вновь возвращаются в режим слежения за числом в СЭ. Управляющая логика обеспечивает поочередный вывод содержимого защелок на внутреннюю шину данных для вывода 16-разрядных слов по 8-разрядным шинам. Состояние СЭ может читаться только через защелки. СЭ имеют на входах 8-разрядные регистры счетного элемента РСЭ, хранящие старший и младший байты нового числа, подлежащего записи в СЭ. Управляющая логика обеспечивает загрузку регистров с внутренней шины данных для побайтной передачи 16-разрядных чисел. В СЭ оба байта загружаются одновременно. При программировании счетчика регистры РСЭ сбрасываются. Формат управляющего слова показан на рисунке 51.

Рисунок 51 - Форматы управляющего слова

Вывод: Стандартный интерфейс - совокупность унифицированных технических, программных и конструктивных средств, необходимых для реализации взаимодействия различных функциональных элементов в автоматических системах обработки информации (СОИ) при условиях, предписанных стандартом и направленных на обеспечение информационной, электрической и конструктивной совместимости указанных элементов. Шина - совокупность линий, сгруппированных по функциональному назначению. Операции на шине называются транзакциями. Основные виды транзакций – транзакции записи и транзакции чтения. Если к шине подключено большое число устройств, ее пропускная способность падает, поскольку слишком частая передача прав управления шиной от одного устройства к другому приводит к ощутимым задержкам. По этой причине во многих ЭВМ предпочтение отдается использованию нескольких шин, образующих определенную иерархию. Для построения гибкой системы с развитым интерфейсом, широко применяются шинные формирователи, буферные регистры. Для связи на удаленных расстояниях используют параллельные периферийные адаптеры (до 15м), последовательный связной адаптер (до нескольких км), а для обслуживания запросов от различных периферийных устройств – контроллер прерываний. Значительно увеличить производительность позволяет контроллер прямого доступа к памяти. Организация временных интервалов и формирование различных управляющих сигналов во времени обеспечивают программируемые таймеры. Контрольные вопросы: 1 Какие виды совместимости должны обеспечивать стандартные интер-фейсы? 2 Пояснить понятие «протокол». 3 Какие функции выполняют буферные регистры? 4 Пояснить режимы работы параллельного программируемого адаптера. 5 Пояснить работу приемника программируемого связного адаптера. 6 Какие функции можно реализовать с помощью программируемого интервального таймера?

|

||||

|

Последнее изменение этой страницы: 2016-04-19; просмотров: 570; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.135.208.236 (0.007 с.) |

(

( ) или

) или  (

( ), первый из которых передает содержимое адресуемого счетчика /или регистра ПИТ на шину данных, а второй загружает байт с этой шины в адресуемый счетчик или регистр. Сигнал

), первый из которых передает содержимое адресуемого счетчика /или регистра ПИТ на шину данных, а второй загружает байт с этой шины в адресуемый счетчик или регистр. Сигнал  разрешает или запрещает работу ПИТ. Сигналы младших линий адреса А1 и A0 выбирают конкретный счетчик CTRi комбинациями 00, 01 и 10, или регистр управляющего слова (комбинацией 11).

разрешает или запрещает работу ПИТ. Сигналы младших линий адреса А1 и A0 выбирают конкретный счетчик CTRi комбинациями 00, 01 и 10, или регистр управляющего слова (комбинацией 11).