Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Режим выполнения основной программыСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

При выполнении основной программы процессор выбирает из ОЗУ очередную команду программы и выполняет соответствующую операцию. Команда представляет собой многоразрядное двоичное число (Рисунок 6), которое состоит из двух частей (полей) - кода операции (КОП) и кода адресации операндов (КАД).

Рисунок 6 - Формат типовой команды микропроцессора

Код операции КОП задает вид операции, выполняемой данной командой, а код адресации КАД определяет выбор операндов (способ адресации), над которыми производится заданная операция. В зависимости от типа микропроцессора команда может содержать различное число разрядов (байтов). Например, команды процессоров Pentium содержат от 1 до 15 байтов, а большинство процессоров с RISC-архитектурой использует фиксированный 4-байтный формат для любых команд. Для хранения адреса очередной команды служит специальный регистр процессора - программный счетчик PC (Program Counter), содержимое которого автоматически увеличивается на 1 после выборки следующего байта команды. Принятая из ОЗУ команда поступает в регистр команд, входящий в состав УУ процессора. Затем производится дешифрация команды, в процессе которой определяется вид выполняемой операции (расшифровка КОП) и формируется адрес необходимых операндов (расшифровка КАД). В соответствии с кодом поступившей команды УУ процессора генерирует последовательность микрокоманд, обеспечивающих выполнение заданной операции. Каждая микрокоманда выполняется в течение одного машинного такта - периода тактовых импульсов, задающих рабочую частоту всех внутренних узлов и блоков микропроцессора. Для выполнения каждой поступившей команды требуется определенное количество командных циклов и тактов. Командным циклом называется промежуток времени, требуемый для выполнения обращения к ОЗУ или внешнему устройству с помощью системной шины. Обычно реализация такого цикла занимает от 2 до 4 системных тактов (периодов синхросигналов шины), которые требуются для установки требуемого адреса, выдачи сигналов, определяющих вид цикла - чтение или запись, получения сигнала готовности к обмену (от памяти или внешних устройств) и собственно передачи данных или команд. Машинным (процессорным) тактом в микропроцессорных системах является длительность периода тактовых сигналов Tt, которая задается тактовой частотой микропроцессора Ft.При выполнении операций, не требующих обращений к системной шине, эта частота определяет производительность микропроцессора. Текущее состояние процессора при выполнении программы определяется содержимым регистра состояния SR (State Register, в микропроцессорах Pentium данный регистр называется EFLAGS). Этот регистр содержит биты управления, задающие режим работы процессора, и биты признаков (флаги), указывающие характеристики результата выполненной операции: N - признак знак (старший бит результата), N = 0 - при положительном результате, N = 1 -при отрицательном результате; С - признак перенос, С = 1, если при выполнении операции образовался перенос из старшего разряда результата; V - признак переполнения, V = 1, если при выполнении операций над числами со знаком произошло переполнение разрядной сетки процессора; Z - признак нуля, Z = 1, если результат операции равен нулю. Некоторые микропроцессоры фиксируют также другие виды признаков: признак четности результата, признак переноса между тетрадами младшего байта. Специальные виды признаков устанавливаются по результатам операций над числами, представленными в формате с «плавающей точкой».

Режим вызова программы Обращение к подпрограмме реализуется при поступлении в микропроцессор специальной команды CALL (в некоторых процессорах эта команда имеет мнемоническое обозначение JSR - Jump-to-SubRoutine), которая указывает адрес первой команды вызываемой подпрограммы. Этот адрес загружается в PC, обеспечивая в следующем командном цикле выборку первой команды подпрограммы. Предварительно выполняется процедура сохранения в специальном регистре или ячейке памяти текущего содержимого PC, где хранится адрес следующей команды основной программы, чтобы обеспечить возвращение к ней после выполнения подпрограммы. Возврат к основной программе реализуется при поступлении команды RETURN (мнемоническое обозначение RET), завершающей подпрограмму. По этой команде сохранявшееся содержимое PC снова загружается в программный счетчик, обеспечивая выполнение команды, которая в исходной программе следовала за командой CALL.

Рисунок 7 - Последовательный вызов (вложение) подпрограмм

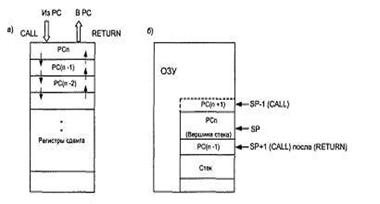

Для реализации этой процедуры используется стек - специальная память магазинного типа, работающая по принципу «последний пришел - первый ушел» (стек типа LIFO -«Last In-First Out»). Существуют различные варианты реализации стека. Регистровый стек (Рисунок 5) реализуется с помощью реверсивных сдвиговых регистров. Каждая команда CALL вызывает ввод в стек очередного содержимого PC. По команде RETURN направление сдвига изменяется и производится извлечение из стека последнего поступившего содержимого PC. Таким образом, обеспечивается выполнение вложенных подпрограмм. Возможное число вложенных подпрограмм определяется глубиной стека, т.е. разрядностью используемых регистров сдвига. Если число вложений превышает глубину стека, первые из введенных в стек значений PC теряются, т.е. возврат к основной программе не будет обеспечен. Поэтому при использовании регистрового стека необходим строгий контроль за числом вложений. Такая реализация стека применяется в системах, решающих задачи с ограниченным числом вложенных подпрограмм (обычно не более 10-20). Значительно более широкие возможности вложения подпрограмм обеспечивает реализация стека в ОЗУ (Рисунок 8). В этом случае часть ОЗУ выделяется для работы в качестве стека. Адресация к ячейкам стека производится с помощью специального регистра - указателя стека SP (Stack Pointer), который вводится в состав УУ процессора. Регистр SP содержит адрес верхней заполненной ячейки стека, в которой хранится значение PC, записанное при выполнении команды CALL.

Рисунок 8 - Варианты реализации стека: регистровый стек (а) и стек, реализуемый в ОЗУ (б)

При поступлении новой команды CALL (операция PUSH) содержимое SP автоматически уменьшается на 1, адресуя следующую, еще незаполненную ячейку стека. Полученный адрес SP-1 выдается на шину А, а на шину D поступает содержимое PC, которое должно сохраняться в стеке. Таким образом, производится последовательное заполнение ячеек стека «снизу-вверх», при этом SP всегда адресует вершину стека. По команде RETURN (операция POP) текущее содержимое SP выдается на шину А, и по шине D производится считывание с вершины стека последнего записанного значения PC. После этого содержимое SP увеличивается на 1, адресуя предыдущее значение PC, хранящееся в стеке. Так как ОЗУ обычно имеет значительный объем, то для размещения стека можно выделить достаточно большое количество ячеек памяти, обеспечивая необходимый уровень вложения подпрограмм.

|

||||

|

Последнее изменение этой страницы: 2016-04-19; просмотров: 570; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.119.134.196 (0.006 с.) |

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм, т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (Рисунок 7). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.

Особенность этой процедуры состоит в том, что большинство микропроцессоров обеспечивают возможности вложения подпрограмм, т.е. реализуют при выполнении подпрограммы вызов новой подпрограммы с последующим возвращением к предыдущей подпрограмме (Рисунок 7). При вложении нескольких подпрограмм требуется сохранение нескольких промежуточных значений содержимого PC и последовательная загрузка этих значений в PC при возврате к предыдущим подпрограммам и к основной программе.