Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Триггер Т-типа (Счётный триггер)Содержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

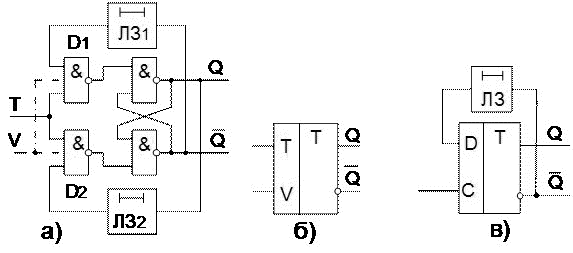

Т-триггер или счётный триггер, имеет один счётный вход Т и два выхода (Рисунок 50,а). Функционирование триггера определяется уравнением:

Из уравнения следует, что Т-триггер каждый раз изменяет своё состояние на противоположное с приходом на счётный вход Т очередного тактирующего импульса длительностью tи. Этому способствует наличие перекрёстных обратных связей с выходов триггера на входы элементов D1 и D2. Для надёжной работы триггера, с целью сохранения информации о предыдущем состоянии триггера в момент его переключения, в схему вводят элементы задержки, имеющие время задержки tз > tи.

Рисунок 50 Т-триггеры: — а) структурная схема, б) УГО TV-триггера, в) Т-триггер на основе D-триггера.

По окончании действия тактирующего импульса. Пусть в исходном состоянии Q=1. Сигнал T=1 откроет элемент D2, так как на втором входе D2 имеется сигнал лог «1» с выхода Q, а элемент D1 будет закрыт. Триггер переходит в состояние Q=0. Вентиль D2 остаётся открытым в течение времени tи, т.к. сигнал Q=1 будет задержан ЛЗ1 на время τ з > tи. В то же время сигнал По окончании действия тактирующего импульса элементы D1 и D2 закроются, так как потенциал входа T=0. После чего на вход элемента D1 через ЛЗ2 поступит сигнал Роль ЛЗ в Т-триггерах выполняют логические элементы с большим временем задержки tзд.р или специальные компоненты электронных схем, например, диоды с накоплением заряда. Кроме счётного входа Т-триггер может иметь вход разрешения V (Рисунок 50,б). Сигнал на этом входе разрешает (при V=1) или запрещает (при V=0) срабатывание триггера от поступающих на вход T сигналов. Т-триггеры, имеющие дополнительный вход V, называются TV-триггерами. Наличие входа V позволяет организовать счёт в заданном временном интервале, что существенно расширяет функциональные возможности Т-триггера. Счётный Т-триггер может быть построен на основе D-триггера, соединив инверсный выход D-триггера со входом D, как показано на рисунке 50,в. В такой схеме каждый переход 1/0 на входе C будет приводить к переходу триггера в противоположное состояние. Например, если Qn =1, то Таким образом, из рассмотрения принципа работы Т-триггера следует, что при Т=1 спадающий фронт сигнала на входе C переводит триггер в противоположное состояние. Частота изменения потенциала на выходе Т-триггера в два раза меньше частоты импульсов на входе C. Это свойство Т-триггеров позволяет строить на их основе двоичные счётчики. Поэтому эти триггеры и называют счётными. 5.1.4 JK-триггеры JK-триггер — это схема с двумя устойчивыми выходными состояниями и двумя входами J и K (Рисунок 51.а). Подобно RS-триггеру, в JK-триггере входы J и K — это входы установки выхода Q триггера в состояние 1 или 0. Однако, в отличие от RS-триггера, в JK-триггере наличие J=K=1 приводит к переходу выхода Q триггера в противоположное состояние. Условие функционирования JK-триггера описывается функцией:

Рисунок 51 JK-триггеры: а) асинхронные; б) тактируемые фронтом.

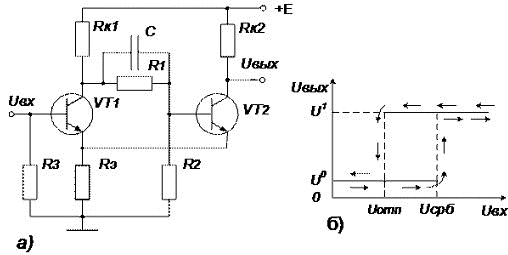

Триггер JK-типа называют универсальным потому, что на его основе с помощью несложных коммутационных преобразований можно получить RS и Т-триггеры, а если между входами J и K включить инвертор, то получится схема D-триггера. Недостатком этой схемы является зависимость работы схемы от длительности тактового импульса. Импульс должен быть коротким и должен закончиться до завершения процесса переключения триггера. Для ослабления требования к длительности тактового импульса в цепи обратных связей можно включить элементы задержки, как показано на рисунке 51,а пунктиром. Однако этот путь не всегда является целесообразным. Разработаны и применяются в основном в интегральном исполнении JK-триггеры, тактируемые фронтом тактовых импульсов, которые не чувствительны к длительности тактовых импульсов. JK-триггеры, тактируемые фронтом, строятся по схеме MS (master-slave то есть мастер-помощник). В схеме имеется два триггера: основной D1…D4, помощник D5…D8 и цепь, разделяющая их — D9 (Рисунок 51,б). Триггер работает следующим образом. Пусть в исходном состоянии Q=0, а Пусть J=1, тогда с приходом тактового импульса C=1, D1 откроется, а D2 останется закрытым. Элементы D5 и D6 закроются сигналом Несмотря на то, что на одном из входов D5 действует сигнал «1», а на одном из входов D6 — «0», они не изменят состояние вспомогательного триггера, так как на других входах элементов D5 и D6 действует сигнал лог. «0» с инвертора D9. По окончании действия тактового импульса, появится сигнал лог. «1» на вторых входах вентилей D5, D6, а вентили D1 и D2 закроются. Так как основной триггер находится в состоянии «1», то откроется D5 и информация запишется во вспомогательный триггер (Q=1, Совершенно аналогично сигнал «1», поданный на вход K, установит триггер в состояние «0». Таким образом, в триггере данного типа изменение выходного сигнала происходит только в моменты, когда потенциал «C» переходит из «1» в «0». Поэтому говорят, что эти триггеры тактируются срезом (или фронтом) в отличие от триггеров, тактируемых потенциалом. Условное графическое обозначение триггера приведено на рисунке 51,в. Если соединить вместе входы J и K, то JK-триггер превратится в Т-триггер. Пусть триггер находится в исходном состоянии ( 5.1.5 Несимметричные триггеры Несимметричный триггер (триггер Шмита) имеет два устойчивых состояния, однако, в отличие от симметричного триггера, нахождение его в том или ином устойчивом состоянии зависит от величины входного сигнала. Несимметричный триггер на дискретных элементах состоит из двух транзисторов, в эмиттерную цепь которых включён резистор RЭ (Рисунок 52). При таком включении напряжение на базе транзистора VT1 зависит от значения коллекторного тока IК2 транзистора VT2. В свою очередь, базовая цепь VT2 через делитель R1/R2 соединена с коллекторной цепью транзистора VT1. Эти цепи создают замкнутую петлю положительной обратной связи, которая, как и в симметричном триггере, обеспечивает быстрое переключение триггера Шмита из одного устойчивого состояния в другое, когда оба транзистора работают в активном режиме.

Рисунок 52 Триггер Шмита на транзисторах

В отсутствие входного напряжения (Uвх =0) триггер находится в устойчивом состоянии. При этом транзистор VT2 открыт и насыщен, так как на его базу через резисторы Rк1, R1 подаётся положительное напряжение, а транзистор VT1 закрыт. За счёт протекающего коллекторного тока IК2 = E /(RК2 + RЭ) на резисторе RЭ создаётся падение напряжения и на базе VT1 относительно эмиттера действует запирающее напряжение UБЭ1=–RЭIК2. В таком состоянии триггера напряжение на выходе UВЫХ=U 0= RЭIК2 + UКЭнас. Если увеличивать входное напряжение, то пока Uвх < RЭIК2 + UБЭнас триггер находится в исходном состоянии. Когда Uвх достигнет напряжения срабатывания UСРБ=RЭI2+UБЭнас, открывается транзистор VT1, снижается его коллекторный потенциал, а следовательно и базовый ток VT2. В результате транзистор VT2 переходит в активный режим и в схеме развивается регенеративный процесс, приводящий к быстрому закрыванию транзистора VT2 и отпиранию VT1.

Параметры схемы несимметричного триггера рассчитываются таким образом, чтобы при уменьшении входного напряжения транзистор VT2 открывался и триггер переходил в исходное устойчивое состояние при напряжении отпускания UВХ=UОТП < UСРБ. При таком условии амплитудная передаточная характеристика имеет петлю гистерезиса (Рисунок 52,б). Для открывания транзистора VT2 и перехода триггера в исходное устойчивое состояние необходимо уменьшить Uвх, чтобы транзистор VT1 перешёл из режима насыщения в активный режим работы. Только при этом условии напряжение на базе транзистора VT2 увеличится до UБЭнас.

Из соотношений (5.1) и (5.2) следует, что для обеспечения принятого условия UСРБ > UОТП, необходимо, чтобы RК1 > RК2. Конденсатор C1 на устойчивые состояния триггера влияния не оказывает. Он выполняет функцию форсирующего конденсатора во время во время включения и выключения транзистора VT2 и тем самым способствует сокращению времени переключения триггера из одного устойчивого состояния в другое. Несимметричный триггер может быть реализован на логических элементах. Для этого достаточно включить последовательно чётное число элементов НЕ и выход этой цепочки соединить со входом цепью обратной связи, образуемой резисторами R1 и R2 (Рисунок 53,а). В отсутствие входного сигнала (Uвх =0) напряжение на выходе (Uвых =0). Если пренебречь входным током ЛЭ, то при Uвх >0 напряжение на входе D1 UВХ = UВХ–R 1 I, где I =(UВХ 1– UВЫХ)/ R 2. Таким образом, UВХ 1 = UВХ + (UВЫХ – UВХ 1) R 1/ R 2 (5.3)

Рисунок 53 Триггер Шмита на логических элементах

С ростом Uвх повышается напряжение Uвх1, но пока Uвх1 < Uпор логические элементы остаются в исходном состоянии и на выходе сохраняется сигнал U 0. Когда Uвх1 = Uпор, происходит переключение логических элементов и на выходе возникает сигнал UВЫХ=U ¹. В результате схема переходит в другое устойчивое состояние. Напряжение срабатывания можно определить из приведённого выше выражения (5.3), если принять Uвх1=Uпор, UВЫХ=U ¹, Uвх=Uсрб: UСРБ = UПОР + (UПОР – U 0) R 1/ R 2 (5.4) Естественно, что при Uвх1 > Uсрб на выходе схемы сохраняется состояние лог. «1». При уменьшении Uвх триггер переходит в исходное состояние, когда Uвх=Uотп. Значение Uотп определяется из соотношения (5.3), если положить Uвх1=Uпор, Uвых=U 1, Uвх=Uотп. UОТП= UПОР + (U 1 – UПОР) R 1/ R 2 (5.5) Из соотношений (5.4) и (5.5) следует, что Uсрб > Uотп и, таким образом, амплитудная передаточная характеристика несимметричного триггера на ЛЭ имеет петлю гистерезиса. Вычитая (5.5) из (5.4), получаем UСРБ – UОТП = (U 1 – U 0) R 1/ R 2 Откуда видно, ширина петли гистерезиса пропорциональна логическому перепаду ∆ UЛ. Несимметричные триггеры применяют в качестве формирователей импульсов прямоугольной формы при воздействии на вход, например, синусоидального напряжения (Рисунок 53,б). Поскольку выходное напряжение резко возрастает при UВХ = UСРБ, то такие триггеры используют и в качестве компаратора напряжения — устройства, которое позволяет зафиксировать момент достижения сигналом некоторого заданного уровня. Регистры Регистры — это функциональные узлы на основе триггеров, предназначенные для приёма, кратковременного хранения (на один или несколько циклов работы данного устройства), передачи и преобразования многоразрядной цифровой информации. В зависимости от способа записи информации (кода числа) различают параллельные, последовательные и параллельно — последовательные регистры.

|

||||

|

Последнее изменение этой страницы: 2016-04-08; просмотров: 2030; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.144.255.116 (0.011 с.) |

не попадёт на вентиль D1 из-за временной задержки ЛЗ2. При отсутствии элементов задержки возможно неоднократное переключение триггера при условии, если длительность импульса tи значительно превышает время переключения триггера.

не попадёт на вентиль D1 из-за временной задержки ЛЗ2. При отсутствии элементов задержки возможно неоднократное переключение триггера при условии, если длительность импульса tи значительно превышает время переключения триггера. , и поэтому очередной тактовый импульс переведёт триггер в новое состояние, т.е. установит Qn +1= Dn =0. Для правильной работы Т-триггера тактовый импульс должен быть коротким, а наличие элемента задержки ЛЗ ослабляет требование к длительности тактового импульса.

, и поэтому очередной тактовый импульс переведёт триггер в новое состояние, т.е. установит Qn +1= Dn =0. Для правильной работы Т-триггера тактовый импульс должен быть коротким, а наличие элемента задержки ЛЗ ослабляет требование к длительности тактового импульса.

с выхода элемента D9. Сигнал лог. «0», снимаемый с открытого вентиля D1, записывает в основной триггер информацию, устанавливая его в состояние «1» (P =1,

с выхода элемента D9. Сигнал лог. «0», снимаемый с открытого вентиля D1, записывает в основной триггер информацию, устанавливая его в состояние «1» (P =1,

).

). ). При подаче J=K=1 и C=1, вентиль D1 будет закрыт сигналом «0» с выхода

). При подаче J=K=1 и C=1, вентиль D1 будет закрыт сигналом «0» с выхода  . При этом выходной потенциал Q=0 блокирует вентиль D2. Поэтому следующая комбинация J=K=1 и C=1 переводит триггер в состояние Q=1 и т.д.

. При этом выходной потенциал Q=0 блокирует вентиль D2. Поэтому следующая комбинация J=K=1 и C=1 переводит триггер в состояние Q=1 и т.д.

(5.1)

(5.1) (5.2)

(5.2)