Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Симетричний триггер з зовнішнім джерелом напруги зміщення.Содержание книги

Поиск на нашем сайте

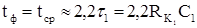

Прискорюючі конденсатори С шунтують резистори R і пезначені для форсування процесів перемикання триггера. Триггер має два стани стійкої рівноваги: VT1 в насиченні, VT2 — в відсічці і навпаки. Припустимо, що VT1 в насиченні, а VT2 — в відсічці, причому закритий стан VT2 підтримується +Ед, а відкритий стан VT1 — підбором Після приходу на базу VT1 запускаючого імпульсу позитивної полярності починається перехід триггера в інший стійкий стан. Цей процес можна розбити на 4 етапи: Перший етап закінчується виходом VT1 з насичення на межу активної області. Другий етап. Струм Ці два етапи складають стадію підготовки триггера. Тепер обидва транзистора знаходяться в активному режимі, тобто (1) З цього моменту починається третій етап — етап регенерації, на протязі якого відбувається лавиноподібна модифікація струму і напруги. Цей процес закінчується тим, що VT1 переходить в відсічку, і припиняється дія позитивного зворотного зв'язку, тобто умови (1) не виконуються. На четвертому етапі VT2 насичується і встановлюються коллекторні напруги: на VT1 При цьому величина оптимальної ємності:

В тих випадках, коли застосування додаткового джерела небажано, використають триггери з автоматичним зміщенням.

Недоліком цього триггера є зменшення амлітуди вихідного імпульсу на величину Uе і наявність двох додаткових елементів Rе і Се. Застосовується для боротьби з дребезгом контактів.

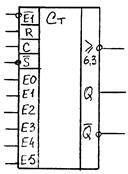

К555ТР2 — 4 штуки RS К561ТР2 — 4 штуки RS На або-не.

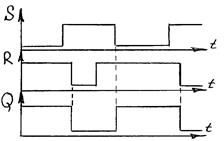

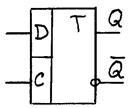

D-триггер. Найбільш часто в цифрових мікросхемах, а також в імпульсних приладах застосовують триггери з одним входом даних — D-триггери.

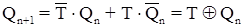

Т - триггер.

Це триггер з одним входом, що змінює свій стан по прибутті кожного імпульсу. Його ще називають лічильним. Характеристичне рівняння.

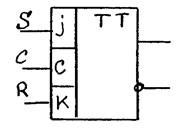

Ідеальний дільник на 2. Перемикається по задньому фронту, т.я. він двоступеневий (тому позначається ТТ). Мікросхемного виконання ні. JK - триггер.

Режим работи Вход Вихід

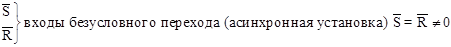

Асинхронна установка H B Асинхронне скиданн B H Невизначеність H H Перемикання B B B B Загрузка 0 (скидання) B B H B H B Загрузка 1 (установка) B B B H B H Зберігання (без змін) B B H H q

Універсальність JK-триггера.

Лічильники. Лічильниками називають послідовністні цифрові пристрої, призначені для підрахунку і запам’ятовування числа імпульсів, поданих на лічильний вхід. Окрім лічильного входу можуть мати входи для асинхронної або синхронної установки початкових станів. По характеру модифікації станів розрізняють: підсумовуючі, віднімаючі і реверсивні. По засобу організації переносу між розрядами вони діляться на лічильники з послідовним, наскрізним і паралельним переносом. Лічильники з послідовним і наскрізним переносом називають асинхронними, а з паралельним переносом — синхронними. По кількості різноманітних станів виходу діляться на двійкові, десяткові, двійково-десяткові. Основними технічними параметрами лічильників є коефіцієнт перелічення Ксч і швидкодія. Коефіцієнт Ксч являє собою число різноманітних сталих станів, тобто максимальне число імпульсів, що лічильник може прорахувати і запам'ятати без повторення станів. Швидкодія лічильника визначається максимальною частотою надходження імпульсів, що реєструються лічильником без збоїв. Асинхронні лічильники.

В асинхронних лічильниках буде відсутня загальна для всіх розрядів синхронізація і перехід розрядів в нові стани відбувається послідовно, розряд за розрядом (доміно).

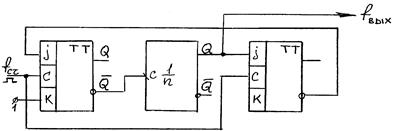

Лічильні входи JK-триггерів з'єднують з прямими виходами попередніх, а D-триггерами — з інверсними. Це пов’язано з тим, що D-триггер зпрацьовує по фронту, а JK - Триггер — по спаду вхідних імпульсів. По такому принципу зроблені лічильники: 155ІЕ2 — десятковий, 155ІЕ5 — двійковий. Основне достоїнство послідовного лічильника — мінімальні затрати мікросхем і мінімум електричних зв'язків. Головний недолік — низька швидкодія (чим більше Ксч). Дільники частоти відрізняються від лічильників тим, що в них використовується тільки один вихід — вихід останнього триггера. Таким чином, n-разрядний двійковий лічильник завжди можна розглядати як дільник на Частота на виході такого дільника рівна: fвых=fсч / Ксч Ксч — будь-яке ціле число. Ксч, яке вимагається, одержують введенням в лічильники зворотних зв'язків. Загальний принцип побудови дільників (лічильників) з непарним Ксч має вид.

Де N — число триггерів. Якщо між вхідним і вихідним триггерами включений дільник частоти на будь-яке натуральне число n, то така схема забезпечує ділення частоти на Ксч=

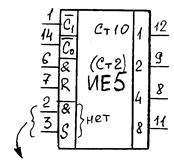

155ІЕ8 — програмуєть лічильник з входом для перемикання коефіцієнту перелічення.

На простих D-триггерах (і будь-яких) змінний коефіцієнт ділення можна зробити за допомогою зворотних зв'язків. Тепер розглянемо реверсивні лічильники. 155ІЕ6 — двійково-десятковий реверсивний лічильник.

Синхронні лічильники.

До синхронних або паралельних лічильників відносять лічильники, в яких перемикання розрядів відбувається одночасно, незалежно від віддаленості розряду від лічильного входу. Завдяки цьому вдається отримати мінімальний час установки нового стану, як ІЕ10. Одночасне переключення досягається подачею на всі триггери синхронизуючих імпульсов, що позитивним або негативним фронтом викликають переключення триггеров у відповідності з логікою роботи лічильника. К555ИЕ18, 531ІЕ16. Регістри.

Регістри — це послідовнісні пристрої, призначені для прийому, зберігання, зрушення і передачі двійкових чисел. Основне функціональне призначення регістрів — оперативна пам'ять для багаторозрядних двійковихих чисел. В залежності від способу прийому і передачі інформації розрізняють паралельні, послідовні (регістри зсуву), послідовно-паралельні, паралельно-послідовні і універсальні. В паралельних регістрах або регістрах пам'яті введення/виведення всіх розрядів числа виробляється водночас, за один такт. Для побудови n-разрядного регістру паматі вимагається n триггерів. Паралельні регістри служать основним функціональним елементом для побудови оперативних запам’ятовуючих приладів. В послідовних регістрах введення/виведення інформації здійснюється через один інформаційний вхід і один вихід порозрядно зі зсувом числа. Тому їх називають зсувними. За один такт вводима або виводима інформація зсувається на один розряд праворуч або ліворуч. Зсуваючі регістри, що зсувають і праворуч і ліворуч, називають реверсивними.

Приклад реверсивного регістру — 155ІР13 (8 розрядів). Послідовно-паралельні регістри виконують перетворення послідовного коду в паралельний. 155ІР8 (8 розрядів). Запам’ятовуючі пристрої.

Запам’ятовуючі пристрої (ЗП) служать для зберігання інформації і обміну нею з іншими частинами ЕОМ або мікропроцессорних систем. По функціональному призначенню ЗП діляться на зовнішні, буферні і внутрішні. Зовнішні ЗП служать для зберігання більшого обсягу інформації і програмного забезпечення системи. В них використовуються ЗП з прямим доступом (магнітні диски) і ЗП з послідовним доступом (магнітні стрічки). Буферні ЗП служать для проміжного зберігання даних при обміні між зовнішньою і внутрішньою пам'яттю. Внутрішні ЗП по функціям,що виконуються діляться на оперативні і постійні. Оперативні ЗП (ОЗП) виконують запис, зберігання і зчитування довільної двійкової інформації, забезпечують зберігання програм для поточної обробки інформації і масивів даних,що обробляються. Постійні ЗП (ПЗП) здійснюють зберігання і видавання постійно записаної інформації, вміст якої не змінюється під час роботи системи. Діляться на: ПЗП, ППЗП — перепрограмуючі і РПЗП — репрограмуючі. ПЗП.

1. Масочно-програмуючі ПЗП (ПЗП) випускають по різноманітним технологіям (ТТЛ, МДП, КМОП). Інформація заноситься в них в процесі виготовлення і не може бути згодом змінена. Цей вид ПЗП вигідно застосовувати при багатосерійном виробництві (більша вартість фотошаблонів). Звичайно в них заноситься стандартна інформація: генератори російських, латинських символів і інших алфавітів, редактори текстів, арифметичні знаки і цифри і ін. К155РЕ21 — 256 КР568РЕ3 — 16к 2. Більш зручні електричні програмуючі ПЗП. Вони дадуть можливість тільки однократного запису потрібної інформації самим споживачем шляхом руйнування запам’ятовуючих елементів напругою або струмом. Запам’ятовуючими елементами можуть бути спеціальні провідникові перемички або p-n переходи. Застосовувати однопрограмуючі ПЗП в обчислювальних системах доцільно в невеликій кількості. Звичайно всі ППЗП мають байтову (8 розрядів) організацію. К556РТ1 — 256 К556РТ18 — 2к 3. Найбільш універсальними є перепрограмуючі (репрограмуючі) ПЗП. Виробляють на основі МОП-СТРУКТУР і ЛІЗМОП (лавинна інжекція зарядів). Особливий інтерес представляють ЗП, виконані по технології МНОП (транзистори з комбінованою нітридно-оксидною ізоляцією) і ЛІЗМОП. Вони дозволяють зберігати інформацію при відключеному живленні до 100 000 годин. Крім того, ємність таких ЗП досягає 256к (32к Розрізняють РПЗП з ультрафиолетовим і електричним витиранням. В УФ ПЗП кожний біт інформації відображається станом відповідного МОП транзистора з плаваючим затвором. Затвори транзисторів при програмуванні заряжаються лавинною інжекцією, тобто зворотнім пробоєм навколишнього затвор ізоляційного шару під дією імпульсу напруги 20 Для витирання інформації кристал БІС в продовж 30 РПЗП з електричним витиранням дозволяє робити як запис, так і стирання інформації за допомогою електричних сигналів. Число циклів до КМ558РР3 64к (8к ОЗП.

По способу зберігання інформації ОЗП ділять на статичні і динамічні. Запам’ятовуючі елементи статичних ЗП являють собою бістабільні елементи (триггери) і забезпечують зчитування інформації без її руйнування. В динамічних ЗП для зберігання інформації використовуються реактивні елементи (конденсатори), що вимагає періодичного відновлення (регенерації) інформації в процесі зберігання. При регенерації виробляється перезапис кожного зберігаємого б, що міститься в пам'яті (3% від t). Основними параметрами ЗП є: інформаційна ємність М і швидкодія. Інформаційна ємність характеризує кількість інформації, що може зберігається в запам’ятовуючому елементі на кристалі і визначається в бітах або кількості слів N з вказівкою їх розрядності n. M= n Де n — розрядність слова (n=0, 1.2, 3…); N= 1 КР565РУ1 К — загальне застосування. Р — пластмасовий корпус. 565 — серія мікросхеми. РУ — ОЗП (RAM). 565РУ1 — 1 РВ — матриця ПЗП. РМ — матриця ОЗП. РЕ — ПЗП (ROM) заказна. 155РЕ3 — 8 РТ — ППЗП (PROM). 556РТ4 — 4 РР — РПЗП (EE PROM) — з електричним витиранням. РФ — РПЗУФ (EPROM) — з ультрафіолетовим витиранням. 573РФ5 — 4 По структурі напівпровідникові ОЗП, ППЗП і РПЗП складаються з наступних типових вузлів:

RAS — строб адреси рядка. CAS — строб адреси стовбчика. CS — вибір мікросхеми. WR/RD — запис-зчитування. D1 — вхідні дані. D0 — вихідні дані. Нагромаджувач являє собою матрицю запам’ятовуючих елементів, об'єднаних в рядки і стовбчики через розв’язуючі ключові елементи, зв'язані дешифраторами. В статичних ОЗП — це триггерні елементи, а в динамічних — ключовий транзистор і ємність зберігання інформації. В нагромаджувачах ПЗП використовуються транзистори, під’єднані відповідним чином до дешифратора рядків і стовбчиків

Приклад. 155РУ5 — матричний ОЗП з організацією 256 слів по 1 біту. Матриця має 16 рядів і 16 колонок запам’ятовуючих осередків.

У випадку необхідності мікросхеми ЗП можна об'єднувати, увінчуючи завдяки цьому ємність пам'яті. Для цього вони мають спеціальний вивод

З двох мікросхем ємністю по 16 чотирьохрозрядних слів ми отримали ємність — 32 чотирьохрозрядних слова.

З двох мікросхем ємністю 16 чотирьохрозрядних слів ми отримали ємність пам'яті — 16 восьмирозрядних слів.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-07-11; просмотров: 509; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.21.105.46 (0.011 с.) |

, щоб

, щоб  .

. зменшується далі, викликаючи зменшення коллекторної напруги. Це зменшення напруги через ланцюжок

зменшується далі, викликаючи зменшення коллекторної напруги. Це зменшення напруги через ланцюжок  передається на базу VT2 і компенсує позитивне Ед. Транзистор VT2 переходить з режиму відсічки в активну область.

передається на базу VT2 і компенсує позитивне Ед. Транзистор VT2 переходить з режиму відсічки в активну область. (перший каскад+другий каскад)

(перший каскад+другий каскад) , на VT2 —

, на VT2 —  . Час встановлення

. Час встановлення  залежить від часу заряду

залежить від часу заряду  через

через  і перехід Б-Е VT2. Для його зменшення необхідно зменшувати

і перехід Б-Е VT2. Для його зменшення необхідно зменшувати  .Максимальна швидкодія триггера досягається при виконанні умови:

.Максимальна швидкодія триггера досягається при виконанні умови:

(декілька тисяч пікофарад).

(декілька тисяч пікофарад).

К155ТМ2 — 2 штуки.ТМ5 — 4 штуки.

ТМ8 — 6 штук (для регістрів).

К155ТМ2 — 2 штуки.ТМ5 — 4 штуки.

ТМ8 — 6 штук (для регістрів).

К155ТВ1

К155ТВ1

Триггер двоступінчастий. Кожен з входів J і K забезпечиний тривхідною схемою і.

Триггер двоступінчастий. Кожен з входів J і K забезпечиний тривхідною схемою і.

J K Q

J K Q

q

q Т-триггер

Т-триггер

D-триггер

D-триггер

RS-триггер

RS-триггер

З RST®

З RST®

З DT®

З DT®

.

.

Ксч

Ксч  ,

, Þ n= (Ксч-1)/2. Вимагається на 3, значить n=1.

Þ n= (Ксч-1)/2. Вимагається на 3, значить n=1. : 3

: 3

155ІЕ2

155ІЕ2

.

.

— дозвіл рахунку.

R — загальне скидання.

— дозвіл рахунку.

R — загальне скидання.

155ІЕ2

155ІЕ2

— для нарощування лічильника. Аналогічно працює 155ІЕ7 — двійковий лічильник.

— для нарощування лічильника. Аналогічно працює 155ІЕ7 — двійковий лічильник.

4=1кБіт (ТТЛ). 60нС.

4=1кБіт (ТТЛ). 60нС. 4=1кБіт (ТТЛШ). 90нС.

4=1кБіт (ТТЛШ). 90нС. 60 мин. опромінюють УФ випромінюванням люмінесцентної лампи. Це веде до збільшення струму витоку в ізоляційному шарі і розсмоктуванню зберігаємих на плаваючих затворах зарядів. Число циклів перезапису звичайно 25

60 мин. опромінюють УФ випромінюванням люмінесцентної лампи. Це веде до збільшення струму витоку в ізоляційному шарі і розсмоктуванню зберігаємих на плаваючих затворах зарядів. Число циклів перезапису звичайно 25  раз.

раз. — кількість слів (m=4, 5.6 …).

— кількість слів (m=4, 5.6 …). 4096 б — динамічне.

4096 б — динамічне. 32.

32.

— адреса.

— адреса.

ОЗП

ОЗП

ПЗП ППЗП електр. УФ

Стирання стирання

РПЗП

ПЗП ППЗП електр. УФ

Стирання стирання

РПЗП

— вибір мікросхеми (BK — вибір корпуса). (вибір чіпа).

— вибір мікросхеми (BK — вибір корпуса). (вибір чіпа).