Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

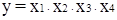

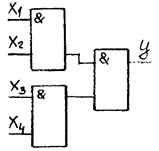

Логічні елементи багатовхідні.Содержание книги Поиск на нашем сайте

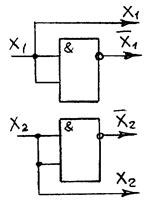

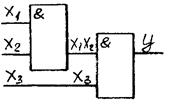

Досі ми розглядаємо тільки логічні елементи з одним або з двома входами. Однак досить часто буває необхідно мати логічні елементи з більшим числом входів. Необхідно мати 3. А є тільки 2.

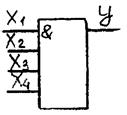

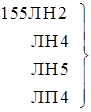

155ЛА1-2 155ЛА4-3 155ЛІ1-4-2і. 155ЛА2 8 і-не. Необхідно мати 4і-не.

Елементна база цифрової техніки.

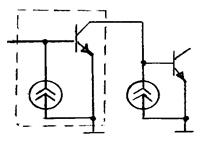

1). Діодно-транзисторна логіка (ДТЛ) — одна з перших розробок цифрових мікросхем на біполярних транзисторах.

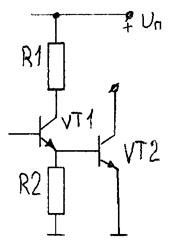

Напруга логічного” 0“ — 1.5 В. Напруга логічної” 1“ — 12В. 2). Транзисторно-транзисторна логіка (ТТЛ) — дуже розповсюджена серія микросхем. Найпростіший елемент ТТЛ одержується з ДТЛ шляхом заміни вхідних діодів і діодів зміщення багатоеміттерним транзистором.

3).Для збільшення швидкодії микросхем ТТЛ були розроблені елементи ТТЛШ. Схемотехнічний принцип побудови такий же, як у ТТЛ.

Крім того, зменшується енергоспоживання. Живлення — 5В. Рівень логічних напруг такий же, як у ТТЛ. Серія 555 — 10МГц. 1533 — 30МГц. 530.531 — 80МГц. 1531 — 150МГц. 4). Елементи еміттерно-зв'язної логіки (ЕЗЛ). Ці елементи засновані на перемикачах струму і відрізняються від інших типів ИМС найбільшою швидкодією і великою потужністю,що споживається. Основою ЕЗЛ елемента є перемикач струму на двох транзисторах з еміттерним зв'язком і двома фазоінверсними виходами.

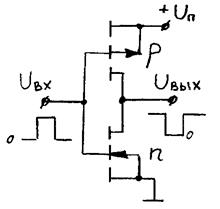

Напруга логічного” 0“ —-1.6 В. Напруга логічної” 1“ —-0.98 В. Нестатком цієї серії є низька поміхочутливість і підвищена чутливість до короткочасних поміх. К500” 0“ —-1.63 В,” 1“ —-0.9 В. 5) Самим низьким рівнем потужності,що споживається відрізняються микросхеми на КМДП транзисторах. Основу таких мікросхем складає ключовий елемент на двох, з'єднаних стоком МДП транзисторах з каналами різної провідності.

Швидкодія — майже сама маленька (3МГц). Найбільш застосовувані серії К176, К561, К564. 6)В останній час розроблені цифрові БИС на базі елементів інтегральної інжекційної логіки — АБО (І Завдяки малій потужності і присутності в схемах І КР582, 584.

Елементи з трьома станами і з відкритим колектором.

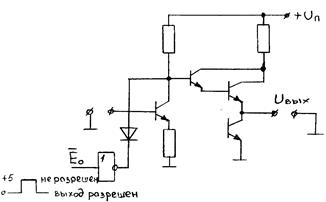

Елементи ТТЛ і КМОП мають двухтактниі вихідні схеми: високий і низький рівень подається на вихід через відкритий біполярний або МОП транзистор. Такі схеми називають активним навантаженням (замість Rк стоїть транзистор). Ці схеми мають низький вихідний опір, малий час перемикання і володіють більш високою поміхостійкістью у порівнянні з одиночним транзистором.

Всі, окрім одного мають разомкнутий стан.

ЛА6 ЛА7 ЛА8

Недоліком ІС з ВК є їхня понижена швидкодія і поміхостійкістьсть у порівнянні з звичайними схемами, що використають активне навантаження. Довга шина може мати значну ємність і, як наслідок, схильність до впливу поміх. Для рішення цієї проблеми застосовують елементи з трьома станами. Це не значить, що ми маємо три рівня напруги. Третій стан (високий імпеданс) — мікросхема відключається від шини. Ці схеми мають окремий запираючий вхід, з допомогою якого вони можуть встановлюватися в третій стан незалежно від того, що сигнали є на вході.

155ЛП8, 155ЛН6

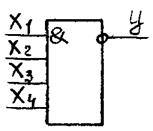

1). Монтажне або (провідне). Це одне з застосуваннь схем з відкритим колектором.

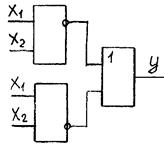

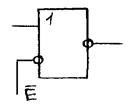

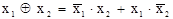

2). Що виключає або (К155ЛП5). Логічний елемент ”що виключає або“ застосовується як суматор по модулю 2 (для двох входів), як пристрій для вироблення паритетного біта, що додається до інформаційного ”слова“ при передачі (або запису) даних, а також для перевірки правильності паритету при відновленні цих даних.

Схема виділення фронту і зрізу.

Звичайно за допомогою диференційного ланцюжка і після цього формують.

Фізичне подання інформації.

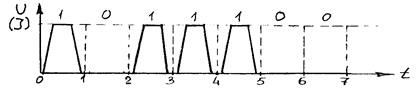

Літери і цифри двійкового алфавіту відображаються фізичними сигналами і можуть приймати два значення, які чітко відрізняються: напруги високого і низького рівня, відсутність і наявність імпульсів струму, позитивний і негативний імпульс струму. Ці два сигнали, які відрізняються позначаються символами ”0“ і ”1“. Застосовуються три способи фізичного подання літер (цифр) двійкового алфавіту: потенційний, імпульсний і динамічний. Потенційне подання.

При потенційному способі двом значенням змінної 0 і 1 відповідають низький і високий рівні напруги. Імпульсное подання.

При імпульсном способі подання одиничне і нульове значення двійкової змінної зображаються наявністю і відсутністю електричного імпульсу в відповідній точці схеми. Динамічне подання.

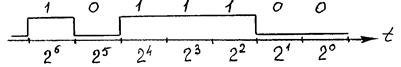

При динамічному способі подання інформації двом можливим значенням змінної відповідає наявність або відсутність серії імпульсов (sin). Для подання і передачі двійкових символів застосовують два способи: послідовний і паралельний. При послідовному способі кожний тимчасовий такт передвизначений для відображення одного розряду. Передається по двом проводам.

При паралельному способі всі розряди передаються по декільком електричним ланцюгам водночас. Кількість ланцюгів рівно кількості розрядів.

Комбінаційні схеми.

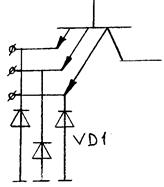

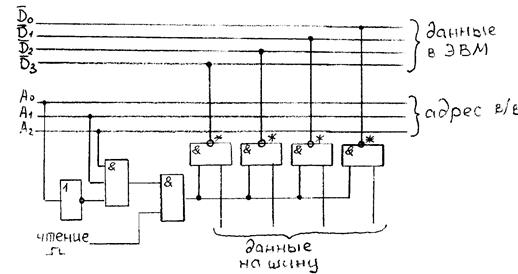

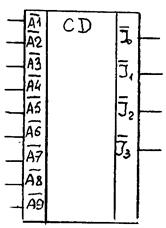

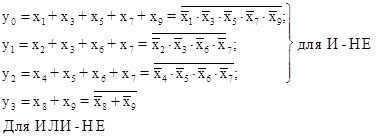

Комбінаційні схеми — це схеми, стан виходів яких однозначно визначається рівнем вхідних сигналів в даний момент часу. Комбінаційні схеми будуються або на основі логічних елементів, або на основі ПЗП, в які записується таблиця перетворення вхідних слів в вихідні. До комбінаційних функціональних вузлів відносяться перетворювачі кодів (шифратори, дешифратори), мультиплексори, демультиплексори, пристрої зсуву чисел, комбінаційні суматори, цифрові компаратори. Шифратор - пристрій, що забезпечує видачу певного коду у відповідь на збудження одного з входів. Шифратори широко використовуються для перетворення десяткових цифр і літерових символів в двійковий код при введенні інформації в ЕОМ з клавiатури. Змінні є незалежними і дозволяють побудувати

Для шифратора:

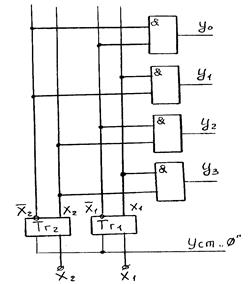

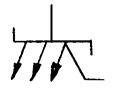

Дешифратори.

Зворотне перетворення двійкового або будь-якого коду в код ”1 з n“ виконують перетворювачі коду що називаються дешифраторами. Використовуються в приладах вводу-виводу інформації з ЕОМ і інших цифрових приладів на друк або дісплей. Дешифратори розділяються: 1) по способу організації дешифрації — на прямокутні (матричні), пірамідальні, ступінчаті; 2) по типу використаних елементів — на діодні, транзисторні, діодно-транзисторні, магнітні; 3) по кількості внутрішніх шин — з повним набором вихідних шин (їх

|

||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-07-11; просмотров: 321; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.219.255.63 (0.008 с.) |

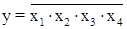

4і-не.

4і-не.

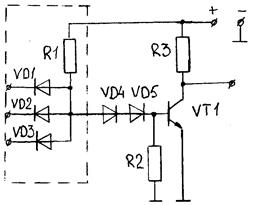

, R1) і послідовно з ним зв'язаного транзисторного ключа. Діодний ключ виконує функцію і, а транзисторний ключ, окрім підсилення — логічну функцію не. Особливістю схеми є використання в базовому ланцюзі діодів VD4, VD5, що служать для підсилення порогової напруги транзисторного ключа і запобігання зпрацювання його від поміх вхідних сигналів на рівні логічного” 0“. 511, 514, 523.

, R1) і послідовно з ним зв'язаного транзисторного ключа. Діодний ключ виконує функцію і, а транзисторний ключ, окрім підсилення — логічну функцію не. Особливістю схеми є використання в базовому ланцюзі діодів VD4, VD5, що служать для підсилення порогової напруги транзисторного ключа і запобігання зпрацювання його від поміх вхідних сигналів на рівні логічного” 0“. 511, 514, 523.

0.4 В. Напруга логічної” 1“ —

0.4 В. Напруга логічної” 1“ —  2.4 В.

Серія 134.158 — 3МГц.

133.155 — 10МГц.

130.131 — 30МГц.

2.4 В.

Серія 134.158 — 3МГц.

133.155 — 10МГц.

130.131 — 30МГц.

Uж.

Виконує операцію не. Потужність, що споживається на декілька порядків менша, ніж в малопотужних ТТЛ. Елементи КМОП (КМДП) відрізняються підвищеною поміхостійкістью, але дуже чутливі до статичної електрики.

Uж.

Виконує операцію не. Потужність, що споживається на декілька порядків менша, ніж в малопотужних ТТЛ. Елементи КМОП (КМДП) відрізняються підвищеною поміхостійкістью, але дуже чутливі до статичної електрики.

Л). Характеризуються надзвичайно низьким енергоспоживанням (менше 1мкВт на елемент).

Л). Характеризуються надзвичайно низьким енергоспоживанням (менше 1мкВт на елемент). Л додаткових резисторов і інших компонентів вдається реалізувати дуже високу щільність розміщення приладів в кристалі. Тому основною галуззю застосування технології І

Л додаткових резисторов і інших компонентів вдається реалізувати дуже високу щільність розміщення приладів в кристалі. Тому основною галуззю застосування технології І  Л є БИС мікропроцесорів, БИС пам'яті і ін. БИС. Основа таких БИС складається з І

Л є БИС мікропроцесорів, БИС пам'яті і ін. БИС. Основа таких БИС складається з І

З відкритим колектором

З відкритим колектором

На 2 входи

На 2 входи

155ЛП2 8-разрядна парність

На 3 входи

155ЛП2 8-разрядна парність

На 3 входи

.

.

вхідних комбінацій. Але якщо накладається обмеження, що забороняє натиск двох і більше клавіш, то залишається тільки 11 вхідних комбінацій. Такий код називається “1 з n“ або унітарним. Якщо обмежень немає, тобто при натисканні декількох клавіш шифратор реагує на старшу (молодшу), то такий шифратор називають пріорітетним.

вхідних комбінацій. Але якщо накладається обмеження, що забороняє натиск двох і більше клавіш, то залишається тільки 11 вхідних комбінацій. Такий код називається “1 з n“ або унітарним. Якщо обмежень немає, тобто при натисканні декількох клавіш шифратор реагує на старшу (молодшу), то такий шифратор називають пріорітетним.

), з неповним набором.

), з неповним набором. Схему прямокутного дешифратора на n входів можна побудувати на основі системи перемикаючих функцій. При цьому прямокутний дешифратор має усього один ступінь дешифрації і число схем збігу І 2n штук.

Схему прямокутного дешифратора на n входів можна побудувати на основі системи перемикаючих функцій. При цьому прямокутний дешифратор має усього один ступінь дешифрації і число схем збігу І 2n штук. x1 x2 y0 y1 y2 y3

0 0 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1

x1 x2 y0 y1 y2 y3

0 0 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1