Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Підсилювачі імпульсних сигналів.Содержание книги Поиск на нашем сайте НЧ корекція.

ВЧ корекція за рахунок від’ємного зворотного зв'язку.

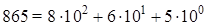

Системи числення і коди, які застосовуються в ЦВК. Під системою числення розуміють засіб виразу і позначки чисел. Узвичаєним зараз є позиційне числення, в якому значення будь-якої цифри визначається не тільки прийнятою конфігурацією її символу, але й розташуванням (позицією), що вона займає в числі. Під основою n позиційного числення розуміють кількість різноманітних символів, що використовуються для виразу числа. Достойністю позиційних систем счислення є компактність запису чисел, істотним недоліком — наявність межрозрядних переносів при виконанні арифметичних дій. Сучасна десяткова позиційна система виникла в Індії не пізніше 5 ст. н. е. Цілі числа в десятковій системі числення подаються в такому вигляді:

Подібний запис можна використати і для цілих чисел:

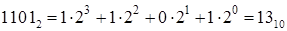

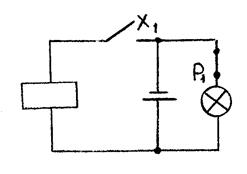

Десяткова система числення заснована на цілих значеннях ступеню числа 10. Вирази Двійкова (бінарна) система заснована на ступені числа 2, тобто вона оперує тільки з двома символами (цифрами): 0 і 1. Двійкова цифра (символ 0 і 1) є одиничною елементарною інформацією, що називається бітому. Двійкова система отримала велике розповсюдження, бо вона має дуже просту технічну реалізацію. Існує багато засобів втілення двох можливих станів в двійковому розряді: замкнутий і разімкнутий контакт реле, триггер, сердечник з ферромагнітного матеріалу з прямокутною петльою гістерезиса, наявність або відсутність імпульсу в лінії. Запис числа в двійковій системі числення (теж позиційнний)

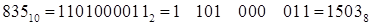

Оскільки двійкові числа мають більшу довжину, для їхнього запису звичайно використовується восьмирічне (з основою 8) або шістнадцятирічне (з основою 16) подання. Щоб записати двійкове число в восьмирічному коді, потрібно усього лише розбити його на групи по три біта, починаючи з молодшого розряду,що значиться, а після цього для кожної групи визначити її восьмирічний еквівалент

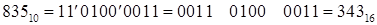

Тут використовуються, звичайно, лише символи від 0 до 7. Для запису двійкового числа в шістнадцятирічному коді його розбивають на групи по 4 біта, кожна з яких може приймати значення від 0 до 15. Оскільки для позначки кожної шістнадцятирічної позиції ми хочемо використати один символ, величини

Шістнадцятирічне подання найкращим чином відповідає байтовій (1 байт рівний 8 бітам) структурі ЕОМ, що часто реалізується у вигляді шістнадцяти або тридцятидвохрозрядних машинних,, слів'’. При цьому кожне слово складається з двох або чотирьох байтів. Двійково-десятковий код — це другий засіб подання чисел. В ньому відбувається двійкове кодування кожної десяткової цифри, що записується у вигляді групи з чотирьох двійкових розрядів. Наприклад:

Двійково-десяткове подання числа не еквівалентне двійковому, що в даному випадку, дорівнює:

Очевидно, що двійково-десяткове кодування не економічне з точки зору використання двійкових розрядів, бо кожна група з 4 біт може видавати числа від 0 до 15, а використовується тільки від 0 до 9. Однак, двійково-десяткове кодування дуже зручне, коли вимагається відтворити число в десятковому виді: кожний двійково-десятковий символ потрібно лише перетворити в відповідне десяткове число, а після цього вивести його на індикацію. Існують спеціальні ВМС для цього. Логічні операції.

Цифрові схеми використають два фізичних стану, майже завжди представлені напругою. Один стан називають станом логічної 1, інший — логічним 0. Якщо більш високій (більш позитивній) напрузі відповідає стан 1, а більш низькій — 0, то це позитивна логіка, якщо навпаки — то негативна логіка. Аналіз логічних ланцюгів виробляється на основі математичного апарату алгебри логіки або булевої алгебри. В булевій алгебрі змінні можуть приймати тільки два значення: 0 і 1. Над змінними можуть проводитися три основні дії: логічне додавання, логічне множення і логічне заперечення, що відповідає логічним функціям або, і, не. Операція логічного додавання (диз’юнкция) позначається знаком (+) або (

Операція логічного множення (кон’юнкция) позначається (

Логічне заперечення (інверсія) позначається рискою над позначкою аргументу.

Аналогія — размикаючий контакт реле.

Характеристики ТТЛ і КМОП. Напруга живлення. Для ТТЛ вимагається +5В Вхід. В стані низького рівня вхід ТТЛ являє собою струмове навантаження для керуючого ним джерела сигналу (1mА). Елементи КМОП не споживають струму по входам. Логічний поріг ТТЛ визначається падінням напруги на двох діодах по відношенню до землі (біля 1.4 В). Для КМОП цей поріг рівний Невикористані входи обох серії необхідно з'єднувати або з землею, або з +Uж. Вихід. В стані низького рівня вихідний каскад ТТЛ веде себе як насичений транзистор, напруга на якому близька до нуля. В стані високого рівня — як повторювач з Uвих Вихід КМОП являє собою відкритий польовий транзистор, підключений до землі або до+Uж. Швидкодія і потужність. Елементи ТТЛ володіють високою швидкодією (до 80 МГЦ), але споживають значну потужність. Схеми КМОП володіють малою швидкодією, але розсіюють малу потужність. Елементи ТТЛ застосовуються в тих випадках, коли істотне значення придається швидкодії, а КМОП — в малопотужних схемах. Схеми ЕСЛ застосовуються (К500) при надвисокій швидкодії.

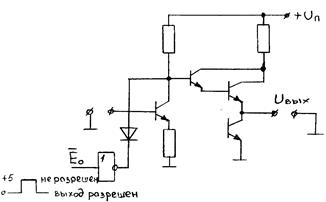

ЛА7 ЛА8

Недоліком ІС з ВК є їхня понижена швидкодія і поміхостійкістьсть у порівнянні з звичайними схемами, що використають активне навантаження. Довга шина може мати значну ємність і, як наслідок, схильність до впливу поміх. Для рішення цієї проблеми застосовують елементи з трьома станами. Це не значить, що ми маємо три рівня напруги. Третій стан (високий імпеданс) — мікросхема відключається від шини. Ці схеми мають окремий запираючий вхід, з допомогою якого вони можуть встановлюватися в третій стан незалежно від того, що сигнали є на вході.

155ЛП8, 155ЛН6

1). Монтажне або (провідне). Це одне з застосуваннь схем з відкритим колектором.

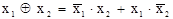

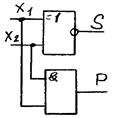

2). Що виключає або (К155ЛП5). Логічний елемент ”що виключає або“ застосовується як суматор по модулю 2 (для двох входів), як пристрій для вироблення паритетного біта, що додається до інформаційного ”слова“ при передачі (або запису) даних, а також для перевірки правильності паритету при відновленні цих даних.

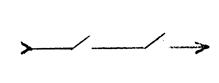

Схема виділення фронту і зрізу.

Звичайно за допомогою диференційного ланцюжка і після цього формують.

Фізичне подання інформації.

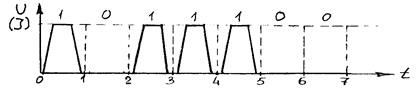

Літери і цифри двійкового алфавіту відображаються фізичними сигналами і можуть приймати два значення, які чітко відрізняються: напруги високого і низького рівня, відсутність і наявність імпульсів струму, позитивний і негативний імпульс струму. Ці два сигнали, які відрізняються позначаються символами ”0“ і ”1“. Застосовуються три способи фізичного подання літер (цифр) двійкового алфавіту: потенційний, імпульсний і динамічний. Потенційне подання.

При потенційному способі двом значенням змінної 0 і 1 відповідають низький і високий рівні напруги. Імпульсное подання.

При імпульсном способі подання одиничне і нульове значення двійкової змінної зображаються наявністю і відсутністю електричного імпульсу в відповідній точці схеми. Динамічне подання.

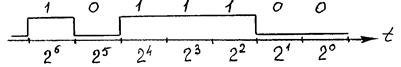

При динамічному способі подання інформації двом можливим значенням змінної відповідає наявність або відсутність серії імпульсов (sin). Для подання і передачі двійкових символів застосовують два способи: послідовний і паралельний. При послідовному способі кожний тимчасовий такт передвизначений для відображення одного розряду. Передається по двом проводам.

При паралельному способі всі розряди передаються по декільком електричним ланцюгам водночас. Кількість ланцюгів рівно кількості розрядів.

Комбінаційні схеми.

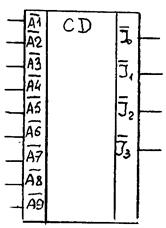

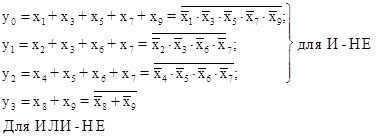

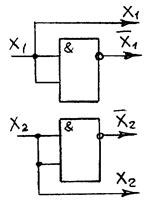

Комбінаційні схеми — це схеми, стан виходів яких однозначно визначається рівнем вхідних сигналів в даний момент часу. Комбінаційні схеми будуються або на основі логічних елементів, або на основі ПЗП, в які записується таблиця перетворення вхідних слів в вихідні. До комбінаційних функціональних вузлів відносяться перетворювачі кодів (шифратори, дешифратори), мультиплексори, демультиплексори, пристрої зсуву чисел, комбінаційні суматори, цифрові компаратори. Шифратор - пристрій, що забезпечує видачу певного коду у відповідь на збудження одного з входів. Шифратори широко використовуються для перетворення десяткових цифр і літерових символів в двійковий код при введенні інформації в ЕОМ з клавiатури. Змінні є незалежними і дозволяють побудувати

Для шифратора:

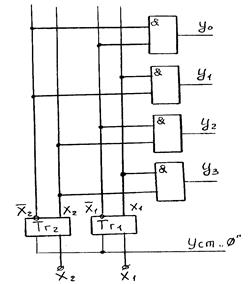

Дешифратори.

Зворотне перетворення двійкового або будь-якого коду в код ”1 з n“ виконують перетворювачі коду що називаються дешифраторами. Використовуються в приладах вводу-виводу інформації з ЕОМ і інших цифрових приладів на друк або дісплей. Дешифратори розділяються: 1) по способу організації дешифрації — на прямокутні (матричні), пірамідальні, ступінчаті; 2) по типу використаних елементів — на діодні, транзисторні, діодно-транзисторні, магнітні; 3) по кількості внутрішніх шин — з повним набором вихідних шин (їх

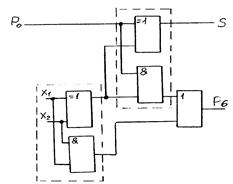

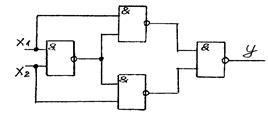

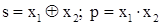

Суматори.

Суматор — це пристрій (вузол), що виконає операцію арифметичного підсумовування двох чисел. Суматор є основним вузлом операційного (арифметичного) пристрою ЕОМ. Суматори можна класифікувати: 1) По кількості входів: 2 входи - напівсуматор; 3 входи — повний суматор; 2) По способу організації процесу підсумовування: комбінаційні і накопичувальні. Комбінаційні. У них сигнали суми і переносу будуть на виході при одночасній подачі кодів доданків. При знятті хоча б одного доданку, сигнал суми на виході зникає. Суматор накопичувального типу будується на основі запам’ятовуючих елементів (триггерів). 3) По способу обробки багаторозрядних чисел: послідовні і паралельні.

Арифметичне підсумовування: 0+0=0; 1+0=1; 0+1=1; 1+1=0 і перенос. Сумматор по модулю 2.

Напівсуматор.

155ИМ1 — 1 розряд. ИМ2 — 2 розряди. ИМ3 — 4 розряди+схема прискореного переносу.

Мультиплексори.

В цифрових приладах часто виникає задача передачі цифрової інформації від m різноманітних приладів до n приймачів через канал загального користування. Для цього на вході каналу встановлюється пристрій, що називається мультиплексором, який згідно коду адреси під’єднується до каналу одного з джерел інформації, а на виході каналу — пристрій демультиплексор, що передає інформацію до приймача зі своєю адресою. Таким чином мультиплексор є комутатором К155КП1

Мультиплексори з Z станами виходу легко дозволяють збільшити число комутируємих каналів. 155КП7

Аналогові ключі, виконані по КМОП-технології, дозволяють створювати схеми з двунаправленою передачею даних. Ці схеми називаються мультиплексори-демультиплексори. К564КП1 8

Цифрові компаратори.

Цифрові компаратори пизначені для порівняння чисел, заданих в двійковому коді. Порівняння чисел можна робити, починаючи як з молодшого, так і зі старшого розряду. Перший варіант порівняння переважний, т. я. припускає більш природний спосіб нарощування їх розрядності. 555СП1, 531СП1

Для правильної роботи багатокаскадного компаратора на входи першої мікросхеми A>B і A<B необхідно подати логічну ”1“, а на A=B — логічний ”0“.

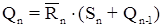

Послідовні схеми.

До послідовних схем відносяться різноманітні типи логічних елементів з двома або більше сталими станами і пристрої на їх основі. Функції виходів цих пристроїв визначаються не тільки комбінацією діючих сигналів на вході, але і станом цих виходів до подання вхідних сигналів. До них відносяться триггери, регістри, лічильники, ОЗП і т. д. Триггери.

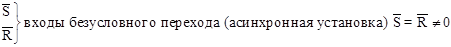

Триггерами називають спускові пристрої з двома можливими сталими станами. По виду вхідних сигналів розрізняють триггери з імпульсним і потенційним керуванням. В цифрових ЕОМ, в основному, застосовують потенційне керуванням. По способу запису інформації триггери поділяються на асинхронні і синхронні (ті, що тактуються). В асинхронних триггерах момент перемикання визначається моментом зміни кодової комбінації на входах. В синхронних — в чітко певні моменти надходження тактуючих імпульсов. Стан триггерів визначається по прямому виходу. Сигнал називається потенційним, якщо інтервали часу

RS-триггер.

Характеристичне рівняння.

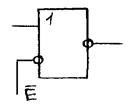

Функціонально триггер можна показати у вигляді елемента пам'яті зі схемою керування.

Елемент пам'яті зберігає інформацію про результат попереднього впливу на триггер. Схема керування виробляє сигнали, що забезпечують зберігання, підтвердження або зміну інформації. Цих сигналів в двійкових триггерах звичайно два: установка в ”1“ і установка в” 0“. Відсутність сигналів установки відповідає режиму зберігання інформації, а їхня одночасна дія призводить до невизначеного результату (стій ТАМ, іди СЮДИ). По реакції триггера на вхідні керуючі сигнали розрізняють наступні види входів: S — (Set) вхід для установки триггера в стан ”1“ на прямому виході; R — (Reset) вхід для скидання триггера в стан ”0“; D — (Delay-затримка) вхід для установки триггера в стан ”1“ при D=1, або в ”0“ при D=0 з затримкою; T — (Toggle-релаксатор) вхід перемикання триггера в протилежний стан. Тому вхід Т називають лічильним; J, K — (Jerk-включення, Kill-відключення) входи для установки і скидання триггера відповідно в ”1“ і ”0“. Аналогічні входам S і R; відзнака в тому, що одночасна присутність S і R призводять до непередбачувальності сигналів на виході, а одночасна поява J і K викликає однозначну зміну станів триггера аналогічно входу Т. V — вхід для дозволу або заборони реагування триггера на відповідні керуючі входи. Наявність окремих входів і визначає назву триггера. Транзисторний триггер з зовнішнім і автоматичним зміщенням.

Пристрій з позитивним зворотним зв'язком, що має два стани сталої рівноваги і може стрибком переходити з одного стану в інший під впливом керуючої напруги називається триггером.

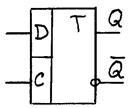

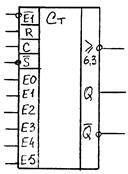

D-триггер. Найбільш часто в цифрових мікросхемах, а також в імпульсних приладах застосовують триггери з одним входом даних — D-триггери.

Т - триггер.

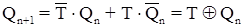

Це триггер з одним входом, що змінює свій стан по прибутті кожного імпульсу. Його ще називають лічильним. Характеристичне рівняння.

Ідеальний дільник на 2. Перемикається по задньому фронту, т.я. він двоступеневий (тому позначається ТТ). Мікросхемного виконання ні. JK - триггер.

Режим работи Вход Вихід

Асинхронна установка H B Асинхронне скиданн B H Невизначеність H H Перемикання B B B B Загрузка 0 (скидання) B B H B H B Загрузка 1 (установка) B B B H B H Зберігання (без змін) B B H H q

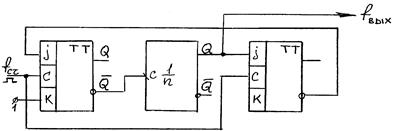

Лічильники. Лічильниками називають послідовністні цифрові пристрої, призначені для підрахунку і запам’ятовування числа імпульсів, поданих на лічильний вхід. Окрім лічильного входу можуть мати входи для асинхронної або синхронної установки початкових станів. По характеру модифікації станів розрізняють: підсумовуючі, віднімаючі і реверсивні. По засобу організації переносу між розрядами вони діляться на лічильники з послідовним, наскрізним і паралельним переносом. Лічильники з послідовним і наскрізним переносом називають асинхронними, а з паралельним переносом — синхронними. По кількості різноманітних станів виходу діляться на двійкові, десяткові, двійково-десяткові. Основними технічними параметрами лічильників є коефіцієнт перелічення Ксч і швидкодія. Коефіцієнт Ксч являє собою число різноманітних сталих станів, тобто максимальне число імпульсів, що лічильник може прорахувати і запам'ятати без повторення станів. Швидкодія лічильника визначається максимальною частотою надходження імпульсів, що реєструються лічильником без збоїв. Асинхронні лічильники.

В асинхронних лічильниках буде відсутня загальна для всіх розрядів синхронізація і перехід розрядів в нові стани відбувається послідовно, розряд за розрядом (доміно).

Лічильні входи JK-триггерів з'єднують з прямими виходами попередніх, а D-триггерами — з інверсними. Це пов’язано з тим, що D-триггер зпрацьовує по фронту, а JK - Триггер — по спаду вхідних імпульсів. По такому принципу зроблені лічильники: 155ІЕ2 — десятковий, 155ІЕ5 — двійковий. Основне достоїнство послідовного лічильника — мінімальні затрати мікросхем і мінімум електричних зв'язків. Головний недолік — низька швидкодія (чим більше Ксч). Дільники частоти відрізняються від лічильників тим, що в них використовується тільки один вихід — вихід останнього триггера. Таким чином, n-разрядний двійковий лічильник завжди можна розглядати як дільник на Частота на виході такого дільника рівна: fвых=fсч / Ксч Ксч — будь-яке ціле число. Ксч, яке вимагається, одержують введенням в лічильники зворотних зв'язків. Загальний принцип побудови дільників (лічильників) з непарним Ксч має вид.

Де N — число триггерів. Якщо між вхідним і вихідним триггерами включений дільник частоти на будь-яке натуральне число n, то така схема забезпечує ділення частоти на Ксч=

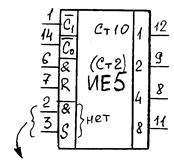

155ІЕ8 — програмуєть лічильник з входом для перемикання коефіцієнту перелічення.

На простих D-триггерах (і будь-яких) змінний коефіцієнт ділення можна зробити за допомогою зворотних зв'язків. Тепер розглянемо реверсивні лічильники. 155ІЕ6 — двійково-десятковий реверсивний лічильник.

Синхронні лічильники.

До синхронних або паралельних лічильників відносять лічильники, в яких перемикання розрядів відбувається одночасно, незалежно від віддаленості розряду від лічильного входу. Завдяки цьому вдається отримати мінімальний час установки нового стану, як ІЕ10. Одночасне переключення досягається подачею на всі триггери синхронизуючих імпульсов, що позитивним або негативним фронтом викликають переключення триггеров у відповідності з логікою роботи лічильника. К555ИЕ18, 531ІЕ16. Регістри.

Регістри — це послідовнісні пристрої, призначені для прийому, зберігання, зрушення і передачі двійкових чисел. Основне функціональне призначення регістрів — оперативна пам'ять для багаторозрядних двійковихих чисел. В залежності від способу прийому і передачі інформації розрізняють паралельні, послідовні (регістри зсуву), послідовно-паралельні, паралельно-послідовні і універсальні. В паралельних регістрах або регістрах пам'яті введення/виведення всіх розрядів числа виробляється водночас, за один такт. Для побудови n-разрядного регістру паматі вимагається n триггерів. Паралельні регістри служать основним функціональним елементом для побудови оперативних запам’ятовуючих приладів. В послідовних регістрах введення/виведення інформації здійснюється через один інформаційний вхід і один вихід порозрядно зі зсувом числа. Тому їх називають зсувними. За один такт вводима або виводима інформація зсувається на один розряд праворуч або ліворуч. Зсуваючі регістри, що зсувають і праворуч і ліворуч, називають реверсивними.

Приклад реверсивного регістру — 155ІР13 (8 розрядів). Послідовно-паралельні регістри виконують перетворення послідовного коду в паралельний. 155ІР8 (8 розрядів). Запам’ятовуючі пристрої.

Запам’ятовуючі пристрої (ЗП) служать для зберігання інформації і обміну нею з іншими частинами ЕОМ або мікропроцессорних систем. По функціональному призначенню ЗП діляться на зовнішні, буферні і внутрішні. Зовнішні ЗП служать для зберігання більшого обсягу інформації і програмного забезпечення системи. В них використовуються ЗП з прямим доступом (магнітні диски) і ЗП з послідовним доступом (магнітні стрічки). Буферні ЗП служать для проміжного зберігання даних при обміні між зовнішньою і внутрішньою пам'яттю. Внутрішні ЗП по функціям,що виконуються діляться на оперативні і постійні. Оперативні ЗП (ОЗП) виконують запис, зберігання і зчитування довільної двійкової інформації, забезпечують зберігання програм для поточної обробки інформації і масивів даних,що обробляються. Постійні ЗП (ПЗП) здійснюють зберігання і видавання постійно записаної інформації, вміст якої н

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-07-11; просмотров: 444; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.217.27 (0.036 с.) |

, тобто 800+60+5.

, тобто 800+60+5. , те є

, те є

, те є

, те є  називаються вагами.

називаються вагами.

позначають літерами латинського алфавіту від A до F.

позначають літерами латинського алфавіту від A до F.

) [латинське слово vel — або]. Аналогія — два (або більше) паралельно розташованих контактів.

) [латинське слово vel — або]. Аналогія — два (або більше) паралельно розташованих контактів.

) або (

) або ( ). Аналогія — два (або більше) послідовно розташовані контакти.

). Аналогія — два (або більше) послідовно розташовані контакти.

=1

=1  =0: Інверсія 0 рівна 1, інверсія 1 рівна 0.

=0: Інверсія 0 рівна 1, інверсія 1 рівна 0.

5%, а КМОП можуть працювати від +5 до +15В.

5%, а КМОП можуть працювати від +5 до +15В. Uж.

Uж. Uж.

Uж.

На 2 входи

На 2 входи

155ЛП2 8-разрядна парність

На 3 входи

155ЛП2 8-разрядна парність

На 3 входи

.

.

вхідних комбінацій. Але якщо накладається обмеження, що забороняє натиск двох і більше клавіш, то залишається тільки 11 вхідних комбінацій. Такий код називається “1 з n“ або унітарним. Якщо обмежень немає, тобто при натисканні декількох клавіш шифратор реагує на старшу (молодшу), то такий шифратор називають пріорітетним.

вхідних комбінацій. Але якщо накладається обмеження, що забороняє натиск двох і більше клавіш, то залишається тільки 11 вхідних комбінацій. Такий код називається “1 з n“ або унітарним. Якщо обмежень немає, тобто при натисканні декількох клавіш шифратор реагує на старшу (молодшу), то такий шифратор називають пріорітетним.

), з неповним набором.

), з неповним набором. Схему прямокутного дешифратора на n входів можна побудувати на основі системи перемикаючих функцій. При цьому прямокутний дешифратор має усього один ступінь дешифрації і число схем збігу І 2n штук.

Схему прямокутного дешифратора на n входів можна побудувати на основі системи перемикаючих функцій. При цьому прямокутний дешифратор має усього один ступінь дешифрації і число схем збігу І 2n штук. x1 x2 y0 y1 y2 y3

0 0 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1

x1 x2 y0 y1 y2 y3

0 0 1 0 0 0

0 1 0 1 0 0

1 0 0 0 1 0

1 1 0 0 0 1

) рівні 1.

2). Значення розряду суми дорівнює 1, якщо непарне число величин

) рівні 1.

2). Значення розряду суми дорівнює 1, якщо непарне число величин

176ЛП2, 531ЛП2

176ЛП2, 531ЛП2

сигналів на один вихід.

сигналів на один вихід.

1

Можна нарощувати і нарощувати.

1

Можна нарощувати і нарощувати.

переводу в Z стан всі двунаправлені виводи незалежно від значень інших вхідних сигналів.

переводу в Z стан всі двунаправлені виводи незалежно від значень інших вхідних сигналів.

між сусідніми вимірами сигналу значно більше часу реакції схеми

між сусідніми вимірами сигналу значно більше часу реакції схеми  , в якій вони використовуються, тобто

, в якій вони використовуються, тобто  .

.

— установочний вхід в ”1“

— установочний вхід в ”1“

— установочний вхід в ”0“

— установочний вхід в ”0“

. Ділянки АА' і BB' відповідають двом стійким станам, а точки A' і B' — пороговим значенням керуючої напруги.

Триггери широко застосовуються в якості електронних реле, елементів перерахуючих осередків ділильників частоти, формувачів прямокутних імпульсів і т. д.

. Ділянки АА' і BB' відповідають двом стійким станам, а точки A' і B' — пороговим значенням керуючої напруги.

Триггери широко застосовуються в якості електронних реле, елементів перерахуючих осередків ділильників частоти, формувачів прямокутних імпульсів і т. д.

К155ТМ2 — 2 штуки.ТМ5 — 4 штуки.

ТМ8 — 6 штук (для регістрів).

К155ТМ2 — 2 штуки.ТМ5 — 4 штуки.

ТМ8 — 6 штук (для регістрів).

К155ТВ1

К155ТВ1

Триггер двоступінчастий. Кожен з входів J і K забезпечиний тривхідною схемою і.

Триггер двоступінчастий. Кожен з входів J і K забезпечиний тривхідною схемою і.

J K Q

J K Q

q

q

Ксч

Ксч  ,

, Þ n= (Ксч-1)/2. Вимагається на 3, значить n=1.

Þ n= (Ксч-1)/2. Вимагається на 3, значить n=1. : 3

: 3

155ІЕ2

155ІЕ2

.

.

— дозвіл рахунку.

R — загальне скидання.

— дозвіл рахунку.

R — загальне скидання.

155ІЕ2

155ІЕ2

— для нарощування лічильника. Аналогічно працює 155ІЕ7 — двійковий лічильник.

— для нарощування лічильника. Аналогічно працює 155ІЕ7 — двійковий лічильник.