Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Пз №5. Решение задач по оценке основных параметров озуСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Цель занятия: Закрепить теоретические знания по основам построения и функционирования ЗУ ЦВМ. · Приобрести навыки практической работы по составлению алгоритмов работы запоминающих устройств ЦВМ, а также в решении задач по определению основных параметров ЗУ.

Методические указания 1. При подготовке к занятию: · повторить материал лекций по данной теме; · используя краткие теоретические сведения п.5.1, изучить алгоритмы работы различных типов ЗУ. 2. На занятии: · Составить схемы алгоритмов функционирования и перечни микроопераций в режимах записи и считывания для ОЗУ типа 2D и 3D. · Решить ряд задач, направленных на уяснение взаимной связи между такими параметрами ЗУ, как разрядность адреса, емкость ЗУ, разрядность хранимых кодов и т.п. 3. Контроль степени усвоения материала рекомендуется провести в конце занятия.

Краткие теоретические сведения о ЗУ

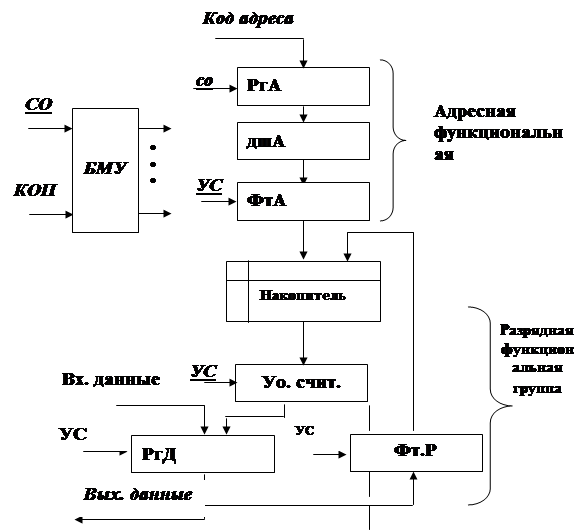

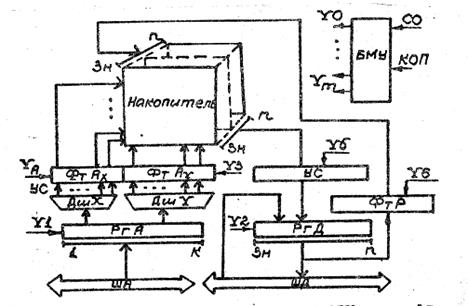

Память современных ВС и ЭВМ представляет собой многоуровневую систему запоминающих устройств. На верхнем уровне иерархической системы памяти используется устройство оперативной памяти или ОЗУ. ОЗУ - устройство внутренней памяти ЭВМ, предназначенное для хранения программы и данных, непосредственно используемых при выполнении операций в АЛУ. Структурная схема адресного ОЗУ не зависит от физических принципов, применяемых при реализации памяти, и в общем виде представлена на рис. 5.1. В состав ОЗУ входят: - адресная функциональная группа, содержащая регистр адреса (РгА), дешифратор адреса (ДшА), формирователь адресных токов (ФтА); - блок хранения информации или накопитель; - разрядная функциональная группа, содержащая усилители считывания (Ус.Счит.), регистр данных (РгД), формирователи разрядных токов (ФтР); - блок местного управления (БМУ).

Полупроводниковые ОЗУ в зависимости от способа организации накопителя (количества адресных и разрядных линий, соединённых с элементом памяти) разделяются на три основных типа: 2D, 3D, 2,5D. Для ОЗУ с регенерацией информации (магнитные ОЗУ) добавляется схема регенерации. При выполнении операций "Запись" от процессора на вход БМУ поступают сигнал обращения (СО) и код операции (КОП). СО инициирует начало работы ОЗУ. КОП задает соответствующий режим функционирования, в котором БМУ управляющими сигналами (УС) обеспечивает выполнение микроопераций: - прием кода адреса ячейки накопителя в РгА; - прием кода данных в РгД; - запись данных в накопитель (по входу DI) При выполнении операции "Считывание" БМУ обеспечивает режим чтения данных. Выполняются микрооперации: - прием кода адреса ячейки накопителя РгА, к которой происходит обращение; - прием кода данных (выход DO), считанного из накопителя в РгД, и выдача в процессор. В настоящее время ОЗУ преимущественно строятся на биполярных и МОП интегральных микросхемах памяти. ОЗУ на основе биполярных микросхем обладают высоким быстродействием. ОЗУ на основе МОП схем уступают по быстродействию, но превосходят их по емкости. Выработка управляющих сигналов, необходимых для синхронизации работы всех элементов ОЗУ, может осуществляться схемами, размещаемыми в микросхемах памяти (распределенное управление), или внешними схемами (централизованное управление). Так высокий уровень интеграции микросхем памяти (МОП-типа) позволяет на одном кристалле вместе в накопителем емкостью I Мбит разместить РгА, ДшА, УС, РгД и схему управления. Полупроводниковые ОЗУ в зависимости от способа организации накопителя (количества адресных и разрядных линий, соединенных с элементом памяти) разделяются на три основных типа: 2D,3D,2,5D.

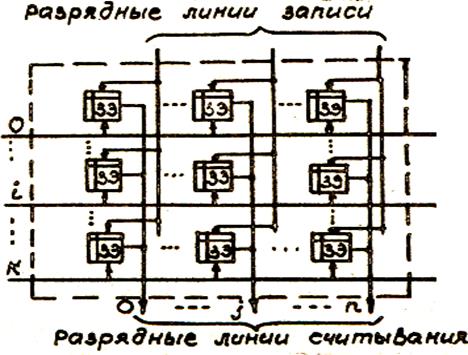

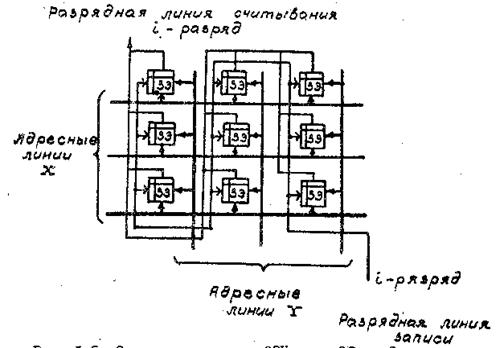

ОЗУ типа 2D Организация ОЗУ типа 2D обеспечивает двухкоординатную выборку каждого запоминающего элемента (3Э) ячейки памяти. Основу ОЗУ составляет плоская матрица из ЗЭ, сгруппированных в ячейки памяти (рис.5.2), Матрица содержит адресные и разрядные линии (шины). Адресные линии используются для обращения к ячейке памяти, которая хранит информационное слово. Разрядные линии записи и считывания позволяют выделить ЗЭ, хранящий бит информации. Структурная схема ОЗУ типа 2D представлена на рис. 5.3. Она включает адресную часть (РгА, ДшА, ФтА), разрядную часть (РгД, ФтР, УС), накопитель и БМУ. Адресная часть служит для приема, хранения и дешифрации кода адреса ячейки памяти, к которой производится обращение, а также для формирования адресных импульсов тока. Разрядная часть предназначена для приема, записи, считывания и выдачи из ОЗУ хранимых информационных слов. БМУ осуществляет синхронизацию работы узлов ОЗУ в режимах записи и чтения.

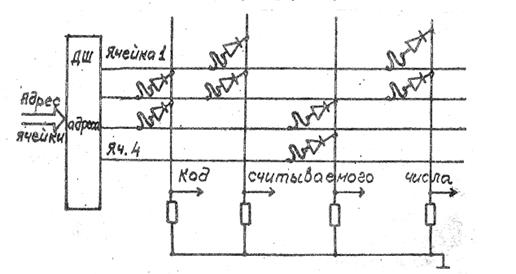

Рис. 5.2. Структура матрицы ОЗУ типа 2D для К слов разрядностью n.

Рис. 5.3. Структурная схема ОЗУ типа 2D

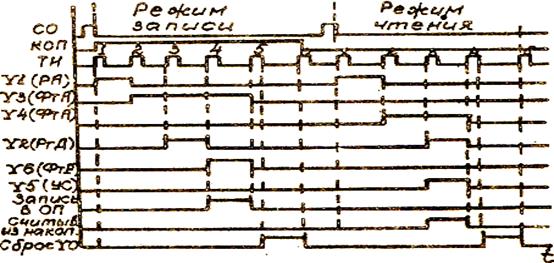

Алгоритм функционирования ОЗУ типа 2D Выполнение операции "Запись"; 1. От процессора по шинам управления на БМУ поступают сигналы СО и КОП, которыми инициируется работа ОЗУ и задается режим записи информации в накопитель. В БМУ запускается схема синхронизации, генерирующая управляющие сигналы (Y1,Y2,Y3,Y6) для режима записи. По шинам адреса (ША) и данных (ЩД) поступают коды адреса и информационного слова (данных). 2. Вырабатываемым управляющим сигналом Y1в первом такте разрешается прием адреса с ША в РгА. Код адреса записывается в РгА и подвергается расшифровке в ДшА. На одном из выходов ДшА появляется управляющий сигнал УС, указывающий адрес ячейки,к которой происходит обращение. 3. Сгенерированный во втором такте сигнал YЗ разрешает запуск ФтА. Сигналом Y3 запускается ФтА для записи. Он формирует на соответствующей адресной линии импульс заданной амплитуды и длительности, открывая тем самым информационное направление для данных, передаваемым по разрядным шинам записи в ЗЭ. Таким образом осуществляется выбор ячейки памяти. 4. В третьем такте сигнал Y2 открывает информационные входы РгД. Код слова с ШД записывается в РгД. 5. В следующем такте сигнал Y6 разрешает запуск ФтР. Единичными разрядами кода данных (слова), поступающего из РгД, осуществляется запуск разрядных формирователей тока записи. Сформированными импульсами заданной длительности и амплитуды осуществляется запись информационного слова в ячейку памяти. Режим записи завершается установкой схем БМУ в исходное по сигналу Y0. Временная диаграмма работы ОЗУ приведена на рис. 5.4.

Рис5.4. Временная диаграмма работы ОЗУ типа 2D

Выполнение операции "Считывание"; 1. При поступлении сигналов СО и КОП в БМУ запускается схема синхронизации, генерирующая последовательность управляющих сигналов YI; Y4; Y5; Y2; Y0 для режима чтения. 2. В первом такте по сигналу Y1 код адреса с ША поступает в РгА и расшифровывается схемой ДшА. 3. Во втором такте сигнал Y4 разрешает запуск ФтА. Сигналом Y4, поступающим с выхода ДшА, запускается ФтА. На адресной линии накопителя появляется импульс заданной амплитуды и длительности. Происходит выбор ячейки памяти. 4. В следующем такте сигналом Y5 открываются входы усилителей считывания (УС) и сигналом Y2 разрешается запись в РгД. Информационные слово из выбранной ячейки памяти по разрядным линиям считывания поступает на УС, где происходит усиление разрядных импульсов слова. С выхода УС слово поступает в РгД. Так как ФтР в этом режиме закрыт, информационное слово с выхода РгД снимается на ШД и поступает в процессор. 5. Режим чтения завершается установкой схемы БМУ в исходное состояние по Y0. Временная диаграмма представлена на рис. 5.4. ОЗУ типа 2Dявляются быстродействующими и достаточно удобными для реализации. Однако они неэкономичны по объему оборудования из-за наличия в них сложного дешифратора с 2K выходами, где К - разрядность адреса. В настоящее время структура типа 2D используется в основном в ЗУ небольшой емкости.

ОЗУ типа 3D

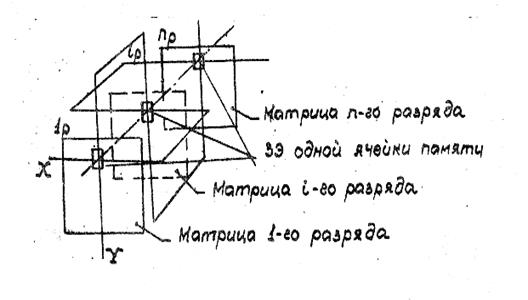

Организация ОЗУ типа 3D обеспечивает трех координатную выборку каждого запоминающего элемента (ЗЭ). Основу запоминающего массива составляют плоские матрицы (рис. 5.5). Каждая матрица содержит одноименные ЗЭ. Количество ЗЭ в матрице равно количеству слов в массиве. Считается, что матрица хранит одноименный разряд всех слов. Матрицы в массиве располагаются друг эа другом в порядке возрастания веса разряда в слове. Их количество эквивалентно количеству разрядов в слове. При такой организации запоминающего массива ячейка памяти имеет пространственную структуру - "пронизывает" плоские матрицы (рис. 5.6).

Рис 5.5. Матрица элементов i-го разряда ОЗУ типа 3D Рис 5.6. Структура ОЗУ типа 3D для К слов разрядностью n.

Для адресной выборки ЗЭ используются две координаты X. и Y. В матрице для этого имеются адресные линии, на пересечении которых располагаются ЗЭ. Разрядные линии записи и считывания проходят через все одноименные 33 матрицы и обеспечивают соответственно запись или считывание бита информации, выбранного ЭП. Для полупроводниковых ОЗУ характерно объединение разрядных линий в одну линию. Объединение матриц в массив осуществляется последовательным соединением адресных линий всех матриц.

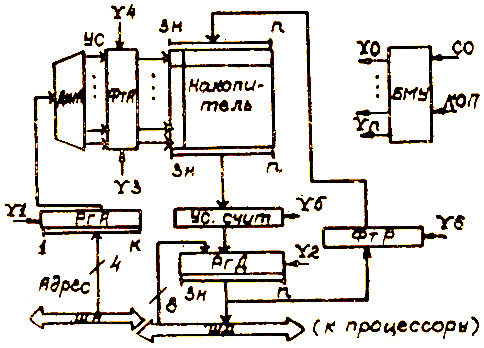

Рис. 5.7. Структура ОЗУ типа 3D Структура ОЗУ типа 3D и его составные части показаны на рис. 5.7. Алгоритм функционирования аналогичен алгоритму ОЗУ 2D. Отличие лишь в том, что ФтА формируют импульсы по двум адресным линиям X и Y. На пересечении этих линий сформированными токами (импульсами) осуществляется выбор ячейки памяти. Код адреса представлен старшей и младшей частями для координат X и Y. Диаграмма работы ОЗУ в отличие от диаграммы ОЗУ типа 2D вместо одного адресного импульса имеет два. Запоминающие устройства типа 3D более экономичны, чем ЗУ типа 2D. Они имеют более простые адресные формирователи, позволяющие строить ОЗУ большего объема, чем структура 2D. Однако полупроводниковые ЗЭ с тремя входами, используемыми при записи, не всегда удается реализовать.

Постоянные ЗУ

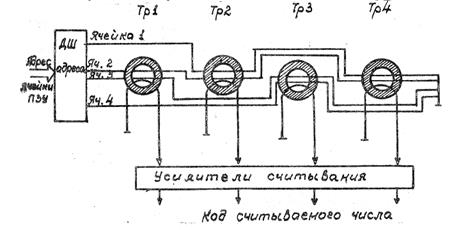

Постоянные ЗУ (ПЗУ) предназначены для длительного хранения не изменяющейся (постоянной) информации и работают только в режиме "Чтение". Для записи (перезаписи) хранящейся в ПЗУ информации необходима остановка ЦВМ и внесение изменений в конструкцию ПЗУ (например, смена платы с микросхемами памяти), либо включение ПЗУ в специальный режим перезаписи на устройствах, называемых программаторами ПЗУ. Типовые схемы ПЗУ трансформаторного типа и полупроводникового ПЗУ приведены на рис. 5.8 и 5.9 соответственно.

Рис. 5.8. Структура ПЗУ трансформаторного типа

Рис. 5.9. Структура полупроводникового ПЗУ

Принцип работа таких ПЗУ ясен из схемы и отличается от принципа работы ОЗУ отсутствием режима "Запись".

Определение основных параметров ЗУ Между техническими характеристиками ОЗУ, ПЗУ существует достаточно четкая взаимосвязь. Например, максимально возможное число ячеек в ЗУ зависит от разрядности адреса, предельная емкость ЗУ зависит как от разрядности адреса, так и от разрядности хранимых кодов и т.п. Поэтому, чтобы иметь возможность определять эти параметры, надо твердо представлять структуру ЗУ и соотношения между его основными характеристиками.

I. Число ячеек - N (предельно возможное) связано с разрядностью адреса - М соотношением N=2M (5.1) 2. Емкость ЗУ (в битах) - Е, определяется как Е = N*Р, (5.2) где P - разрядность хранимых кодов. 3. То же, в байтах и килобайтах, соответственно определяется как E=N*P/8 (5.3) E=N*P/(8*1024) Используя выражения всегда можно определить недостающие параметры ЗУ, если известны необходимые исходные. Например, нужно определить разрядность адреса ЗУ, если известна емкость в байтах и разрядность хранимых слов в битах, т.е. Е= 16 байт, P= 8. Тогда из (5.3) получаем N=8*Е/P=8*16/8=16бит Из (5.I), окончательно М=log2N=log2 16=4

Задание для работы на занятии

1. Изучить алгоритм работы ОЗУ, ПЗУ всех типов по структурной схеме. 2. Составить схемы алгоритмов работы ОЗУ 2D, 3D и ПЗУ. 3. Составить последовательности микроопераций, соответствующие алгоритмам. Пояснить назначение каждого управляющего сигнала - УС 4.Решить задачи по определению основных характеристик ЗУ (по вариантам, указанным преподавателем). Варианты задач Определить параметры ЗУ, помеченные знаком "?".

Задание на самоподготовку 1. Изучить по рекомендованной литературе особенности построения и функционирования ОЗУ типа 2,5D. 2. Определить разрядность адреса, необходимую для задания адресов ячеек в современных моделях персональных компьютеров.

Контрольные вопросы 1. Общие характеристики ОЗУ. 2. Единицы емкости ЗУ. 3. Типы ЗУ, их назначение и особенности структуры. 4. Типы ЗЭ и их характеристики. 5. Достоинства и недостатки ОЗУ типа 2D и 3D. 6. Пояснить структуру ячейки памяти 2D, 3D.

Литература 4. Пятибратов А.П. и др. Вычислительные системы, сети и телекоммуникации: Учебник.-2-е изд., перераб. и доп./ А.П.Пятибратов, Л.П. Гудыно, А.А.Кириченко; Под ред. А.П.Пятибратова. М.: Финансы и статистика, 2002.-512с:ил. с.111-122. 5. Каган Б.М. Электронные вычислительные машины и системы: Учеб. Пособие для вузов.-3-е изд.,перераб и доп.-М.: Энергоатомиздат,1991.-592с.:ил. с.99-124. 6. Нешумова К.А. Электронные вычислительные машины и системы. М.: Высшая школа, 1989.-366с.:ил. с.173-210.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-16; просмотров: 1781; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 13.58.53.112 (0.009 с.) |