Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Структура арифметико – логического устройстваСодержание книги

Поиск на нашем сайте

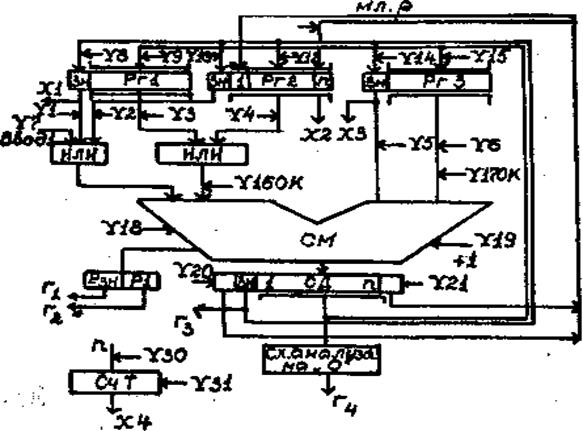

Структура АЛУ зависит от характера использования элементов и узлов, входящих в состав АЛУ, формы представления операндов, способов организации выполнения операций, организации связи между узлами. На рис.6.2 представлена упрощенная структурная схема АЛУ для операций над двоичными числами с фиксированной запятой.

Рис. 6.2. Структурная схема АЛУ параллельного типа

В состав АЛУ входят: n – разрядный параллельный комбинационный сумматор СМ; регистры для временного хранения операндов и промежуточных результатов Рг1, Рг2, Рг3; сдвигатель СД; счетчик тактов СчТ; вспомогательные логические схемы ИЛИ; схема анализа на ноль и схема формирования 2-разрядного кода признака [r1:r2] результата (Рзн и Р1 – переносы из знакового и старшего разряда СМ). Работа АЛУ осуществляется под действием управляющих сигналов Y1….Y21, которые вырабатываются УУ (БМУ). Каждый УС инициирует определенную микрооперацию, выполняемую в АЛУ. Перечень микроопераций приведен в табл.6.1 Формируемые сигналы X1….X4 и r1...r4 в виде сигналов состояния устройства (ССУ) поступают и там анализируются. Результаты анализа ССУ позволяют сформировать логическую последовательность микроопераций.

Таблица 6.1. Перечень микроопераций

П р и м е ч а н и е: При работе на микроЭВМ, при выполнении алгоритма умножения, сначала осуществляется сдвиг множителя (Рг2) по Y20А, потом сдвиг суммы частичных произведений (Рг3) по Y20.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-16; просмотров: 476; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.26.35 (0.008 с.) |

СД:=СД

СД:=СД

СД:=СД

СД:=СД