Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Генераторы логических функцийСодержание книги

Поиск на нашем сайте

Наиболее важными программируемыми элементами логическо- го блока являются схемы F-LUT, G-LUT и Н-LUT (см. рис. 1.2), вырабатывающие значения логических функций. С помощью эле- ментов F и G можно реализовать любую логическую функцию че- тырех переменных, а элемент Н позволяет сформировать значение любой логической функции трех переменных. Как построить универсальную схему, реализующую логические функции 4 переменных? Если решать эту задачу на уровне венти- лей, то она оказывается очень сложной, но если посмотреть на нее с другой точки зрения, то ее решение значительно облегчается. Любая функция 4-х переменных может быть описана таблицей ис- тинности, состоящей из 16 строк. Предположим, что мы храним таблицу истинности в одноразрядной памяти на 16 слов. Подавая на адресные входы памяти четыре входных бита, мы получаем на выходе значение функции для этой комбинации значений перемен- ных. Именно такой подход был принят разработчиками ПЛИС FPGA в фирме Xilinx. Схемы F и G, вырабатывающие значения логиче- ских функций, фактически являются очень компактными и быст- рыми статическими ЗУ 16´1, а схема Н представляет собой стати- ческое ЗУ 8´1. Когда логический блок используется для выполне- ния логических операций, то в статическое ЗУ загружаются табли- цы истинности логических функций F, G и Н. Время вычисления результата не зависит от воспроизводимой функции и равно времени считывания слова из памяти. Обратите внимание, что сигналы с выходов схем F и G, а также сигналы, поступающие на дополнительные входы логического блока, можно подать через мультиплексоры группы А на входы схемы Н (см. рис. 1.2), поэтому можно реализовать логические функции с числом переменных больше четырех. Ниже приведен перечень функций, которые можно реализовать с помощью схем F, G и Н в одном логическом блоке: • любая функция с числом переменных не более четырех плюс любая другая функция с числом переменных не более четы- рех, которые не связаны с переменными первой функции, плюс любая третья функция с числом независимых переменных не более трех; • любая одна функция пяти переменных; • любая функция четырех переменных плюс некоторые дру- гие функции шести переменных, не зависящих от переменных пер- вой функции; • некоторые функции с числом переменных до девяти, вклю- чая проверку на четность и проверку равенства двух 4-разрядных двоичных слов. При соответствующем программировании мультиплексоров группы В сигналы с выходов схем, вырабатывающих значения функций, могут быть выведены на выходы X и У логического блока или запомнены в переключающихся по фронту D-триггерах. Помимо удобства программирования, применение памяти для хранения таблиц истинности имеет другое важное достоинство. Каждая таблица преобразования LUT (Look-Up Table) может быть использована как оперативное запоминающее устройство с органи- зацией 16x1 или как 16-разрядный сдвиговый регистр. Это дает возможность использовать в проектах небольшие по объему блоки распределенной по кристаллу памяти. Триггер Каждый CLB содержит два триггера, которые могут использо- ваться для фиксации и хранения сигналов с выходов схем (LUT), вырабатывающих значения функций, или же работать независимо от них. Входной сигнал DIN может быть прямым входом для любо- го триггера (см. рис. 1.2). Сигнал H 1 тоже можно передавать лю- бому триггеру, но через схему Н-LUT, что вносит в цепь его пере- дачи некоторую задержку. Оба триггера имеют общие входы СК тактирования от сиг- нала К, разрешения тактирования ЕС и установки/сброса SR (см. рис. 1.2). Внутренние программируемые цепи в схеме триггера (рис. 1.3) позволяют индивидуально программировать полярность такти- рующего сигнала СК. С помощью мультиплексоров в триггерах может быть также ис- пользован вход разрешения тактового сигнала ЕС (см. рис. 1.3). Сигнал SR асинхронный и для каждого триггера программиру- ется с использованием внутренних цепей триггера как сигнал уста- новки или сброса. Этот сигнал определяет состояние, в котором окажется триггер после процесса конфигурации микросхемы. Кон- фигурация определяет и характер воздействия на триггеры импуль- сов GSR (Global SR) и SR при работе схемы.

Рис. 1.3. Триггерная схема конфигурируемого блока

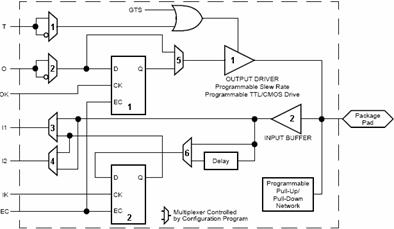

Блоки ввода/вывода сигналов ПЛИС FPGA находят широкое применение также благодаря то- му, что имеют большое число блоков ввода/вывода сигналов, на- страиваемых под различные стандарты электрического соединения микросхем. Блоки ввода/вывода (БВВ) обеспечивают интерфейс между выводами корпуса ПЛИС FPGA и ее внутренними логиче- скими схемами. Каждому выводу корпуса придается блок вво- да/вывода БВВ, который может быть конфигурирован как вход, выход или двунаправленный вывод. На рис. 1.4 показана упрощенная функциональная блок-схема одного блока ввода/вывода (I/O block, IOВ). Сигнальный вывод ПЛИС получил название PAD. С помощью настройки к нему мож- но подключать внутренний нагрузочный резистор PULL-UP или резистор PULL-DOWN, соединенные с шиной питания или шиной земли, соответственно. Эти резисторы обеспечивают режим выхода с открытым коллектором (стоком) для систем с различными уров- нями логики.

Рис. 1.4. Упрощенная структура блока ввода/вывода

Работа БВВ как выходного блока обслуживается следующими элементами: выходным буфером 1, триггером 1, мультиплексорами 1, 2, 5 и логической схемой ИЛИ (см. рис. 1.4). Выводимый сигнал О можно получать в прямой или инверсной форме в зависимости от программирования мультиплексора 2. Этот сигнал может пере- даваться на выходной буфер непосредственно или сниматься с триггера при соответствующем программировании мультип- лексоpa 5. Сигналы Т и GTS (Global Tri-State), согласно логике ИЛИ, управляют переводом буфера в третье состояние, причем ак- тивный уровень сигнала Т программируется с помощью мультип- лексора 1. Внутренние программируемые цепи триггера (на рисун- ке не показаны) позволяют изменять полярность тактирующего фронта. Сам буфер имеет программируемые крутизну фронта вы- ходного сигнала и его уровни — КМОП/ТТЛ. Крутизна фронтов в некритичных к скорости передачи цепях снижается для уменьше- ния уровня помех на шинах питания и земли. Тракт ввода сигналов содержит входной буфер 2, триггер 2, программируемые мультиплексоры 3, 4, 6, элемент задержки Delay (см. рис. 1.4). Вводимый сигнал в зависимости от программирова- ния мультиплексоров 3 и 4 или поступает непосредственно в сис- тему коммутации FPGA по входным линиям I 1 и I 2, или же фикси- руется триггером и с его выхода передается в эти линии. Для обес- печения временного сдвига входного сигнала относительно фронта синхросигнала, гарантирующего надежный прием сигнала во внут- ренний триггер, в цепь входного сигнала может включаться специ- альная схема задержки. Входной буфер может конфигурироваться для приема входных сигналов с пороговым значением ТТЛ (1,2 В) или КМОП (0,5 Ucc). Программируемые соединения Как показано на рис. 1.5, логические блоки в ПЛИС FPGA ок- ружены системой каналов, которые состоят из совокупности ме- таллических сегментов («проводов»), соединяемых друг с другом программируемым элементом связи (ключом). Трассировочные каналы вокруг CLB состоят из трех типов соединительных прово- дов: одинарной длины, двойной длины и длинные сегменты, пере- секающие кристалл по всей его длине или ширине. Кружками на рис. 1.5 отмечены программируемые точки связи. На пересечении каждого вертикального и горизонтального ка- налов находится матрица программируемых переключателей (PSM, Programmable Switching Matrix). Линии одинарной длины осуществляют соединения соседних или близлежащих CLB. Линии двойной длины огибают переключа- тельные блоки PSM, соседние по отношению к данному, и прохо- дят к следующим, чем облегчается установление более длинных связей. Три длинные линии, пересекающие весь кристалл по длине (ширине), предназначены на передачу сигналов на большие рас- стояния и при большой нагрузке. Выводы логических блоков (CLB) пересекают горизонтальные и вертикальные каналы трассировки, проходящие непосредственно около них, и могут программируемыми элементами связи (ключа- ми) подключаться к линиям каналов. Дальнейшее направление сиг- налов в нужные цепи осуществляется матрицей программируемых переключателей.

Рис. 1.5. Упрощенная система коммутации ПЛИС FPGA

В матрице программируемых переключателей (рис. 1.6) пересе- каются вертикальные и горизонтальные линии связи, и в каждом пересечении имеется цепь из 6 транзисторов для установления того или иного соединения. Сигнал, поступающий в матрицу переклю- чателей по какой-либо линии (например, горизонтальной), может быть направлен вверх, вниз или прямо в зависимости от того, какой транзистор будет открыт при конфигурировании FPGA. Возможна и одновременная передача сигнала по нескольким направлениям, если требуется его разветвление. Хотя матрица программируемых переключателей является не- обходимым компонентом, но за его использование приходится пла- тить: при каждом прохождении сигналов через такую матрицу вно- сится небольшая задержка. Поэтому программа компоновки ищет не только возможные размещения логических блоков и какую-то комбинацию соединений, которые будут работать. Программа «размещения и трассировки» затрачивает много времени, пытаясь оптимизировать характеристики устройства путем нахождения та- кого размещения, которое позволило бы сделать соединения корот- кими, и только после этого осуществляет реализацию самих соеди- нений.

Рис. 1.6. Матрица программируемых переключателей PSM

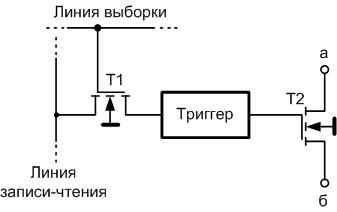

Транзисторный ключ, управляемый триггером памяти конфигу- рации, показан на рис. 1.7. Ключевой транзистор Т2 замыкает или размыкает участок аb в зависимости от состояния триггера, выход которого подключен к затвору транзистора Т2. При программиро- вании на линию выборки подается высокий потенциал, и транзи- стор Т1 включается. С линии записи-чтения подается сигнал, уста- навливающий триггер в состояние логической "1" или "0". В рабо- чем режиме транзистор Т1 заперт, триггер сохраняет неизменное состояние. Так как от триггера памяти конфигурации высокое бы- стродействие не требуется, он проектируется с оптимизацией по параметрам компактности и максимальной устойчивости стабиль- ных состояний. Помехи в несколько вольт для такого триггера не влияют на его состояние.

Рис. 1.7. Схема ключевого транзистора, управляемого триггером памяти конфигурации

Триггеры памяти конфигурации распределены по всему кри- сталлу СБИС вперемешку с элементами схемы, которые они кон- фигурируют. Загрузка соответствующих данных в память конфи- гурации программирует ПЛИС. Процесс оперативного программи- рования может производиться неограниченное число раз. В ПЛИС FPGA с триггерной памятью конфигурация разрушается при каж- дом выключении питания. При включении питания необходим процесс программирования (инициализации, конфигурирования) схемы — загрузка данных конфигурации. Обобщая представленную вводную информацию, можно еще раз отметить основные особенности ПЛИС: • возможность быстрого изменения принципиальной элек- трической схемы устройства на стадии проектирования, в том чис- ле с использованием языков описания аппаратуры (HDL); • малое время цикла «редактирование схемы — программи- рование ПЛИС — тестирование» при полном отсутствии каких- либо монтажных работ и материальных затрат; • поддержка внутри одного кристалла практически всего спектра современных технических решений в области цифровой электроники с гарантированными временными характеристиками; • относительно дешевые (в том числе и бесплатные) средства сквозной разработки, работающие на платформе ПК под управле- нием Windows, простые средства загрузки кристалла, дающие воз- можность с минимальными затратами провести освоение данной технологии.

|

||||||||||

|

Последнее изменение этой страницы: 2016-12-27; просмотров: 501; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.20 (0.008 с.) |