Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Описание комбинационной схемы в поведенческом стилеСодержание книги

Поиск на нашем сайте Ключевым поведенческим элементом языка VHDL является «процесс». Процесс (process) — это совокупность «последователь- ных» операторов, которые выполняются одновременно с другими параллельными операторами и с другими процессами. Логическая схема может быть описана последовательными операторами: case-when, if-then-else.

Последовательный оператор case Когда нужно выбирать среди нескольких альтернатив на осно- вании значения только одного сигнала или выражения, обычно бо- лее читабельным и дающим лучший результат синтеза является оператор case (case statement). Синтаксис оператора case: case expression is when choices => sequential-statements ... when choices => sequential-statements end case; В этом операторе вычисляется заданное выражение expression, по его значению выбирается одна из альтернатив choices и испол- няются соответствующие последовательные операторы sequential- statements. Заметьте, что в каждом из наборов альтернатив choices можно записать один или большее число последовательных опера- торов. Сами альтернативы choices могут иметь форму одного значения или нескольких значений, разделенных вертикальной чертой (|). Альтернативы choices должны быть взаимно исключаю- щими и содержать все возможные значения типа выражения ex- pression; в последней альтернативе choices можно воспользоваться ключевым словом others для указания всех значений, которые еще не были упомянуты ранее. В листинге 2.5 приведен вариант описания комбинационной схемы в поведенческом стиле, в котором используется оператор case. Подобно тому, как это было в варианте с параллельным оператором select (см. листинг 2.4), оператор case позволя- ет в очень наглядной форме задать желаемое функциональное по- ведение. Здесь также использован тип INTEGER для сигналов на входе А.

Листинг 2.5. Описание комбинационной схемы в поведенческом стиле с использованием оператора case

Последовательный оператор if Последовательный оператор if (if statement) дает возможность творчески подойти к описанию поведения схемы: if boolean-expression then sequential-statement end if; if boolean-expression then sequential-statement else sequential-statement End if if boolean-expression then sequential-statement elsif boolean-expression then sequential- statement ... elsif boolean-expression then sequential- statement end if; if boolean-expression then sequential-statement elsif boolean-expression then sequential- statement ... eisif boolean-expression then sequential- statement else sequential-statement end if; В первой и простейшей форме этого оператора проверяется бу- лево выражение boolean-expression и, если оно имеет значение true, то исполняется последовательный оператор sequential-statement. Во второй форме добавляется предложение "else" с другим последова- тельным оператором sequential-statement, который исполняется, если булево выражение имеет значение false. Для образования вложенных операторов if-then-else в языке VHDL использу- ют специальное ключевое слово elsif, которое вводит «средние» предложения. Последовательный оператор sequential-statement предложения elsif исполняется в том случае, когда булево вы- ражение boolean-expression в этом предложении истинно, а все предшествующие булевы выражения boolean-expressions оказыва- ются ложными. Последовательный оператор sequential-statement заключитель- ного необязательного предложения else исполняется только то- гда, когда все предыдущие выражения boolean-expressions имеют значения false. Для пояснения описания комбинационной схемы с использова- нием оператора if составим таблицу истинности (табл. 2.2) систе- мы логических функций (2.4). В этой таблице в столбцах под об- щим заголовком «Совпадение» отмечены одинаковые значения указанных функций на соответствующих наборах. В листинге 2.6 представлено поведенческое описание комбинационной схемы с использованием оператора if. Для более компактной записи ис- пользуется векторное описание как входов, так и выходов схемы. Идея приведенного описания состоит в том, что последователь- но проверяется принадлежность текущего состояния входов одно- му из подмножеств наборов, определяющих совпадающие значения функций F 1, F 2 и F 3 (см. табл. 2.2), после чего выходам присваива- ется соответствующее значение. Таблица 2.2 Таблица истинности

Листинг 2.6. Описание комбинационной схемы в поведенческом стиле с использованием оператора if

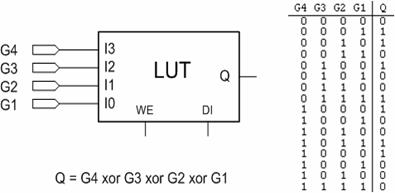

Замечание Реальная интерпретация приведенных выше описаний системы булевых функций на VHDL в аппаратной среде может существенно отличаться от схемного варианта, приведенного на рис. 2.6. Ком- пиляторы САПР проводят автоматическую оптимизацию схемы независимо от формы ее задания. В данном случае при реализации в ПЛИС функции F 1, F 2 и F 3 независимо от используемых опера- торов будут реализованы на полутора конфигурируемых логиче- ских блоках. Роль основного логического элемента в ПЛИС играет логиче- ская таблица (ЛТ) или look-up table (LUT), представляющая собой однобитное ОЗУ на 16 ячеек. Если в ЛТ по адресу G 3, G 2, G 1, G 0 записана единица, то код адреса представляет собой конституенту единицы заданной четырехвходовой логической функции. Напри- мер, если по адресу 1,1,1,1 записана единица, а по остальным адре- сам — ноль, то ЛТ реализует четырехвходовую функцию И. На рис. 2.7 показан пример кодирования функции «Исключающее ИЛИ» на четыре входа.

Рис. 2.7. Пример кодирования функции «Исключающее ИЛИ» на четыре входа

ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ 1. Изучить описание лабораторной работы. 2. Выполнить синтез многовыходной комбинационной схемы для трех переключательных функций F 1, F 2, F 3 на элементах И- НЕ. 3. Создать описание комбинационной схемы для трех пере- ключательных функций F 1, F 2, F 3 на VHDL в соответствии с усло- виями варианта.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ 1. Выполнить ввод спроектированной схемы в редакторе схем системы Xilinx Foundation. 2. Для облегчения отладки схемы подсоединить к её входам двоичный счетчик CB4CE (рис. 2.8). 3. Выполнить функциональное моделирование схемы

(см. рис. 2.8). Рис. 2.8. Схема эксперимента

4. Выполнить ввод и отладку описания комбинационной схе- мы на VHDL в том же проекте, где был реализован схемный вари- ант. 5. Выполнить подготовку и размещение двух вариантов схемы на кристалле, подсоединив к входам и выходам макроэлементы стенда (рис. 2.9). 6. Выполнить временное моделирование и измерение задер- жек переключения двух вариантов комбинационной схемы. 7. Выполнить загрузку проекта в ПЛИС стенда и произвести отладку схем на макете. 8. Продемонстрировать преподавателю работу отлаженной схемы на макете и на экране виртуального осциллографа. 9. Измерить задержки переключения комбинационной схемы. 10. Сдать преподавателю оформленный отчет в конце занятия.

ОТЧЕТ ПО РАБОТЕ Отчет должен содержать: 1) исходные данные варианта задания; 2) синтез многовыходной комбинационной схемы; 3) описание комбинационной схемы на VHDL; 4) результаты экспериментальных исследований.

Рис. 2.9. Схема, подготовленная для размещения на кристалле Список литературы 1. Миллер Р. Теория переключательных схем. В 2-х т. Т. 1. Комбинационные схемы. / Пер. с англ. Под ред. П.П. Пархоменко. М.: Наука, 1970. 2. Трачик В. Дискретные устройства автоматики. Пер. с польск. Под ред. Д.А. Поспелова. М.: Энергия, 1978. 3. Вавилов Е.Н., Портной Г.Н. Синтез схем электронных циф- ровых машин. М.: Советское радио, 1963. 4. Поспелов Д.А. Логические методы анализа и синтеза схем. М.: Энергия, 1974. 5. Блейксли Т.Р. Проектирование цифровых устройств с малы- ми и большими интегральными схемами. / Пер. с англ.: Вища шко- ла, 1981. 6. Угрюмов Е.П. Цифровая схемотехника. СПб.: БХВ, 2000. 7. Уэйкерли Дж. Ф. Проектирование цифровых устройств. В 2-х т. Т. 1-2. М.: Постмаркет, 2002. 8. Суворова Е.А., Шейнин Ю.Е. Проектирование цифровых систем на VHDL. СПб.: БХВ-Петербург, 2003. 9. Тарасов И.Е. Разработка цифровых устройств на основе ПЛИС XILINX с применением языка VHDL. М.: Горячая линия- Телеком, 2005. 10. Ковригин Б.Н. Введение в инструментальные средства про- ектирования и отладки цифровых устройств на ПЛИС: учебное по- собие. М.: МИФИ, 2006.

Лабораторная работа 3 ПРОЕКТИРОВАНИЕ СИНХРОННЫХ ТРИГГЕРНЫХ СХЕМ

Цель: изучить различную организацию синхронных триггер- ных схем; овладеть методом логического проектирования син- хронного двухступенчатого триггера; получить навыки проекти- рования синхронных триггерных схем на VHDL; приобрести опыт экспериментального исследования заданного типа триггера.

ВВЕДЕНИЕ

Практически все цифровые устройства сочетают функции по переработке информации с функцией хранения. Неотъемлемой ча- стью таких устройств является элемент памяти. В цифровых уст- ройствах для хранения информации чаще всего используется эле- мент с двумя устойчивыми состояниями — триггер. Структуру триггера можно представить в виде запоминающей ячейки (ЗЯ) и схемы управления (СУ) (рис. 3.1).

Рис. 3.1. Обобщенная структура триггерной схемы: СУ — схема управления; ЗЯ — запоминающая ячейка; Е 1, Е 2 — логические вхо- ды; С — вход синхронизации; S — вход установки в «1», R — вход сброса в «0» Запоминающая ячейка Запоминающая ячейка — это схема, которая имеет два выхода: Q и ⎯Q, разрешенные сигналы на которых всегда противоположны, и два входа: S (Set — установка) и R (Reset — сброс). Переклю- чающий сигнал по входу S устанавливает ЗЯ в состояние 1 (Q = 1, ⎯Q = 0), а по входу R — в состояние 0 (Q = 0, ⎯Q = 1). В общем слу- чае ЗЯ может иметь несколько установочных входов. Обычно она состоит из двух логических элементов, которые взаимно охвачены обратной связью (рис. 3.2).

Рис. 3.2. Запоминающая ячейка (асинхронный RS-триггер):

зируемым) RS-триггером. Такое название объясняется способом записи информации. Со- стояние асинхронного триггера определяется в каждый момент времени состоянием входов, т.е. изменения входного сигнала непо- средственно передаются на выход триггера.

Схема управления Схема управления (см. рис. 3.1) преобразует информацию, по- ступающую на входы Е 1 и Е 2, в сигналы, которые подаются на ус- тановочные входы ЗЯ. В некоторых схемах выходные сигналы триггера поступают на вход схемы управления (на рис. 3.1 эта связь показана пунктиром).

Синхронизирующий вход Триггеры, применяемые в потенциальной системе элементов, имеют, как правило, еще один вход — вход для синхронизирую- щих сигналов. Импульсы, на него поступающие, определяют мо- мент приема триггером входной информации. Поэтому в обобщен- ной структуре триггера (см. рис. 3.1) показан еще и вход синхрони- зации С.

Таким образом, рассматриваемые ниже триггеры обладают сле- дующими свойствами: на входы Е1 и Е2 поступают сигналы, несу- щие логическую (входную) информацию, на вход С — импульсы, которые логической информации не несут, а являются сигналами синхронизации. Входная информация принимается на хранение в триггер только с поступлением синхронизирующего импульса (СИ). Синхронные триггеры в зависимости от организации схемы управления разделяют на: синхронные триггеры со статическим управлением записью, синхронные двухступенчатые триггеры, синхронные триггеры с динамическим управлением записью.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-27; просмотров: 558; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.96 (0.012 с.) |

а) RS - триггер с прямыми входами на элементах ИЛИ-НЕ, его условное графиче- ское обозначение и таблица переходов; б) RS -триггер с инверсными входами на элементах И-НЕ, его условное графическое обозначение и таблица переходов

а) RS - триггер с прямыми входами на элементах ИЛИ-НЕ, его условное графиче- ское обозначение и таблица переходов; б) RS -триггер с инверсными входами на элементах И-НЕ, его условное графическое обозначение и таблица переходов Запоминающую ячейку называют асинхронным (несинхрони-

Запоминающую ячейку называют асинхронным (несинхрони- Поскольку прием входной информации определяется момен- том подачи импульса на вход синхронизации С, то такой триг- гер называют синхронным триггером.

Поскольку прием входной информации определяется момен- том подачи импульса на вход синхронизации С, то такой триг- гер называют синхронным триггером.