Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Интегральные схемы типа FPGAСодержание книги

Поиск на нашем сайте

СХЕМОТЕХНИКА ЭВМ Лабораторный практикум МОСКВА 2006 ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ РФ

МОСКОВСКИЙ ИНЖЕНЕРНО-ФИЗИЧЕСКИЙ ИНСТИТУТ

(ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ)

СХЕМОТЕХНИКА ЭВМ ЛАБОРАТОРНЫЙ ПРАКТИКУМ

Издание третье, переработанное и дополненное

Под редакцией Б.Н. Ковригина Москва 2006 УДК 004.2(076.5) ББК 32 973а7 К17

Схемотехника ЭВМ. Лабораторный практикум: у чебное пособие / Под ред.

Авторы: М.Н. Ёхин, Б.И. Кальнин, Б.Н. Ковригин, В.Г. Тышкевич, И.М. Яды- кин.

В пособии содержится описание шести лабораторных работ по курсу «Схемо- техника ЭВМ». В каждой работе дано краткое изложение теоретических основ и особенностей выполнения работ. Пособие рассчитано на студентов специальности «Вычислительные машины, комплексы и сети» и смежных специальностей, изучающих компьютерную техни- ку. Пособие предназначено для студентов дневного, вечернего и заочного обуче- ния.

Рецензент А.Л. Зорин

ISBN 5-7262-0674-6

© Московский инженерно-физический институт (государственный университет), 2006

СОДЕРЖАНИЕ Лабораторная работа 1. Изучение инструментальных средств проектирования цифровых схем....................................................................... 4 Лабораторная работа 2. Синтез комбинационных схем.............................................. 23 Лабораторная работа 3. Проектирование синхронных триггерных схем................... 54 Лабораторная работа 4. Синхронные счетчики............................................................ 95 Лабораторная работа 5. Проектирование многофункциональных регистров.......... 119 Лабораторная работа 6. Состязания сигналов в цифровых схемах.......................... 143 Приложение 1. Библиотечные элементы схемного редактора............................ 180 Приложение 2. Построение временных диаграмм работы цифровых схем....... 192 Приложение 3. Краткое руководство по работе с цифровым осциллографом..................................................... 198

Лабораторная работа 1 ИЗУЧЕНИЕ ИНСТРУМЕНТАЛЬНЫХ СРЕДСТВ ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ СХЕМ

Цель: изучить состав и возможности органов управления уни- версального лабораторного стенда; овладеть основными приема- ми проведения эксперимента на стенде; изучить полный маршрут проектирования цифровых схем с использованием САПР; получить навыки исследования проектируемых схем с использованием вир- туального осциллографа.

ВВЕДЕНИЕ

Лабораторный практикум по курсу «Схемотехника ЭВМ» вы- полняется в учебной лаборатории, основу которой составляет ав- томатизированное рабочее место студента-проектировщика (АРМ). Данная универсальная компьютеризированная лаборатория объединяет на единой инструментальной базе все практикумы по дисциплинам системотехнического цикла. АРМ студента-проектировщика – это комплекс аппаратно- программных средств, предназначенный для обучения основам схемотехники, проектированию цифровых систем на основе мик- роконтроллеров и программируемой логики. Каждое рабочее место включает: • персональный компьютер, оснащенный платой расширения цифрового осциллографа серии BORDO и 16-канального логиче- ского анализатора; • профессиональную САПР ПЛИС и инструментальные сред- ства автоматизации программирования микроконтроллера; • универсальный лабораторный стенд, содержащий ПЛИС FPGA XCS10-3PC84 фирмы XILINX, 8-ми разрядный микрокон- троллер семейства MCS-51 PCF80С552 фирмы PHILIPS, память и органы управления и индикации. В лабораторном практикуме по курсу «Схемотехника ЭВМ» ис- пользуется только часть оборудования стенда, а именно: ПЛИС FPGA XCS10-3PC84, клавишные регистры, генераторы и индика- ция. Разработка цифровых схем на ПЛИС невозможна без примене- ния систем автоматизированного проектирования (САПР). Особо значимыми становятся процедуры отладки и верификации проект- ных решений. Понимание единых общепризнанных средств описа- ний, создаваемых автоматизированными средствами проектирова- ния, необходимо для современного квалифицированного разработ- чика. Тщательное изучение возможностей и особенностей работы вспомогательного оборудования стенда и САПР имеет принципи- альное значение для успешного выполнения лабораторного прак- тикума в целом. Недостаточное знание инструментальных средств проектирования, используемых в практикуме, может привести к значительным затратам времени при выполнении лабораторных работ и, в конечном итоге, к неудаче в работе.

Н АЧАЛЬ НЫЕ СВЕДЕНИЯ О ПЛИС

Микросхемы программируемой логики или ПЛИС (программи- руемые логические интегральные схемы) — одно из наиболее ди- намично развивающихся направлений современной цифровой электроники. Привлекательность данной технологии заключается в предоставляемой конечному пользователю возможности быстрого создания цифровых устройств с произвольной внутренней структу- рой. По сравнению со специализированными цифровыми микро- схемами (Application Specific Integral Circuit, ASIC), цикл разработ- ки устройств на ПЛИС занимает значительно меньшее время и не- измеримо дешевле (благодаря тому, что изменение принципиаль- ной электрической схемы выполняется путем перепрограммирова- ния одного и того же экземпляра микросхемы). Таким образом, вместо металлических соединений, реализуемых в процессе произ- водства ASIC, в ПЛИС используются соединения, коммутируемые программируемыми ключами. Для задания этих соединений в ПЛИС существует теневая (конфигурационная) память, хранящая таблицу соединений. В настоящее время наиболее распространенные серии ПЛИС имеют следующую архитектуру: • CPLD (Complex Programmable Logic Device) — устройства, использующие для хранения конфигурации энергонезависимую память (Flash или EEPROM); • FPGA (Field Programmable Gate Array) — устройства, ис- пользующие для хранения конфигурации энергозависимую память, которая требует инициализации после включения питания. Поскольку универсальный лабораторный стенд содержит ПЛИС FPGA, то ниже рассматривается только этот тип микросхем про- граммируемой логики.

Триггер Каждый CLB содержит два триггера, которые могут использо- ваться для фиксации и хранения сигналов с выходов схем (LUT), вырабатывающих значения функций, или же работать независимо от них. Входной сигнал DIN может быть прямым входом для любо- го триггера (см. рис. 1.2). Сигнал H 1 тоже можно передавать лю- бому триггеру, но через схему Н-LUT, что вносит в цепь его пере- дачи некоторую задержку. Оба триггера имеют общие входы СК тактирования от сиг- нала К, разрешения тактирования ЕС и установки/сброса SR (см. рис. 1.2). Внутренние программируемые цепи в схеме триггера (рис. 1.3) позволяют индивидуально программировать полярность такти- рующего сигнала СК. С помощью мультиплексоров в триггерах может быть также ис- пользован вход разрешения тактового сигнала ЕС (см. рис. 1.3). Сигнал SR асинхронный и для каждого триггера программиру- ется с использованием внутренних цепей триггера как сигнал уста- новки или сброса. Этот сигнал определяет состояние, в котором окажется триггер после процесса конфигурации микросхемы. Кон- фигурация определяет и характер воздействия на триггеры импуль- сов GSR (Global SR) и SR при работе схемы.

Рис. 1.3. Триггерная схема конфигурируемого блока

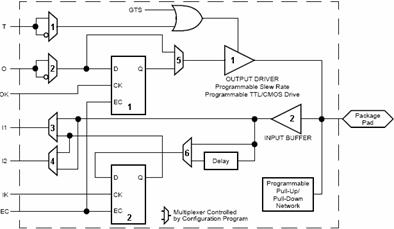

Блоки ввода/вывода сигналов ПЛИС FPGA находят широкое применение также благодаря то- му, что имеют большое число блоков ввода/вывода сигналов, на- страиваемых под различные стандарты электрического соединения микросхем. Блоки ввода/вывода (БВВ) обеспечивают интерфейс между выводами корпуса ПЛИС FPGA и ее внутренними логиче- скими схемами. Каждому выводу корпуса придается блок вво- да/вывода БВВ, который может быть конфигурирован как вход, выход или двунаправленный вывод.

На рис. 1.4 показана упрощенная функциональная блок-схема одного блока ввода/вывода (I/O block, IOВ). Сигнальный вывод ПЛИС получил название PAD. С помощью настройки к нему мож- но подключать внутренний нагрузочный резистор PULL-UP или резистор PULL-DOWN, соединенные с шиной питания или шиной земли, соответственно. Эти резисторы обеспечивают режим выхода с открытым коллектором (стоком) для систем с различными уров- нями логики.

Рис. 1.4. Упрощенная структура блока ввода/вывода

Работа БВВ как выходного блока обслуживается следующими элементами: выходным буфером 1, триггером 1, мультиплексорами 1, 2, 5 и логической схемой ИЛИ (см. рис. 1.4). Выводимый сигнал О можно получать в прямой или инверсной форме в зависимости от программирования мультиплексора 2. Этот сигнал может пере- даваться на выходной буфер непосредственно или сниматься с триггера при соответствующем программировании мультип- лексоpa 5. Сигналы Т и GTS (Global Tri-State), согласно логике ИЛИ, управляют переводом буфера в третье состояние, причем ак- тивный уровень сигнала Т программируется с помощью мультип- лексора 1. Внутренние программируемые цепи триггера (на рисун- ке не показаны) позволяют изменять полярность тактирующего фронта. Сам буфер имеет программируемые крутизну фронта вы- ходного сигнала и его уровни — КМОП/ТТЛ. Крутизна фронтов в некритичных к скорости передачи цепях снижается для уменьше- ния уровня помех на шинах питания и земли. Тракт ввода сигналов содержит входной буфер 2, триггер 2, программируемые мультиплексоры 3, 4, 6, элемент задержки Delay (см. рис. 1.4). Вводимый сигнал в зависимости от программирова- ния мультиплексоров 3 и 4 или поступает непосредственно в сис- тему коммутации FPGA по входным линиям I 1 и I 2, или же фикси- руется триггером и с его выхода передается в эти линии. Для обес- печения временного сдвига входного сигнала относительно фронта синхросигнала, гарантирующего надежный прием сигнала во внут- ренний триггер, в цепь входного сигнала может включаться специ- альная схема задержки. Входной буфер может конфигурироваться для приема входных сигналов с пороговым значением ТТЛ (1,2 В) или КМОП (0,5 Ucc). Программируемые соединения Как показано на рис. 1.5, логические блоки в ПЛИС FPGA ок- ружены системой каналов, которые состоят из совокупности ме- таллических сегментов («проводов»), соединяемых друг с другом программируемым элементом связи (ключом). Трассировочные каналы вокруг CLB состоят из трех типов соединительных прово- дов: одинарной длины, двойной длины и длинные сегменты, пере- секающие кристалл по всей его длине или ширине. Кружками на рис. 1.5 отмечены программируемые точки связи.

На пересечении каждого вертикального и горизонтального ка- налов находится матрица программируемых переключателей (PSM, Programmable Switching Matrix). Линии одинарной длины осуществляют соединения соседних или близлежащих CLB. Линии двойной длины огибают переключа- тельные блоки PSM, соседние по отношению к данному, и прохо- дят к следующим, чем облегчается установление более длинных связей. Три длинные линии, пересекающие весь кристалл по длине (ширине), предназначены на передачу сигналов на большие рас- стояния и при большой нагрузке. Выводы логических блоков (CLB) пересекают горизонтальные и вертикальные каналы трассировки, проходящие непосредственно около них, и могут программируемыми элементами связи (ключа- ми) подключаться к линиям каналов. Дальнейшее направление сиг- налов в нужные цепи осуществляется матрицей программируемых переключателей.

Рис. 1.5. Упрощенная система коммутации ПЛИС FPGA

В матрице программируемых переключателей (рис. 1.6) пересе- каются вертикальные и горизонтальные линии связи, и в каждом пересечении имеется цепь из 6 транзисторов для установления того или иного соединения. Сигнал, поступающий в матрицу переклю- чателей по какой-либо линии (например, горизонтальной), может быть направлен вверх, вниз или прямо в зависимости от того, какой транзистор будет открыт при конфигурировании FPGA. Возможна и одновременная передача сигнала по нескольким направлениям, если требуется его разветвление. Хотя матрица программируемых переключателей является не- обходимым компонентом, но за его использование приходится пла- тить: при каждом прохождении сигналов через такую матрицу вно- сится небольшая задержка. Поэтому программа компоновки ищет не только возможные размещения логических блоков и какую-то комбинацию соединений, которые будут работать. Программа «размещения и трассировки» затрачивает много времени, пытаясь оптимизировать характеристики устройства путем нахождения та- кого размещения, которое позволило бы сделать соединения корот- кими, и только после этого осуществляет реализацию самих соеди- нений.

Рис. 1.6. Матрица программируемых переключателей PSM

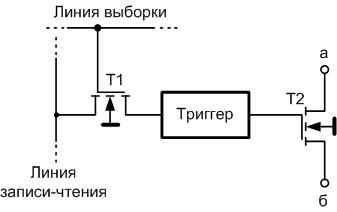

Транзисторный ключ, управляемый триггером памяти конфигу- рации, показан на рис. 1.7. Ключевой транзистор Т2 замыкает или размыкает участок аb в зависимости от состояния триггера, выход которого подключен к затвору транзистора Т2. При программиро- вании на линию выборки подается высокий потенциал, и транзи- стор Т1 включается. С линии записи-чтения подается сигнал, уста- навливающий триггер в состояние логической "1" или "0". В рабо- чем режиме транзистор Т1 заперт, триггер сохраняет неизменное состояние. Так как от триггера памяти конфигурации высокое бы- стродействие не требуется, он проектируется с оптимизацией по параметрам компактности и максимальной устойчивости стабиль- ных состояний. Помехи в несколько вольт для такого триггера не влияют на его состояние.

Рис. 1.7. Схема ключевого транзистора, управляемого триггером памяти конфигурации

Триггеры памяти конфигурации распределены по всему кри- сталлу СБИС вперемешку с элементами схемы, которые они кон- фигурируют. Загрузка соответствующих данных в память конфи- гурации программирует ПЛИС. Процесс оперативного программи- рования может производиться неограниченное число раз. В ПЛИС FPGA с триггерной памятью конфигурация разрушается при каж- дом выключении питания. При включении питания необходим процесс программирования (инициализации, конфигурирования) схемы — загрузка данных конфигурации. Обобщая представленную вводную информацию, можно еще раз отметить основные особенности ПЛИС: • возможность быстрого изменения принципиальной элек- трической схемы устройства на стадии проектирования, в том чис- ле с использованием языков описания аппаратуры (HDL); • малое время цикла «редактирование схемы — программи- рование ПЛИС — тестирование» при полном отсутствии каких- либо монтажных работ и материальных затрат; • поддержка внутри одного кристалла практически всего спектра современных технических решений в области цифровой электроники с гарантированными временными характеристиками; • относительно дешевые (в том числе и бесплатные) средства сквозной разработки, работающие на платформе ПК под управле- нием Windows, простые средства загрузки кристалла, дающие воз- можность с минимальными затратами провести освоение данной технологии.

XCS10-3PC84

В данном практикуме используется только часть оборудования стенда: ПЛИС FPGA XCS10-3PC84, клавишные регистры, генера- торы и индикация. Контакты корпуса ПЛИС уже распаяны на пе- чатной плате лабораторного стенда и выведены на его органы управления. Часть лицевой панели стенда с используемыми орга- нами управления приведена на рис. 1.8.

Рис. 1.8. Органы управления универсального лабораторного стенда

Для задания воздействий на схему, которая предварительно должна быть загружена в ПЛИС XCS10, на стенде имеются: • два генератора одиночных импульсов — ГОИ1 и ГОИ2. Первый из них может работать в одном из двух режимов — либо в режиме одиночных импульсов, либо в режиме непрерывных им- пульсов. Выбор режима осуществляется рядом стоящим тумблером (см. рис. 1.8); • три клавишных регистра Р 1, Р 2 и Р 3, используемых для за- дания постоянных значений. Для целей контроля состояния схемы в процессе её отладки на стенде имеются шесть четырехразрядных светодиодных шкал (см. рис. 1.8), которые можно подключать к произвольным точкам схемы. Таким образом, можно одновременно наблюдать состояние схемы в 24 точках. В системе проектирования органы управления оформлены в ви- де макроэлементов и содержатся в библиотеке проекта с именем «maket».

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ А. Ввод и моделирование схемы в системе Xilinx Foundation 1. Войти в систему и открыть новый проект под своим име- нем. Примечание. Данный пункт и все последующие выполняются, руководствуясь пособием [2]. 2. Выполнить ввод схемы, приведенной на рис. 1.9 (счет- чик+дешифратор), в редакторе схем. 3. Выполнить функциональное моделирование созданной схе- мы (рис. 1.10).

Рис. 1.9. Схема соединения счетчика и дешифратора

Рис. 1.10. Временная диаграмма работы счетчика и дешифратора

Б. Загрузка проекта в ПЛИС и отладка схемы на стенде 1. Выполнить подготовку схемы для размещения на кри- сталле, подсоединив к входам и выходам макроэлементы стенда (рис. 1.11). 2. Выполнить размещение подготовленной схемы на кристал- ле (см. [2]). 3. Выполнить загрузку проекта в ПЛИС (см. [2]). 4. Произвести отладку схемы на лабораторном стенде. 5. Продемонстрировать преподавателю работу схемы на стен- де и на экране виртуального осциллографа. 6. Измерить по указанию преподавателя задержки переклю- чения схемы.

Рис. 1.11. Схема с макроэлементами стенда

Список литературы 1. Кнышев Д.А., Кузелин М.О. ПЛИС фирмы «XILINX»: опи- сание структуры основных семейств. М.: «Додэка-ХХ1». 2001. 2. Ковригин Б.Н. Введение в инструментальные средства про- ектирования и отладки цифровых устройств на ПЛИС / Учебное пособие. М.: МИФИ. 2006. 3. Кузелин М.О., Кнышев Д.А., Зотов В.Ю. Современные се- мейства ПЛИС фирмы Xilinx. М.: Горячая линия-Телеком. 2004. 4. Мальцев П.П, Гарбузов Н.И., Шарапов А.П., Кнышев Д.А. Программируемые логические ИМС на КМОП-структурах и их применение. М.: Энергоатомиздат. 1998. 5. Тарасов И.Е. Разработка цифровых устройств на основе ПЛИС XILINX с применением языка VHDL. М.: Горячая линия- Телеком. 2005. 6. Угрюмов Е.П. Цифровая схемотехника. СПб.: БХВ. 2000. 7. The Programmable Logic Data Book. Xilinx Inc. 1999.

Лабораторная работа 2 СИНТЕЗ КОМБИНАЦИОННЫХ СХЕМ

Цель: изучить методы синтеза комбинационных схем на логи- ческих элементах; получить навыки проектирования комбинаци- онных схем на VHDL; овладеть инструментальными средствами проектирования схем на ПЛИС; приобрести опыт эксперимен- тального исследования синтезируемых схем. ВВЕДЕНИЕ

Схемы, выходное состояние которых однозначно определяется только комбинацией входных сигналов, называют комбинацион- ными. Закон функционирования комбинационной схемы определя- ется системой переключательных (логических) функций:

F 2 = f 2 K (x 1, x 2 ,K, xn ),⎪ ⎬ ⎪

(2.1) Fk = f k (x 1, x 2,K, xn).⎪⎭ Синтез комбинационной схемы состоит в построении схемы на основе заданного закона ее функционирования в виде системы пе- реключательных функций или таблиц истинности. При синтезе комбинационной схемы чаще всего необходимо построить схему с использованием минимального числа элементов в заданном эле- ментном базисе, например, на элементах И-НЕ. Задача проектиро- вания комбинационных схем в общем случае не имеет однозначно- го решения.

Проектирование одновыходной комбинационной схемы на эле- ментах И-НЕ состоит из следующих шагов: · получение минимальной ДНФ переключательной функции; · представление полученной минимальной формы в базисе Шеффера; · построение по полученному выражению комбинационной схемы. Пусть задана функция F 1 от четырех переменных в виде деся- тичных номеров конституент совершенной дизъюнктивной нор- мальной формы, т.е. тех наборов, на которых функция равна еди- нице: F 1 (x 3, x 2, x 1, x 0) = S(0, 2, 4, 6, 10, 12, 14, 15). Эту функцию необходимо реализовать на элементах И-НЕ. За- пишем эту функцию в виде логического выражения:

Ú (x 3 x 2 x 1 x 0).

Минимизация функции

Рис. 2.1. Минимизация функции при помощи диаграммы Вейча Получим следующее минимальное выражение функции:

(2.2)

Функций Пусть даны три функции, каждая из которых зависит от четырех переменных:

F 2 (A, B, C, D) = å (2, 3,10), ⎪ (2.4)

Таким образом, сначала находят все простые импликанты каж- дой функции системы F 1, F 2, F 3. Затем из функций системы обра- зуют все возможные подсистемы, состоящие из двух функций: F 1× F 2, F 1· F 3, F 2· F 3. Для каждой из полученных подсистем функций находят все простые импликанты. Затем образуют подсистему из трех функций F 1· F 2· F 3 и для нее находят все простые импликанты. Эту процедуру удобнее всего выполнить, используя диаграм- мы Вейча. Занесем исходные функции на три диаграммы Вейча (рис. 2.4).

Рис. 2.4. Диаграммы Вейча трех функций Найдем все простые импликанты для этих функций, т.е. сокра- щенную дизъюнктивную нормальную форму (СкДНФ) функций F 1, F 2, F 3:

F 1 = BD Ú CD Ú AD,⎫

F 2 = BCD Ú ABC, ⎬

(2.5)

Затем необходимо найти СкДНФ функций, представляющих со- бой все сочетания логических произведений исходных функций: F 1· F 2, F 1· F 3, F 2· F 3 и F 1· F 2· F 3. Получение логического произведения функций легко осущест- вить с помощью диаграммы Вейча. Для этого необходимо совмес- тить диаграммы Вейча соответствующих функций. Затем в каждой клетке совмещенной диаграммы выполнить операцию конъюнкция над значениями совмещаемых функций. Данная операция показана на рис. 2.5 для функции F 1· F 2. На этом же рисунке представлены диаграммы Вейча и для ос- тальных логических произведений исходных функций.

По полученным диаграммам найдем простые импликанты дан- ных функций: F 1 × F 2 = BCD, ⎫ F × F = ABD, ⎪

1 3 ⎪ (2.6)

F 2 × F 3 = ABC,

Рис. 2.5. Диаграммы Вейча логических произведений трех функций

End if if boolean-expression then sequential-statement elsif boolean-expression then sequential- statement ... elsif boolean-expression then sequential- statement end if; if boolean-expression then sequential-statement elsif boolean-expression then sequential- statement ... eisif boolean-expression then sequential- statement else sequential-statement end if; В первой и простейшей форме этого оператора проверяется бу- лево выражение boolean-expression и, если оно имеет значение true, то исполняется последовательный оператор sequential-statement. Во второй форме добавляется предложение "else" с другим последова- тельным оператором sequential-statement, который исполняется, если булево выражение имеет значение false. Для образования вложенных операторов if-then-else в языке VHDL использу- ют специальное ключевое слово elsif, которое вводит «средние» предложения. Последовательный оператор sequential-statement предложения elsif исполняется в том случае, когда булево вы- ражение boolean-expression в этом предложении истинно, а все предшествующие булевы выражения boolean-expressions оказыва- ются ложными. Последовательный оператор sequential-statement заключитель- ного необязательного предложения else исполняется только то- гда, когда все предыдущие выражения boolean-expressions имеют значения false. Для пояснения описания комбинационной схемы с использова- нием оператора if составим таблицу истинности (табл. 2.2) систе- мы логических функций (2.4). В этой таблице в столбцах под об- щим заголовком «Совпадение» отмечены одинаковые значения указанных функций на соответствующих наборах. В листинге 2.6 представлено поведенческое описание комбинационной схемы с использованием оператора if. Для более компактной записи ис- пользуется векторное описание как входов, так и выходов схемы. Идея приведенного описания состоит в том, что последователь- но проверяется принадлежность текущего состояния входов одно- му из подмножеств наборов, определяющих совпадающие значения функций F 1, F 2 и F 3 (см. табл. 2.2), после чего выходам присваива- ется соответствующее значение. Таблица 2.2 Таблица истинности

Листинг 2.6. Описание комбинационной схемы в поведенческом стиле с использованием оператора if

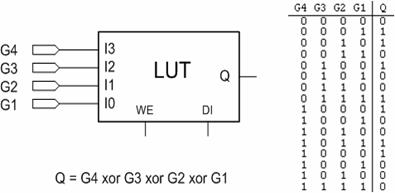

Замечание Реальная интерпретация приведенных выше описаний системы булевых функций на VHDL в аппаратной среде может существенно отличаться от схемного варианта, приведенного на рис. 2.6. Ком- пиляторы САПР проводят автоматическую оптимизацию схемы независимо от формы ее задания. В данном случае при реализации в ПЛИС функции F 1, F 2 и F 3 независимо от используемых опера- торов будут реализованы на полутора конфигурируемых логиче- ских блоках. Роль основного логического элемента в ПЛИС играет логиче- ская таблица (ЛТ) или look-up table (LUT), представляющая собой однобитное ОЗУ на 16 ячеек. Если в ЛТ по адресу G 3, G 2, G 1, G 0 записана единица, то код адреса представляет собой конституенту единицы заданной четырехвходовой логической функции. Напри- мер, если по адресу 1,1,1,1 записана единица, а по остальным адре- сам — ноль, то ЛТ реализует четырехвходовую функцию И. На рис. 2.7 показан пример кодирования функции «Исключающее ИЛИ» на четыре входа.

Рис. 2.7. Пример кодирования функции «Исключающее ИЛИ» на четыре входа

ПОДГОТОВКА К ВЫПОЛНЕНИЮ РАБОТЫ 1. Изучить описание лабораторной работы. 2. Выполнить синтез многовыходной комбинационной схемы для трех переключательных функций F 1, F 2, F 3 на элементах И- НЕ. 3. Создать описание комбинационной схемы для трех пере- ключательных функций F 1, F 2, F 3 на VHDL в соответствии с усло- виями варианта.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ 1. Выполнить ввод спроектированной схемы в редакторе схем системы Xilinx Foundation. 2. Для облегчения отладки схемы подсоединить к её входам двоичный счетчик CB4CE (рис. 2.8). 3. Выполнить функциональное моделирование схемы

(см. рис. 2.8). Рис. 2.8. Схема эксперимента

4. Выполнить ввод и отладку описания комбинационной схе- мы на VHDL в том же проекте, где был реализован схемный вари- ант. 5. Выполнить подготовку и размещение двух вариантов схемы на кристалле, подсоединив к входам и выходам макроэлементы стенда (рис. 2.9). 6. Выполнить временное моделирование и измерение задер- жек переключения двух вариантов комбинационной схемы. 7. Выполнить загрузку проекта в ПЛИС стенда и произвести отладку схем на макете. 8. Продемонстрировать преподавателю работу отлаженной схемы на макете и на экране виртуального осциллографа. 9. Измерить задержки переключения комбинационной схемы. 10. Сдать преподавател

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-27; просмотров: 364; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.18.110.214 (0.016 с.) |

Б.Н. Ковригина. Изд. 3-е, перераб. и доп. М.: МИФИ, 2006. 212 с.

Б.Н. Ковригина. Изд. 3-е, перераб. и доп. М.: МИФИ, 2006. 212 с. © Ёхин М.Н., Б.И. Кальнин, Ковригин Б.Н. и др., 2006

© Ёхин М.Н., Б.И. Кальнин, Ковригин Б.Н. и др., 2006

Произведем минимизацию заданной функции, используя метод диаграмм Вейча (рис.2.1).

Произведем минимизацию заданной функции, используя метод диаграмм Вейча (рис.2.1).

F 1мин (x 3, x 2, x 1, x 0) = x 2 x 0 Ú x 1 x 0 Ú x 3 x 0 Ú x 3 x 2 x 1.

F 1мин (x 3, x 2, x 1, x 0) = x 2 x 0 Ú x 1 x 0 Ú x 3 x 0 Ú x 3 x 2 x 1. Простые импликанты системы логических функций (2.4) представляют собой совокупность простых импликант всех сочетаний логических произведений исходных функций, включая и функции системы: F 1, F 2, F 3, F 1× F 2, F 1· F3, F 2· F 3 и F 1 ·F 2 ·F 3.

Простые импликанты системы логических функций (2.4) представляют собой совокупность простых импликант всех сочетаний логических произведений исходных функций, включая и функции системы: F 1, F 2, F 3, F 1× F 2, F 1· F3, F 2· F 3 и F 1 ·F 2 ·F 3.

⎪

⎪