Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Создание проекта в Xilinx ISEСодержание книги Похожие статьи вашей тематики

Поиск на нашем сайте

После запуска программы Xilinx ISE создадим новый проект. Первым шагом задается имя проекта, путь к папке, в которую он будет сохранятся и тип источника верхнего уровня (рисунок 2.3). В нашем случае, тип источника верхнего уровня – HDL.

Рисунок 2.3 – Меню создания проекта

На следующем шаге определяемся с аппаратным обеспечением, на котором будем работать (рисунок 2.4). В нашем случае платформа не важна. По-этому, как и в предыдущей работе, выберем аппаратную часть «ZYNQ XC7Z020»

Рисунок 2.4 – Меню выбора аппаратного обеспечения

После создания проекта откроется основное окно рабочей среды. Чтобы добавить новый модуль, нужно во всплывающем меню проекта, на вкладке «Hierarchy», выбрать кнопку «New Source» (рисунок 2.5).

Рисунок 2.5 – Всплывающее меню проекта

Первым шагом, при создании нового модуля, задаем его имя и тип. В нашем случае, тип модуля должен быть «Verilog Module». Так же необходимо проследить, чтобы был отмечен пункт «Add to project» (рисунок 2.6).

Рисунок 2.6 – Меню создания модуля

Далее задаются входы и выходы нового модуля (рисунок 2.7).

Рисунок 2.7 – Меню задания входов и выходов нового модуля

После создания нового модуля открывается редактор кода. В коде необходимо описать работу устройства, передающего данные на вход интерфейса RS-232, принятые 8-ми разрядной шине. Проект состоит из нескольких модулей, описывающих работу отдельных устройств, таких как: буфер FIFO (BuferFIFO), счетчик (Counter), мультиплексор (Multiplex), дешифратор (Decoder) и трансмиттера (Transmitter). На рисунке 2.8 представлен редактор кода буфера FIFO.

Рисунок 2.8 – Редактор кода модуля

Тестирование Для тестирования создается новый модуль. Алгоритм его создания ничем не отличается от создания рабочего модуля за одним не большим исключением: тип рекомендуется указывать «Verilog Test Fixture» (рисунок 2.9). В этом случае, в фале, сразу генерируется основной код тестового модуля.

Рисунок 2.9 – Меню создания тестового модуля

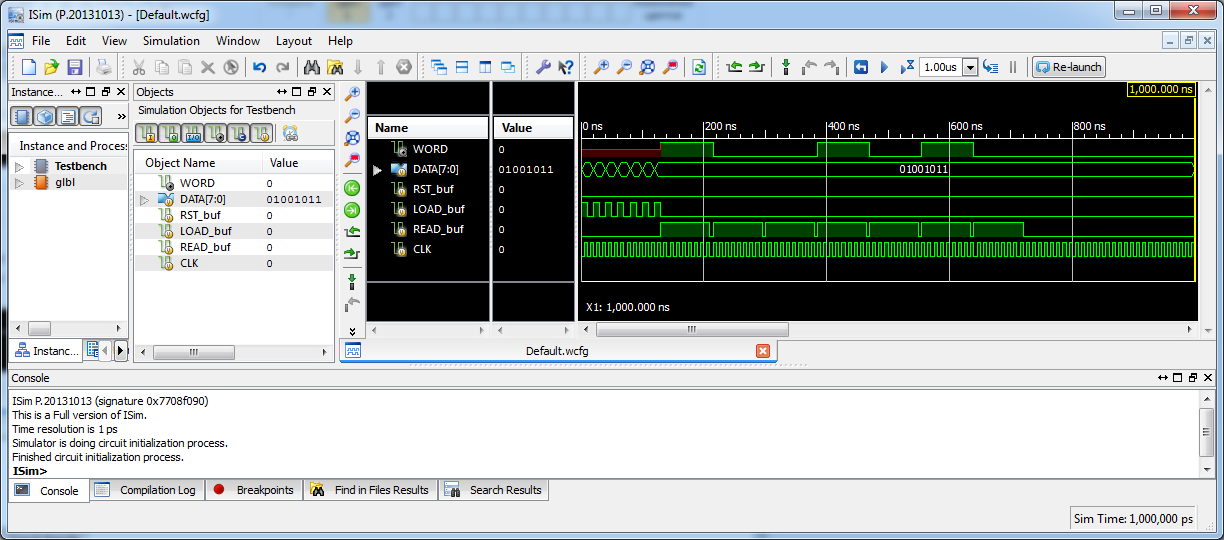

Затем, по требованию программы, привязываем тестовый модуль к верхнему модулю в дереве. После того, как тестовый модуль написан, можно запустить симуляцию. Для этого, в разделе «Design» должен стоять флажок на пункте «Simulation», в разделе «Hierarchy» выделен тестовый модуль. После щелчка по пункту «Simulate Behavioral Model» из раздела «ISim Simulator» запуститься симуляция. Симуляция проходит в несколько этапов. Сначала, всегда, запускается процесс проверки синтаксиса (Behavioral Check Syntax). Если ошибок не обнаружено происходит симуляция модели. В дополнение нужно сказать, что процесс проверки ошибок синтаксиса (Behavioral Check Syntax) можно запускать отдельно. В результате появляется окно «ISim» (рисунок 2.10). В нем можно увидеть диаграмму входных и выходных сигналов. Также, в разделе «Instance and Process Name» можно увидеть другие сигналы, не попавшие на диаграмму. Чтобы увидеть уровень напряжения нужного сигнала, необходимо перетащить его на панель «Name».

Рисунок 2.10 – Окно результатов симуляции

|

||||

|

Последнее изменение этой страницы: 2019-08-19; просмотров: 768; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.147.126.199 (0.007 с.) |