Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Создание проекта в Xilinx VivadoСодержание книги Похожие статьи вашей тематики

Поиск на нашем сайте

Создадим новый проект. В процессе создании проекта, при выборе типа проекта, укажем «RTL Project» – проект со схемой, построенной на принципе уровней регистровых передач (от англ. Register Transfer Level). Смысл такой схемы заключается в том, что она полностью описывает структуру данного устройства, элементами которой являются схемотехнические принципы (триггеры, регистры и т.д.). Также существуют другие типы проектов: - Post-synthesis Project – создать проект для работы с уже синтезированным проектом. В проект можно добавить уже готовые модули, провести синтез и создать файл для программирования ПЛИС; - I/O Planning Project – создать проект для работы с входами и выходами ПЛИС; - Imported Project – импортировать проект из других сред разработки ПЛИС: Synplify или Xilinx ISE; - Example Project – создать проект для работы с одним из проектов-примеров. Меню выбора типов проекта приведено на рисунке 1.2.

Рисунок 1.2 – Меню выбора типа проекта

Следующим важным шагом является выбор ПЛИС (во вкладке «Parts»), для которой создаётся проект, или сразу выбрать отладочную плату (вкладка «Boards»). В данном разделе выбираются следующие параметры: - Product category – назначение ПЛИС; - Family – семейство; - Sub-Family – подсемейство; - Package – комплекция; - Speed Grade – класс скорости; - Temp Grade – временные параметры. Так как в данной работе выбор этих параметров значения не имеет, можно выбрать сразу плату, например, ZENQ-7 ZC702 (рисунок 1.3).

Рисунок 1.3 – Меню выбора платы

После создания проекта откроется основное окно рабочей среды (рисунок 1.4), состоящее из основных элементов: - Flow Navigator (если дословно – «навигатор потока») – навигация по этапам проектирования цифрового устройства; - Project Manager (менеджер проекта) – управление проектом (добавление ресурсов, IP-ядер, настройка); - «Подвал» – позволяет открыть консоль, сообщения об этапах компиляции.

Рисунок 1.4 – Рабочая среда Xilinx Vivado

Для дальнейшей работы необходимо создать модуль на VHDL или Verilog, который опишет работу проектируемого устройства. Для этого нажимаем кнопку «Add Sources» во «Flow Navigator». В появившемся окне из предложенных вариантов выбираем тип источника «Add or Create Design Sources». Далее, в окне, создаем новый модуль командой «Create File». В окне создания нового модуля (рисунок 1.5) выбираем имя и язык, на котором он будет написан.

Рисунок 1.5 – Окно создания нового модуля Для удобства можно сразу определить, какие входы и выходы есть у объекта, который мы будем описывать. Их можно определить в поле «I/O Port Definitions», окна «Define Module» (рисунок 1.6): Port Name – имя входа/выхода – порта; Direction – вход или выход (input/output); Bus – является ли порт шиной; MSB/LSB – старший/младший значащие разряды.

Рисунок 1.6 – Окно «Define Module» с настроенными «I/O Port Definitions»

Для того, чтобы перейти к редактированию модуля, надо дважды щёлкнуть левой кнопкой мыши по нему в разделе «Sources» менеджера проектов (Project Manager), справа откроется редактор кода (рисунок 1.7). В коде необходимо описать работу дешифратора. После служебного слова «module» идёт название самого модуля: «Decoder». В скобках указываются параметры: входящий сигнал А (трёхразрядная шина), входящий сигнал EN (разрешение работы), выходящий сигнал Х (семиразрядная шина). Блок «always @» указывает, что при определённом изменении входных сигналов необходимо делать то, что пойдёт дальше в скобках «begin-end». Если после оператора «always @» стоит «*», это означает, что работать блок будет при изменении любых сигналов. Внутри находится условный оператор: «if (<условие>) begin … end». А внутри условного оператора блок «case (<условие>) …», предполагающий более двух ветвлений.

Рисунок 1.7 – Редактор кода модуля

После того, как модуль написан, надо его сохранить. Для этого необходимо нажать кнопку «Save File». После этого автоматически пройдёт проверка файла на синтаксические ошибки.

Тестирование Далее нужно написать небольшой «Testbench» – ещё один модуль, который необходим для симуляции проекта. В нём мы зададим временные параметры, в которые происходят изменения сигналов. Важно: тестбенч не имеет входных и выходных параметров. После объявления модуля описываются переменные, с которыми работает тестбенч, затем объявляется объект класса «Decoder». После того, как тестбенч написан, можно снова сохранить файл и запустить поведенческую симуляцию по кнопке «Run Simulation» в разделе «Flow Navigator». На симуляции можно увидеть временные диаграммы (рисунок 1.8) тех сигналов, которые описаны в тестбенче. Это важный и обязательный этап проверки описанной схемы (описали модуль – описали схему). Те сигналы, которые состоят из нескольких «проводов» (являются шинами), можно развернуть, также можно регулировать масштаб временных диаграмм.

Рисунок 1.8 – Временная диаграмма работы модуля

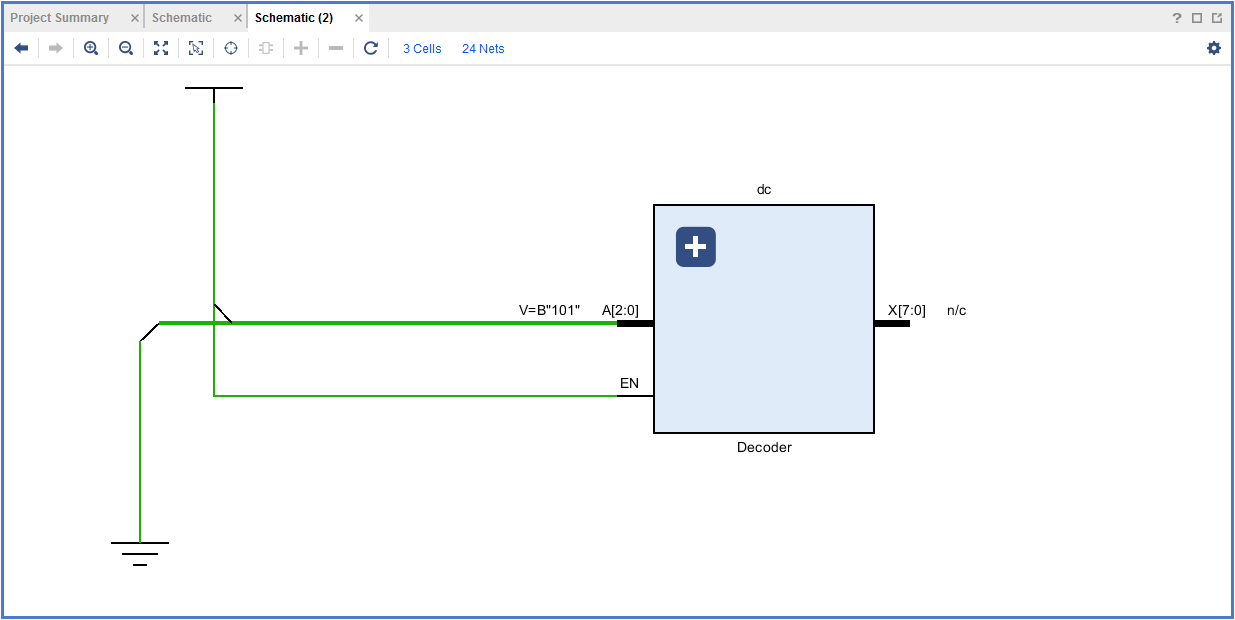

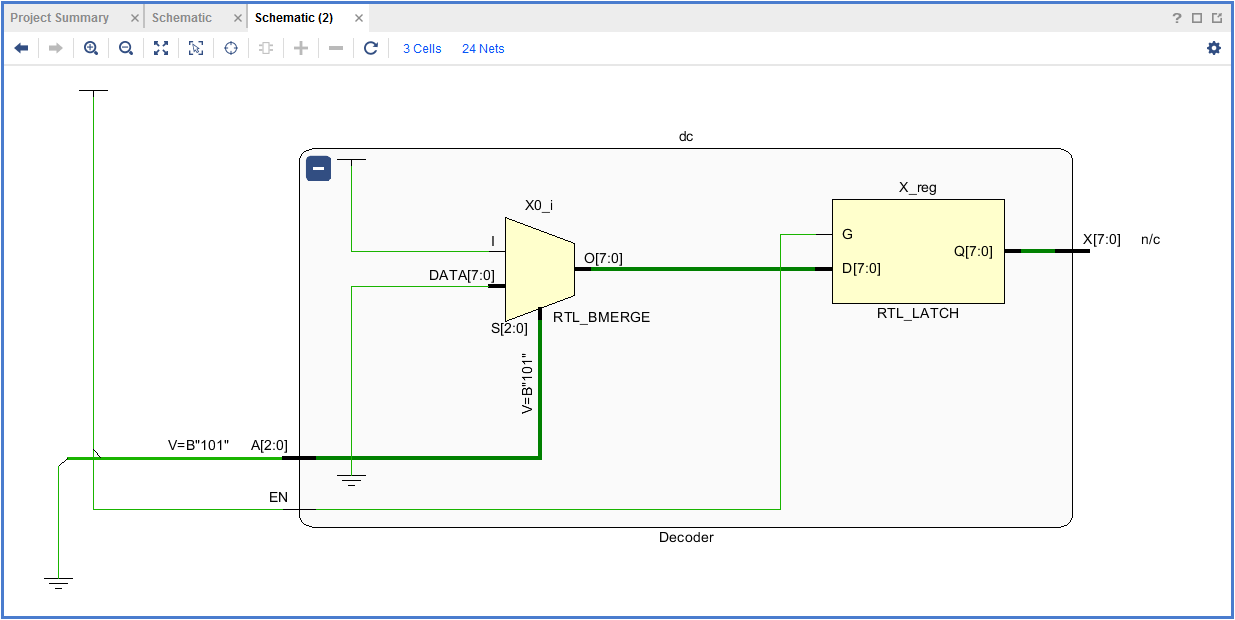

Также можно посмотреть, какую схему составил Vivado на основе написанного кода. Для этого в меню «Flow Navigator», в разделе «RTL Analysis» нажимаем «Schematic». Изначально, схема находится в свернутом состоянии, в виде блока, имеющего входы и выходы (рисунок 1.9). Для просмотра внутреннего строения блока (рисунок 1.10) нужно нажать на крестик в верхнем левом углу.

Рисунок 1.9 – Блок модуля

Рисунок 1.10 – Схема модуля на основе написанного кода

|

||||

|

Последнее изменение этой страницы: 2019-08-19; просмотров: 3108; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.23.101.75 (0.006 с.) |