Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Создание многоуровневого проекта в XIlinx ISE. Импорт из XIlinx ISE в XIlinx VIvadoСодержание книги

Поиск на нашем сайте Цель работы: научиться создавать иерархию источников в дереве проекта. Успешно произвести перенос проекта из Xilinx ISE в Xilinx Vivado. Задание: смоделировать в среде разработки Xilinx ISE устройство, которое передаст информацию, принятую по 8-ми разрядной шине, на вход интерфейса RS-232. Считать тактовую частоту равной частоте передачи информации. Обеспечить сброс хранилища памяти (буфера). Обеспечить возможность управления приёмом и передачей информации. После удачного моделирования импортировать проект в среду Xilinx Vivado.

Теоретические данные Xilinx ISE – САПР, с помощью которой можно проводить реализацию различных проектов на ПЛИС до 7-го поколения включительно. RS-232 (англ. Recommended Standard 232) – уровень асинхронного интерфейса. В настоящее время используется для устаревшего или специального оборудования, в данный момент вытеснен интерфейсом USB. Данный интерфейс обеспечивает передачу данных или каких-либо сигналов. На данный момент разъём имеется на некоторых персональных компьютерах, так как некоторые устройства используют или использовали RS-232, например, компьютерные мышки. Асинхронный интерфейс (UART) предполагает последовательную передачу данных по одному биту в строго определённый промежуток времени. Существует ряд общепринятых скоростей (биттрейтов), с которыми передаются данные: 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 921600 бит в секунду. Принято, что ждущим (неактивным) состоянием входа и выхода UART является логическая «1». Перед началом передачи информационной последовательности бит выдается сигнал о начале – стартовый бит, соответствующий логическому «0». После приёма стартового бита происходит приём ещё 9 бит (для 8-битных сигналов): 8 информационных и проверочный стоп-бит, соответствующий логической «1». В случае если стоп-бит оказывается неравен единице, UART фиксирует ошибку. В результате можно получить временную диаграмму, представленную на рисунке 2.1.

Рисунок 2.1 – Временная диаграмма

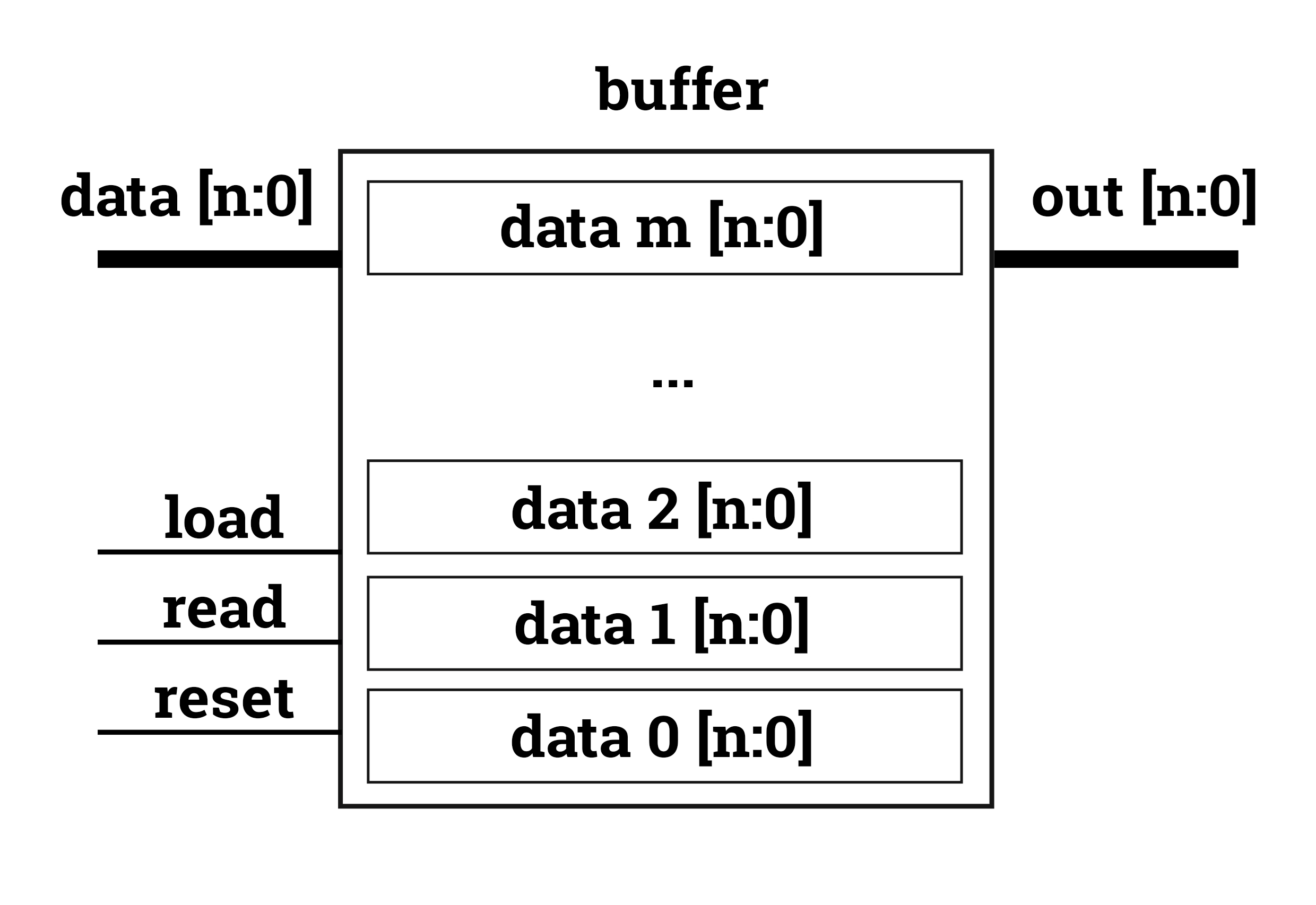

При передаче больших массивов информации важно обеспечить временное хранение данных. Для этого в информатике используется буфер. Часто буфер используется, если различны скорости приёма и передачи данных. На рисунке 2.2 изображён буфер, который может хранить m сигналов по n + 1 бит. Также в нём имеются входы сброса, загрузки и чтения: если на вход загрузки «load» приходит сигнал «1», буфер считывает информацию, приходящую по каналу «data», если на входе чтения «read» сигнал «1», то буфер выдаёт информацию на выход «out». При сбросе (на входе «reset» уровень «1») буфер очищается от информации.

Рисунок 2.2 – Пример буфера Буфер может быть организован по принципам FIFO (First In First Out) или LIFO (Last In First Out). В первом случае первый информационный блок, который в буфер вошёл, будет выдан первым при сигнале на чтение. А во втором на чтение будет выдан последний блок, вошедший в буфер.

|

||

|

Последнее изменение этой страницы: 2019-08-19; просмотров: 867; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.169 (0.008 с.) |