Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Создание и отладка проекта в среде разработки XIlinx VIvadoСодержание книги

Поиск на нашем сайте

СОДЕРЖАНИЕ СОДЕРЖАНИЕ.. 1 ВВЕДЕНИЕ.. 2 1 СОЗДАНИЕ И ОТЛАДКА ПРОЕКТА В СРЕДЕ РАЗРАБОТКИ XILINX VIVADO.. 3 1.1 Теоретические данные. 3 1.2 Создание проекта в Xilinx Vivado. 4 1.3 Тестирование. 9 2 СОЗДАНИЕ МНОГОУРОВНЕВОГО ПРОЕКТА В XILINX ISE. ИМПОРТ ИЗ XILINX ISE В XILINX VIVADO.. 12 2.1 Теоретические данные. 12 2.2 Создание проекта в Xilinx ISE.. 14 2.3 Тестирование. 17 2.4 Перенос проекта в Xilinx Vivado. 19 ЗАКЛЮЧЕНИЕ.. 21 СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ.. 22 ПРИЛОЖЕНИЕ А.. 23 ТЕКСТ ПРОГРАММЫ ДЕШИФРАТОРА.. 23 И ТЕСТОВОГО МОДУЛЯ.. 23 ПРИЛОЖЕНИЕ Б.. 25 ТЕКСТ ПРОГРАММЫ АСИНХРОННОГО.. 25 ИНТЕРФЕЙСА И ТЕСТОВОГО МОДУЛЯ.. 25

В настоящее время проектирование больших систем осуществляется с применением так называемых языков описания высокого уровня (Hardware Description Languages – HDL) VHDL и Verilog. Язык описания аппаратуры Verilog был разработан фирмой Gateway Design Automation в 1984 г. После поглощения последней фирмой Caddence язык получил широкое распространение среди разработчиков и стал не менее популярен, чем VHDL. В отличие от VHDL, структура и синтаксис которого напоминают такие «сложные» языки, как АДА или АЛГОЛ, Verilog обеспечивает более лаконичный и удобочитаемый синтаксис, характерный для очень популярного в среде программистов и разработчиков встроенных систем языка Си [1]. Vivado – САПР от компании Xilinx, предназначенная для создания цифровых устройств с применением языков высокого уровня. В данной лабораторной работе необходимо ознакомиться со средами программирования ПЛИС Xilinx Vivado и Xilinx ISE, в процессе создания модели дешифратора и интерфейса RS-232.

СОЗДАНИЕ И ОТЛАДКА ПРОЕКТА В СРЕДЕ РАЗРАБОТКИ XILINX VIVADO Цель работы: освоить среду разработки Xilinx Vivado. Разобрать пример с созданием дешифратора, его симуляцией, увидеть его схему. Разработать собственный проект в соответствии с заданием.

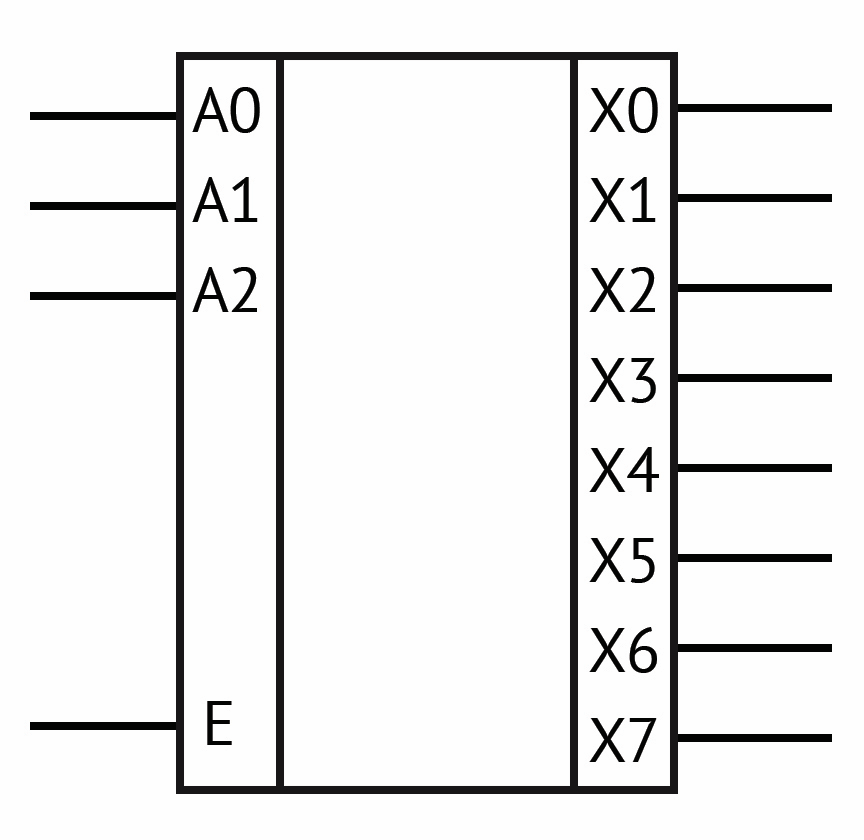

Теоретические данные Дешифратор (декодер) – устройство, преобразующее кодовую комбинацию, поступающую на входы, в сигнал на одном из выходов. В общем случае это устройство с m входами и n выходами, причём число выходов n = 2m. Как правило, входы обозначаются весами двоичных разрядов, а выходы нумеруются от 0 до n1. Условное графическое обозначение дешифратора представлено на рисунке 1.1.

Рисунок 1.1 – Условное графическое обозначение дешифратора

Работу дешифратора с тремя входами и восемью выходами можно представить следующей таблицей истинности (таблица 1.1).

Номер входного набора |

Входы |

Выходы | |||||||||||||||||||||||||||||||||||

| A2 | A1 | A0 | X7 | X6 | X5 | X4 | X3 | X2 | X1 | X0 | ||||||||||||||||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | |||||||||||||||||||||||||||

| 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | |||||||||||||||||||||||||||

| 2 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | |||||||||||||||||||||||||||

| 3 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | |||||||||||||||||||||||||||

| 4 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||

| 5 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||

| 6 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||

| 7 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | |||||||||||||||||||||||||||

Таблиц 1.1 – Таблица истинности для дешифратора

Тестирование

Далее нужно написать небольшой «Testbench» – ещё один модуль, который необходим для симуляции проекта. В нём мы зададим временные параметры, в которые происходят изменения сигналов. Важно: тестбенч не имеет входных и выходных параметров. После объявления модуля описываются переменные, с которыми работает тестбенч, затем объявляется объект класса «Decoder».

После того, как тестбенч написан, можно снова сохранить файл и запустить поведенческую симуляцию по кнопке «Run Simulation» в разделе «Flow Navigator». На симуляции можно увидеть временные диаграммы (рисунок 1.8) тех сигналов, которые описаны в тестбенче. Это важный и обязательный этап проверки описанной схемы (описали модуль – описали схему). Те сигналы, которые состоят из нескольких «проводов» (являются шинами), можно развернуть, также можно регулировать масштаб временных диаграмм.

Рисунок 1.8 – Временная диаграмма работы модуля

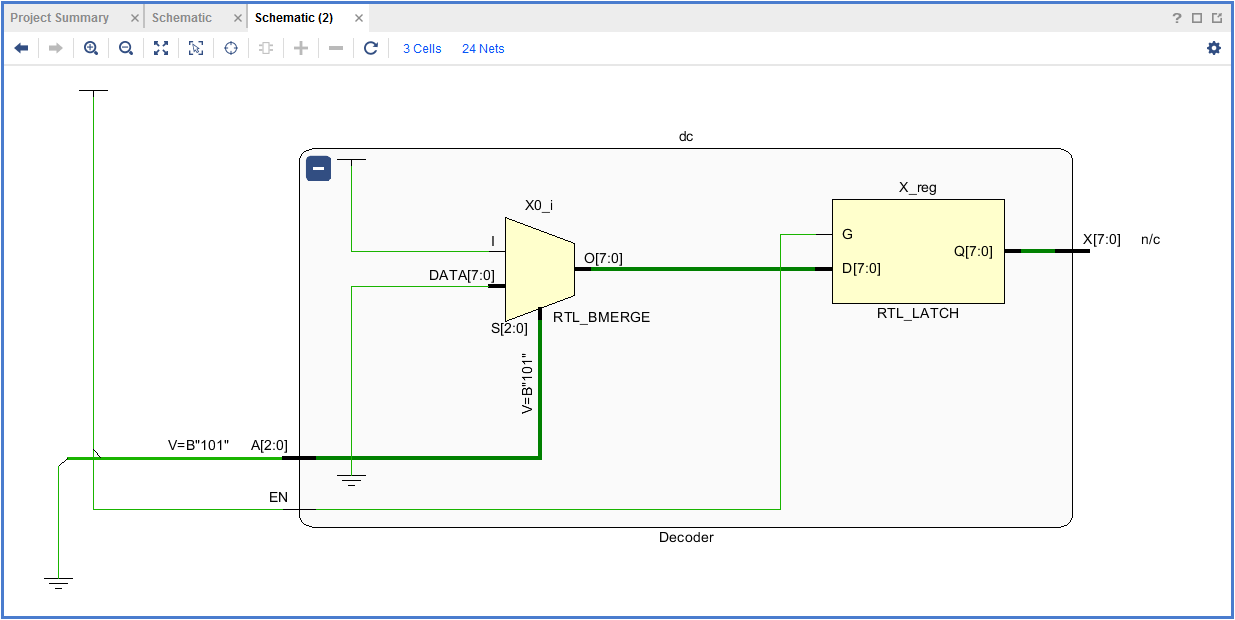

Также можно посмотреть, какую схему составил Vivado на основе написанного кода. Для этого в меню «Flow Navigator», в разделе «RTL Analysis» нажимаем «Schematic».

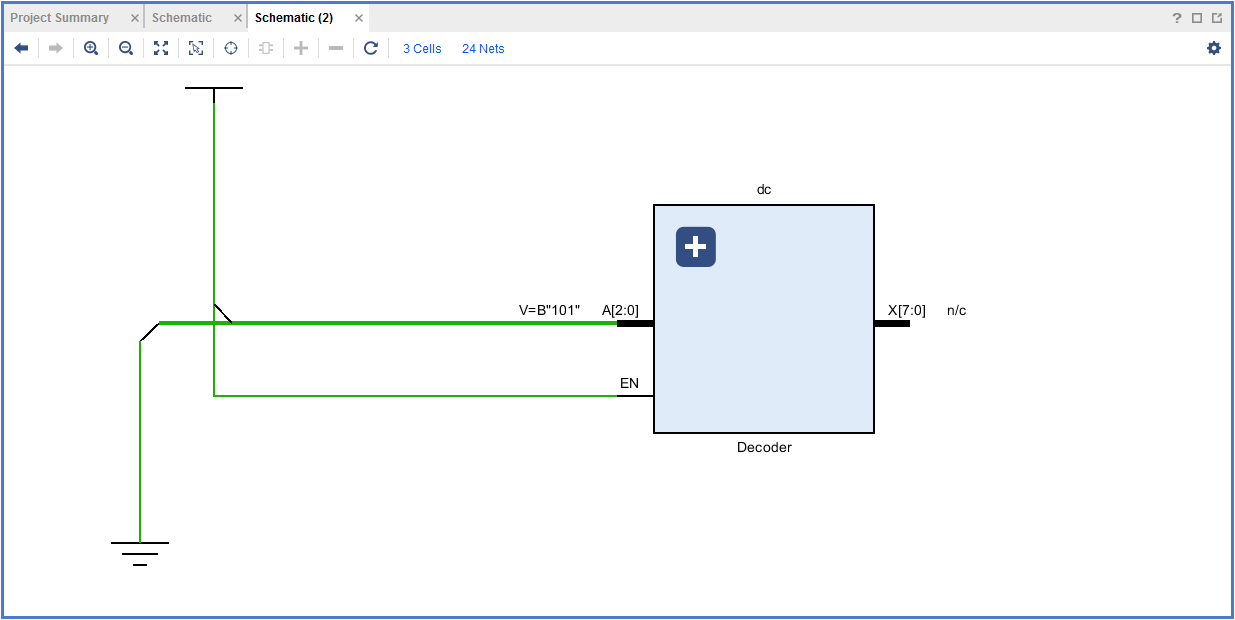

Изначально, схема находится в свернутом состоянии, в виде блока, имеющего входы и выходы (рисунок 1.9). Для просмотра внутреннего строения блока (рисунок 1.10) нужно нажать на крестик в верхнем левом углу.

Рисунок 1.9 – Блок модуля

Рисунок 1.10 – Схема модуля на основе написанного кода

Теоретические данные

Xilinx ISE – САПР, с помощью которой можно проводить реализацию различных проектов на ПЛИС до 7-го поколения включительно.

RS-232 (англ. Recommended Standard 232) – уровень асинхронного интерфейса. В настоящее время используется для устаревшего или специального оборудования, в данный момент вытеснен интерфейсом USB. Данный интерфейс обеспечивает передачу данных или каких-либо сигналов. На данный момент разъём имеется на некоторых персональных компьютерах, так как некоторые устройства используют или использовали RS-232, например, компьютерные мышки.

Асинхронный интерфейс (UART) предполагает последовательную передачу данных по одному биту в строго определённый промежуток времени. Существует ряд общепринятых скоростей (биттрейтов), с которыми передаются данные: 300, 600, 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 921600 бит в секунду.

Принято, что ждущим (неактивным) состоянием входа и выхода UART является логическая «1». Перед началом передачи информационной последовательности бит выдается сигнал о начале – стартовый бит, соответствующий логическому «0». После приёма стартового бита происходит приём ещё 9 бит (для 8-битных сигналов): 8 информационных и проверочный стоп-бит, соответствующий логической «1». В случае если стоп-бит оказывается неравен единице, UART фиксирует ошибку. В результате можно получить временную диаграмму, представленную на рисунке 2.1.

Рисунок 2.1 – Временная диаграмма

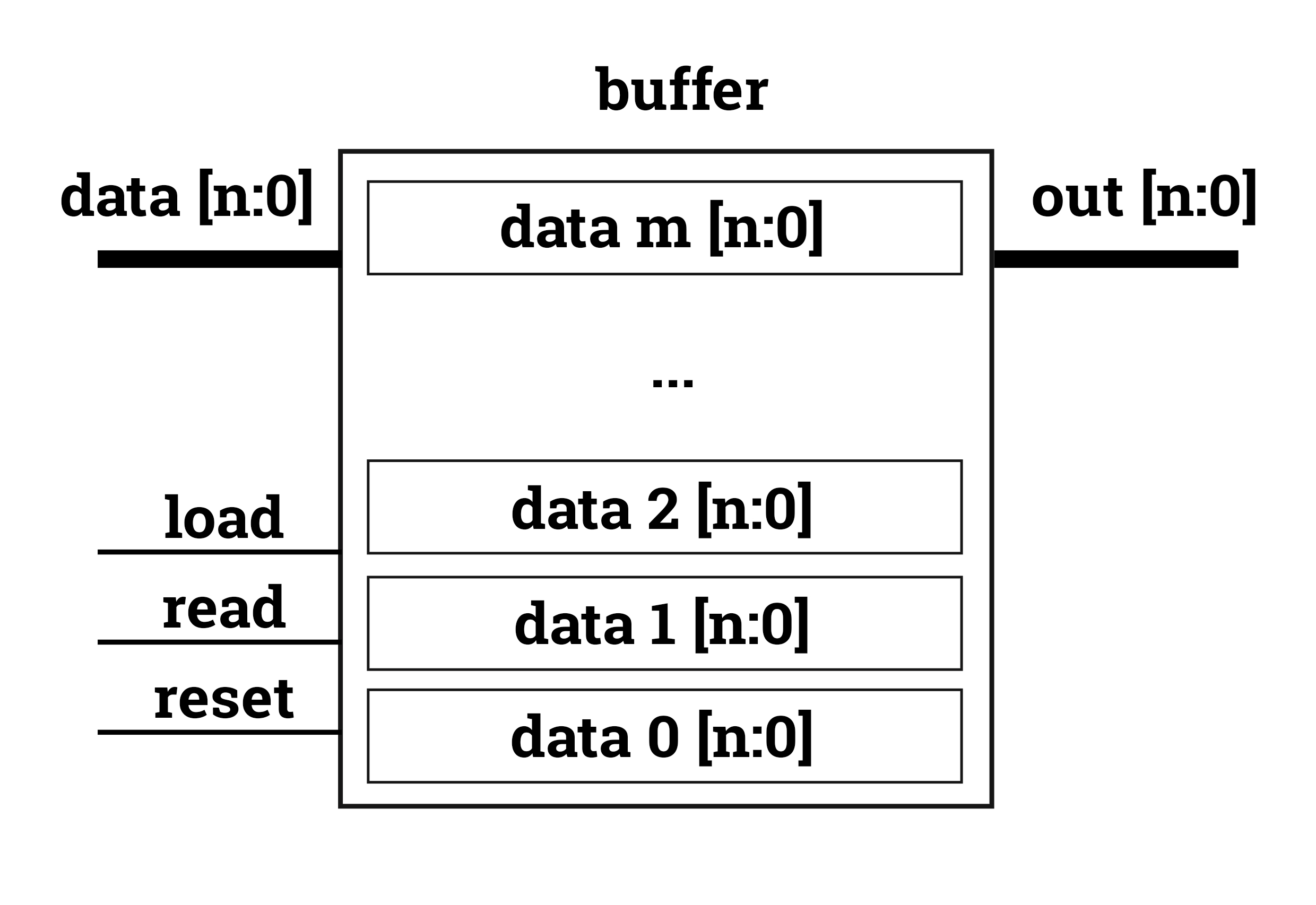

При передаче больших массивов информации важно обеспечить временное хранение данных. Для этого в информатике используется буфер. Часто буфер используется, если различны скорости приёма и передачи данных. На рисунке 2.2 изображён буфер, который может хранить m сигналов по n + 1 бит. Также в нём имеются входы сброса, загрузки и чтения: если на вход загрузки «load» приходит сигнал «1», буфер считывает информацию, приходящую по каналу «data», если на входе чтения «read» сигнал «1», то буфер выдаёт информацию на выход «out». При сбросе (на входе «reset» уровень «1») буфер очищается от информации.

Рисунок 2.2 – Пример буфера

Буфер может быть организован по принципам FIFO (First In First Out) или LIFO (Last In First Out). В первом случае первый информационный блок, который в буфер вошёл, будет выдан первым при сигнале на чтение. А во втором на чтение будет выдан последний блок, вошедший в буфер.

Тестирование

Для тестирования создается новый модуль. Алгоритм его создания ничем не отличается от создания рабочего модуля за одним не большим исключением: тип рекомендуется указывать «Verilog Test Fixture» (рисунок 2.9). В этом случае, в фале, сразу генерируется основной код тестового модуля.

Рисунок 2.9 – Меню создания тестового модуля

Затем, по требованию программы, привязываем тестовый модуль к верхнему модулю в дереве.

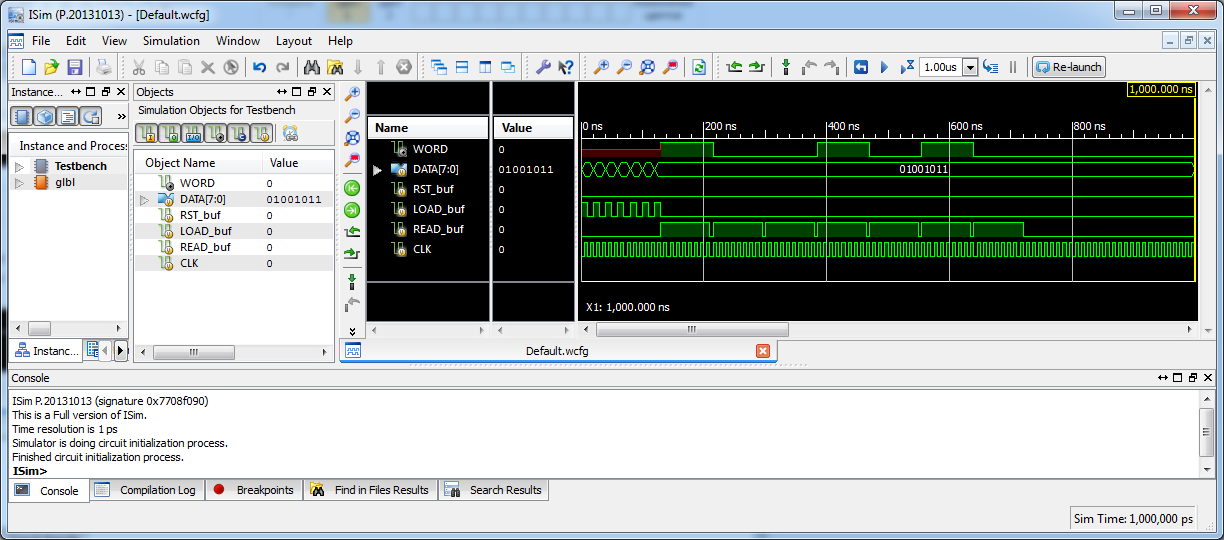

После того, как тестовый модуль написан, можно запустить симуляцию. Для этого, в разделе «Design» должен стоять флажок на пункте «Simulation», в разделе «Hierarchy» выделен тестовый модуль. После щелчка по пункту «Simulate Behavioral Model» из раздела «ISim Simulator» запуститься симуляция.

Симуляция проходит в несколько этапов. Сначала, всегда, запускается процесс проверки синтаксиса (Behavioral Check Syntax). Если ошибок не обнаружено происходит симуляция модели. В дополнение нужно сказать, что процесс проверки ошибок синтаксиса (Behavioral Check Syntax) можно запускать отдельно.

В результате появляется окно «ISim» (рисунок 2.10). В нем можно увидеть диаграмму входных и выходных сигналов. Также, в разделе «Instance and Process Name» можно увидеть другие сигналы, не попавшие на диаграмму. Чтобы увидеть уровень напряжения нужного сигнала, необходимо перетащить его на панель «Name».

Рисунок 2.10 – Окно результатов симуляции

ЗАКЛЮЧЕНИЕ

В ходе выполнения работы были изучены среды программирования Vivado и ISE от фирмы Xilinx.

С помощью САПР Vivado была построена модель работы дешифратора.

С помощью САПР ISE, была построена модель работы асинхронного интерфейса RS-232, состоящего из таких модулей, как: дешифратор, мультиплексор, счетчик, буфер. Затем, данный проект был импортирован в среду Xilinx Vivado.

Был получен ценный опыт написания тестовых модулей и проверки с их помощью работоспособности моделей, а также синтезирования готовых схем на основе готового кода.

ПРИЛОЖЕНИЕ А

ТЕКСТ ПРОГРАММЫ ДЕШИФРАТОРА

И ТЕСТОВОГО МОДУЛЯ

module Decoder _1(

input [2:0] A, //трехразрядная шина входа А

Begin

//только при разрешении работы

If (EN)

Begin

X =0; //обнулить шину

X [ A ]=1; //А-тому разряду положить "1"

End

End

Endmodule

module Testbench_1;

//!Тестбенч не имеет входных и выходных параметров.

//После объявления модуля описываются переменные

//с которыми работает тестбенч

reg [2:0] A;

reg EN;

wire [7:0] X;

//зетем объявляется объект класса decoder

Decoder _1 dc _1(A, EN, X);

Initial

Begin

A =2;//подача сигнала 2(010) на шину A

EN =1;//сигнал разрешения (или 0, или 1)

#5; // длительность сигнала (5 нс)

A=3;

#4;

A=7;

#9;

EN=0;

A=0;

#7

EN=1;

#6

A=5;

End

Endmodule

ПРИЛОЖЕНИЕ Б

Module Decoder(

input [2:0] A,//трехразрядная шина А

Begin

X =8' b 00000000; //Обнуление шины X (=0)

X [ A ] = 1;// проводу с номером А из шины X присвоить 1

End

Endmodule

Module Counter(

If(CE)

Begin

Q = Q +1;//увеличение числа на выходе

End

Endmodule

Module Multiplexer(

Output F //выход F

);

//объявление..

//входов/выходов,..

wire CLK;

wire CE;

wire [2:0] A;

wire [7:0] D;

//.., вспомогательных регистров, и..

wire [7:0] DD;

reg F;

//.., и включаемых модулей

Decoder DC _1(CLK, A, D);

//реакция на любое изменение входящих сигналов

always @*

//если нразрешена работа

If (CE)

Begin

F = D [ A ]&& DD [ A ];//подать на выход F сигнал с провода с номером A из шин D и DD

End

Endmodule

Module BuferFIFO(

Input RST,//вход сброса

Input READ,//вход чтения

input [7:0] DATA,//восьмиразрядная шина ввода данных DATA

output [7:0] OUT //восьмиразрядная шина вывода данных OUT

);

//объявление входов/выходов

wire RST;

wire LOAD;

wire READ;

wire [7:0] DATA;

reg [7:0] OUT;

//объявление вспомогательных регистров:

//счетного i

//памяти database

reg [3:0] i;

reg [7:0] database [6:0];

//начальная инициализация

//обнуление счетного регистра

//обнуление выходной шины

Initial

Begin

i=0;

OUT = 0;

End

//реакция на фронт сигналов READ,RST,LOAD

always @ (

Posedge READ or

Posedge RST or

Posedge LOAD)

Begin

//реакция на сброс

If (RST)

Begin

//очистка памяти через счетчик (каждый i-ый восьмиразрядный регистр

for(i=0; i<=6; i=i+1)

Begin

database[i] = 8'HXX;

End

End

Else

//реакция на загрузку

If(LOAD)

Begin

//запись данных в буфер

for(i=0; i<=6; i=i+1)

Begin

database[6-i] = database[6-(i+1)];

End

database[0]=DATA;

End

Else

//реакция на чтение

If(READ)

Begin

//выгрузка данных из буфера на шину дынных

OUT=database[6];

for(i=0; i<=6; i=i+1)

Begin

database[6-i] = database[6-(i+1)];

End

End

End

Endmodule

Module Transmitter(

input [7:0] DATA,//восьмиразрядная шина данных

input RST_buf,//сброс буфера

input LOAD_buf,// загрузка в буфер

input READ _ buf,//чтение из буфера

Endmodule

module Testbench;

//Входы (Inputs)

//объявление входов

reg [7:0] DATA;

reg RST_buf;

reg LOAD_buf;

reg READ_buf;

reg CLK;

//Выходы (Outputs)

//объявление выходов

wire WORD;

//объявление тестируемого модуля

//Instantiate the Unit Under Test (UUT)

Transmitter uut (

DATA(DATA),

.RST_buf(RST_buf),

.LOAD_buf(LOAD_buf),

.READ_buf(READ_buf),

CLK(CLK),

WORD(WORD)

);

//обнуление значений

Initial

Forever

Begin

#5;

CLK = ~CLK;

End

Initial

Begin

// Инициализация входов

DATA = 83;//подача даных для записи в буфер

RST _ buf = 0;//не очищать буфер

LOAD _ buf = 1;//загрузить в буфер данные с шины DATA

READ _ buf = 0;//отключение чтения из буфера

CLK = 0;//синхроимпуль в 0

#10;//подача сигнала в течение 10 нс

//ЗАПИСЬ В БУФЕР

LOAD _ buf =0;//отключить загрузку в буфер

#10;;//подача сигнала в течение 10 нс

LOAD _ buf =1;//включить загрузку в буфер

DATA = 80;//подача данных для записи в буфер числа 80

#10;;//подача сигнала в течение 10 нс

LOAD_buf = 0;

#10;

LOAD_buf = 1;

DATA = 65;

#10;

LOAD_buf = 0;

#10;

LOAD_buf = 1;

DATA = 82;

#10;

LOAD_buf = 0;

#10;

LOAD_buf = 1;

DATA = 84;

#10;

LOAD_buf = 0;

#10;

LOAD_buf = 1;

DATA = 65;

#10;

LOAD_buf = 0;

#10;

LOAD_buf = 1;

DATA = 75;

#10;

//ЧТЕНИЕ ИЗ БУФЕРА

LOAD_buf = 0;

READ_buf = 1;

#80;

READ_buf = 0;

#5;

READ_buf = 1;

#80;

READ_buf = 0;

#5;

READ_buf = 1;

#80;

READ_buf = 0;

#5;

READ_buf = 1;

#80;

READ_buf = 0;

#5;

READ_buf = 1;

#80;

READ_buf = 0;

#5;

READ_buf = 1;

#80;

READ_buf = 0;

#5;

READ_buf = 1;

#80;

READ_buf = 0;

#100;

End

Endmodule

СОДЕРЖАНИЕ

СОДЕРЖАНИЕ.. 1

ВВЕДЕНИЕ.. 2

1 СОЗДАНИЕ И ОТЛАДКА ПРОЕКТА В СРЕДЕ РАЗРАБОТКИ XILINX VIVADO.. 3

1.1 Теоретические данные. 3

1.2 Создание проекта в Xilinx Vivado. 4

1.3 Тестирование. 9

2 СОЗДАНИЕ МНОГОУРОВНЕВОГО ПРОЕКТА В XILINX ISE. ИМПОРТ ИЗ XILINX ISE В XILINX VIVADO.. 12

2.1 Теоретические данные. 12

2.2 Создание проекта в Xilinx ISE.. 14

2.3 Тестирование. 17

2.4 Перенос проекта в Xilinx Vivado. 19

ЗАКЛЮЧЕНИЕ.. 21

СПИСОК ИСПОЛЬЗОВАННЫХ ИСТОЧНИКОВ.. 22

ПРИЛОЖЕНИЕ А.. 23

ТЕКСТ ПРОГРАММЫ ДЕШИФРАТОРА.. 23

И ТЕСТОВОГО МОДУЛЯ.. 23

ПРИЛОЖЕНИЕ Б.. 25

ТЕКСТ ПРОГРАММЫ АСИНХРОННОГО.. 25

ИНТЕРФЕЙСА И ТЕСТОВОГО МОДУЛЯ.. 25

| Изм. |

| Лист |

| № докум. |

| Подпись |

| Дата |

| Лист |

| 2 |

| Разраб. |

| Кузнецов А.В. |

| Провер. |

| Орлов В.П. |

| Н. Контр. |

| Зав.каф. |

| Описание прибора на языке Verilog |

| Лит. |

| Листов |

| 31 |

| ИВЗО ППБЗ-01-15 |

В настоящее время проектирование больших систем осуществляется с применением так называемых языков описания высокого уровня (Hardware Description Languages – HDL) VHDL и Verilog. Язык описания аппаратуры Verilog был разработан фирмой Gateway Design Automation в 1984 г. После поглощения последней фирмой Caddence язык получил широкое распространение среди разработчиков и стал не менее популярен, чем VHDL.

В отличие от VHDL, структура и синтаксис которого напоминают такие «сложные» языки, как АДА или АЛГОЛ, Verilog обеспечивает более лаконичный и удобочитаемый синтаксис, характерный для очень популярного в среде программистов и разработчиков встроенных систем языка Си [1].

Vivado – САПР от компании Xilinx, предназначенная для создания цифровых устройств с применением языков высокого уровня.

В данной лабораторной работе необходимо ознакомиться со средами программирования ПЛИС Xilinx Vivado и Xilinx ISE, в процессе создания модели дешифратора и интерфейса RS-232.

СОЗДАНИЕ И ОТЛАДКА ПРОЕКТА В СРЕДЕ РАЗРАБОТКИ XILINX VIVADO

Цель работы: освоить среду разработки Xilinx Vivado. Разобрать пример с созданием дешифратора, его симуляцией, увидеть его схему. Разработать собственный проект в соответствии с заданием.

Теоретические данные

Дешифратор (декодер) – устройство, преобразующее кодовую комбинацию, поступающую на входы, в сигнал на одном из выходов. В общем случае это устройство с m входами и n выходами, причём число выходов n = 2m. Как правило, входы обозначаются весами двоичных разрядов, а выходы нумеруются от 0 до n1. Условное графическое обозначение дешифратора представлено на рисунке 1.1.

Рисунок 1.1 – Условное графическое обозначение дешифратора

Работу дешифратора с тремя входами и восемью выходами можно представить следующей таблицей истинности (таблица 1.1).

Номер входного набора

Входы

Выходы

Таблиц 1.1 – Таблица истинности для дешифратора

|

| Поделиться: |