Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Конфігурування пристроїв SCSIСодержание книги

Поиск на нашем сайте

При конфігуруванні пристроїв (програмно або джамперами) необхідно встановити наступні параметри: - Ідентифікатор пристрої (SCSI ID) - унікальний для кожного пристрою адресу на шині з діапазону 0-7 (для Wide SCSI 0-15). Позиційний код, що використовується для адресації, забезпечує сумісність адресації 8 - і 16-бітних пристроїв на одній шині. Ряд версій BIOS вважає завантажувальним тільки пристрій з SCSI ID = 0. - Контроль паритету. Якщо хоча б один пристрій не підтримує контроль паритету, він повинен бути відключений для всіх пристроїв на шині. - Включення термінаторів. У сучасних пристроях застосовуються активні термінатори, які можуть включатися одним джампером або програмно-керованим сигналом. Термінатори повинні включатися тільки на крайніх пристроях в ланцюжку. Сучасні хост-адаптери дозволяють автоматично включати свій термінатор, якщо вони є крайніми, і відключати, якщо використовуються внутрішній і зовнішній роз'єм каналу. Це дозволяє підключати та відключати зовнішні пристрої, не піклуючись про перемикання термінаторів. - Харчування термінаторів. Коли використовуються активні термінатори, необхідно включити живлення термінаторів хоча б на одному пристрої. - Узгодження швидкості синхронного обміну. Режим синхронного обміну включається за взаємною згодою пристроїв. Якщо хоча б один пристрій на шині його не підтримує, рекомендують заборонити узгодження на хост-адаптер. Якщо обмін буде ініційовано цільовим пристроєм, що підтримує синхронний режим, хост-адаптер підтримає цей режим. Цільовим пристрою можна заборонити запит синхронного режиму спеціальним джампером. - Дозвіл відключення дозволяє пристроям відключатися від шини при неготовності даних під час тривалих операцій з носієм, що досить ефективно в багатозадачному режимі при декількох ПУ на шині. - Узгодження ширини шини даних виконується за протоколом шини, виходячи з можливостей обох учасників обміну. Цільовим пристрою можна заборонити запит 16-бітного режиму спеціальним джампером. - Заборона] 6-розрядного режиму дозволяє підключити 16-бітове пристрій до 8-бітної шині. - Примусове переключення в лінійний режим дозволяє перевести пристрій LVD в режим SE. - Заборона синхронізації по обох фронтах дозволяє примусово перевести пристрій Ultra3 в режим Ultra2.

- Старт по команді або заборона автоматичного запуску шпиндельного двигуна пристрою. При включенні цієї опції запуск двигуна пристрою виконується тільки по команді від хост-адаптера, що дозволяє знизити пік навантаження блока живлення в момент включення. Хост буде запускати пристрої послідовно. - Затриманий старт в поєднанні з джамперами вибору затримок дозволяє автоматично запускати двигун через вказаний інтервал після подачі живлення (різним пристроям задають різні значення затримок). Конфігурування хост-адаптерів з точки зору шини SCSI не відрізняється від конфігурації інших пристроїв. Для сучасних адаптерів замість джамперів використовується програмне конфігурування. Як і всяка карта розширення, хост-адаптер повинен бути налаштований і з боку системної шини розширення, до якої він підключається. Системні ресурси для SCSI-адаптера включають: - Область пам'яті для розширення ROM BIOS, необхідного для підтримки конфігурування пристроїв і дискових функцій; - Область розділяється буферної пам'яті; - Область портів вводу-виводу; - Лінія запиту переривання (IRQ); - Канал DMA. Всіх пристроїв SCSI потрібні спеціальні драйвери. Базовий драйві дискових пристроїв входить в BIOS хост-адаптера. До однієї шині SCSI можна підключати різнотипні пристрої різних поколінь, 8 - і 16-бітові. При підключенні до однієї шині пристроїв LVD і SE, всі пристрої перейдуть у режим SE і шина не зможе працювати в режимі Ultra2, властивому пристроїв LVD. Якщо на шині присутні пристрої ШгаІбО і Ultra2 (або ще нижче), то шина буде працювати в найнижчому з цих режимів. У шині SCSI завжди потрібна установка термінаторів, які повинні бути узгоджені за импедансу з кабелем і встановлюються на кінцях фізичних ліній. У SCSI-1 застосовуються пасивні термінатори з імпедансом 132 Ом. Кожна сигнальна лінія з'єднується резистором 330 Ом з шиною GND і 220 Ом з шиною +5 В. На частоті 20 МГц в SCSI-2 використовуються активні термінатори з імпедансом 110 Ом. Вони мають джерело опорної напруги (стабілізатор), і кожна сигнальна лінія з'єднується резистором 110 Ом з виходом цього джерела.

У високошвидкісних версіях інтерфейсу використовуються FPT (Forced Perfect Terminator) термінатори - покращений варіант активних термінаторів з обмежувачами викидів. Для живлячи активних

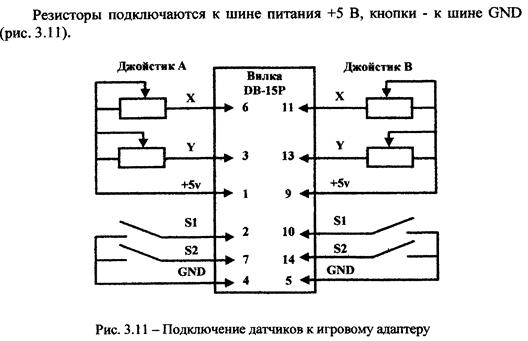

термінаторів в шині передбачені спеціальні лінії ТегтР \ КК. По виконання термінатори можуть бути як внутрішні (розміщені на друкованій платі пристрою), так і зовнішні (що встановлюються на роз'єми кабелю або пристрою). Ігровий адаптер Game-порт Інтерфейс ігрового адаптера займає дозволяє вводити значення дискретних (4 біти) і аналогових сигналів (величини опір 4 резисторів). Спочатку порт був призначений для підключення джойстиків і інших ігрових пристроїв введення, але він може застосовуватися і для підключення інших датчиків. Метод вимірювання опору заснований на програмному визначенні тривалості імпульсу, пропорційній величині опору. Перетворення починається з виведення будь-якого байта в регістр адаптера (201Ь), при цьому біти 0-3 встановлюються в одиничні значення. Час вимірюється до повернення в нульове стан біт 0-3, відповідних чотирьом аналоговим каналам. Якщо аналоговий вхід закорочений на шину ВМ) або ланцюг вимірюваного опору розірвана, відповідний біт не обнулиться ніколи (до апаратного скидання комп'ютера). Тому щоб уникнути зависання в програмі перетворення повинен бути передбачений механізм тайм-ауту. Для вимірюваних опорів в діапазоні 0-100 кОм час визначається за формулою Т (мкс) = 24,24-11 * И (кОм). Звичайно, точність і лінійність перетворення невисока, перетворення виконується не швидко (до 1,12 мс) і сильно завантажує процесор. Однак, на відміну від «справжніх» аналого-цифрових перетворювачів, цей перетворювач дістається даром - ігровий адаптер входить до складу практично всіх комбінованих плат послідовних і паралельних портів (Мультикарта) і звукових карт. Порт має роз'єм-розетку ОВ-158, призначення висновків і відповідність сигналів бітам регістру наведено в табл. 3.13.

Замикання кнопок відповідають нулі в бітах 5-7. При необхідності аналогові канали можна використовувати і для дискретного вводу, якщо їх входи підключити до кнопок, що замикає їх на щіну GND, і до резисторам, «підтягує» їх до рівня + 5 В. Два джойстика (А і В) підключаються через Y-подібний перехідник-разветвитель. На звукових картах через роз'єм «Game» разом з джойстиками можуть підключатися і зовнішні MIDI-пристрої через спеціальний кабель-адаптер, що забезпечує гальванічну розв'язку вхідного сигналу і обмеження вихідного струму (див. рис. 3.11). Для інтерфейсу MIDI використовуються контакти 12 і 15, раніше призначалися для шин GND і +5 V. Таке призначення робить безпечним підключення адаптера MIDI до "чистого" ігровому порту і звичайного джойстика до ігрового порту з сигналами MIDI.

Відеоадаптери При розвитку відеосистем ПК використовувалися наступні види відеоадаптерів. Монохромний MDA. Адаптер монітора розроблений на базі контролера дисплея Motorola 6845. Забезпечував роботу монохромного дисплея в текстовому режимі, використовував відеобуфер обсягом 4К статичної ОЗУ і вбудований генератор символів. Параметри розгортки задаються через 18 програмно доступних в просторі введення / виводу регістрів (індекс-порт 3B4h, запис / читання даних - порт 3B5h). Кольоровий графічний адаптер CGA. У CGA адаптері контролер також реалізований на мікросхемі 6845, тому способи програмування регістрів МДА і CGA однакові, проте при установці відеорежиму змінюються адреси портів (для монохромного 3B4h/3B5h для кольорового 3D4h/3D5h).

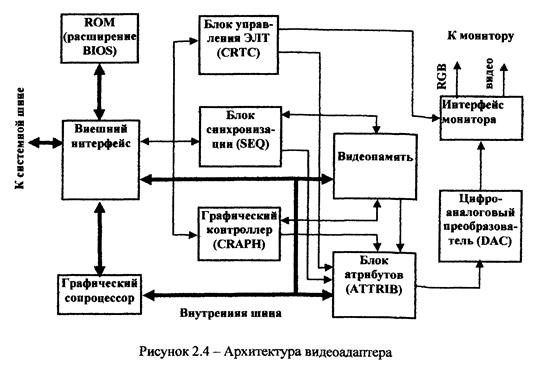

Розширений графічний адаптер EGA. В адаптері EGA сформувалася архітектура (набір блоків та їх відображення на адресний простір введення / виводу) яка з невеликими доповненнями (див. нижче) є стандартною для сучасних відеоадаптерів. Адаптер EGA фірми IBM забезпечує можливість роботи в різних відеорежимах спільно з кольоровими або монохромними моніторами з цифровими входами. В архітектурі EGA виділилися такі блоки: I) Блок управління електронно-променевою трубкою (CRTC - CRT Controller) управляє сигналами горизонтальної та вертикальної синхронізації, початковим адресою виведення в відеобуфері, положенням і формою курсора і ін Оскільки адаптер EGA може формувати растр, що містить більше 256 рядків розгортки, деякі регістри CRT повинні мати 9 біт. Проте всі регістри блоку 8-бітові, а старше за дев'ять біти зібрані в регістр переповнення. 2) Блок синхронізації (SEQ - Sequencer) генерує тактові сигнали і сигнали для синхронізації доступу до відеопам'яті. Блок забезпечує доступ до відеопам'яті з боку процесора у спеціально виділені проміжки часу, вільні від процесу регенерації зображення на екрані дисплея. У цьому ж блоці містяться регістри управління записом даних у бітові площині. 3) Графічний контролер (CRAPH - Graphics Controller) в графічних режимах направляє дані з пам'яті в контролер атрибутів і в процесор. Для швидкої зміни зображення на екрані дисплея апаратурою забезпечується можливість запису 32 біт даних за один цикл пам'яті (8 біт для кожної площини), а додаткова логіка дозволяє процесору записувати дані в відеопам'ять не дотримуючись меж байтів. 4) Контролер атрибутів (ATTR1B - Attribute controller) встановлює колірну палітру з 16 кольорів, кожен з яких може бути визначений незалежно від інших кольорів. На вхід монітора подається 6-ти бітовий код кольору. Цією ж мікросхемою виконуються дії з управління мерехтінням і підкресленням. Контролер отримує дані з відеобуфера і перетворює їх в сигнали, що подаються на вхід монітора. Призначення регістрів перерахованих модулів адаптера разом з їх відображеннями на адресні порти і порти даних наведені в Додатку В. Починаючи з адаптера EGA, дня доступу до відеопам'яті з боку процесора виділено два сегменти адресного простору (BOOOOh - AFFFFh). З метою сумісності з більш ранніми моделями відеоадаптерів, адреси відеобуфера можуть змінюватися в залежності від встановленого водеорежіма (початковий адресу BOOOOh - монохромний текстовий режим, початкова адреса B8000h ~ кольоровий текстовий режим і початкова адреса AOOOOh - графічний режим).

Адаптер VGA. В адаптері VGA є всі перераховані вище блоки адаптера EGA, програмування яких аналогічно EGA. Для растрів 400 рядків і вище в регістри додано кілька полів зберігання десяти розрядів (див. П.2). Проте в адаптері VGA збільшено колірне дозвіл (до 256 кольорів в графічному режимі і до 218 кольорів при індексації кольорів за допомогою регістрів PEL). Збільшення колірного дозволу призвело до переходу на аналогове управлінні відеотерміналом (сигнал по кожній колірної складової R, G і В передається по одній лінії, а інформацію про інтенсивності складової несе амплітуда сигналу). Для реалізації аналогового управління (попередні адаптери MDA, CGA і EGA формують для управління монітором лише цифрові ТТЛ-сигнали) в адаптер VGA доданий вихідний блок цифро-аналогового перетворювача (Digital Analog Converter - DAC), зі своїми 256 восемнадцатьюразряднимі регістрами PEL. Адреси портів і особливості програмування регістрів PEL викладені в Додатку В. Адаптер SVGA, До даного класу відносяться адаптери сучасних ПК. Адаптер SVGA має весь набір стандартних регістрів VGA, але має поліпшеними характеристиками (роздільна здатність екрану і колірне дозвіл, обсяг відеопам'яті, підтримка VESA - режимів та ін.) Для управління додатковими можливостями адаптери SVGA мають набір додаткових програмно-доступних регістрів. На жаль набір додаткових регістрів не стандартизований і відрізняється у кожної фірми-виробника. Для своєї роботи адаптер SVGA вимагає''свій "драйвер, інакше його можливості обмежуються стандартним 256-кольоровим режимом VGA. Адаптери мають об'єм відеопам'яті, що перевищує виділене адресний простір, тому вони містять спеціальні регістри перемикання банків (що ускладнює програмне формування зображення). Сучасні адаптери SVGA мають можливість переадресації відеопам'яті в область старших адрес (вище кордону 16 Мбайт), що дозволяє в захищеному режимі працювати з цільними образами екранів. Крім апаратно-виділеної відеопам'яті, встановлюваної на графічних адаптерах, існує і архітектура уніфікованої пам'яті UMA (Unified Memory Architecture). При такому підході під відеобуфер виділяється область системного ОЗУ, що дозволяє дещо здешевити комп'ютер. Формування зображення у відеопам'яті графічного адаптера виробляється під керуванням програми, що виконується центральним процесором. Сама по собі завдання формування процесору цілком під силу, але при її вирішенні потрібно пересилання великого обсягу інформації в відеопам'ять, а для багатьох побудов ще і читання відеопам'яті з боку процесора. Відеопам'ять більшу частину часу зайнята видачею інформації схемами регенерації зображення в досить напруженому темпі. Від цього процесу вона вільна тільки під час зворотного ходу променя по рядку і кадру, але це менша частина часу. Якщо звернення до активної сторінці відеопам'яті з боку процесора відбувається під час прямого ходу і швидкодії схем адаптера недостатньо для того, щоб це звернення вписалося між сусідніми вибірками процесу регенерації, на екрані з'явиться штрих від не ліченої інформації пікселів. Якщо таке звернення відбувається часто, на екрані з'являється "сніг".

Виходів із цієї скрути є декілька. По-перше, підвищують швидкодію відеопам'яті. По-друге, розширюють розрядність шин графічного адаптера, причому як внутрішньої (шини відеопам'яті), так і інтерфейсної, і застосовують високопродуктивні шини (локальну УЬВ, РС1 або АВР). Розширення розрядності дозволяє за один цикл обігу передати більшу кількість біт даних - підвищити продуктивність. По-третє, підвищити швидкість відеопостроеній можна застосуванням кешування відеопам'яті або створення тіньової відеопам'яті. У цьому випадку при запису в область відеопам'яті дані будуть записані як у відеопам'ять, так і в ОЗУ (або навіть в кеш), а при зчитуванні з цієї області звернення буде тільки до швидкодіючому ОЗУ. І по-четверте, можна принципово скоротити обсяг інформації, переданої графічному адаптеру, але для цього графічний адаптер повинен містити графічний співпроцесор. У сучасних відеосистемах використовуються всі ці рішення. Графічні співпроцесори. Інтелектуальний графічний адаптер містить на своїй платі власний процесор, здатний формувати растрове зображення у відеопам'яті по командах, отриманими від центрального процесора. Команди орієнтуються на найбільш часто використовувані методи опису зображень, які будуються з окремих графічних елементів більш високого рівня, ніж пікселі. Команди малювання забезпечують побудову графічних примітивів (точки, відрізка прямої, прямокутника, дуги, еліпса). Примітиви такого типу в командах описуються у векторному вигляді, що набагато компактніше, ніж їх растровий образ. Таким чином, вдається значно скоротити обсяг переданої графічної інформації за рахунок застосування більш ефективного способу опису зображень. До командам малювання відноситься і заливка замкнутого, контуру, заданого в растровому вигляді, деяким кольором або візерунком. Вона прискорюється особливо ефективно: при програмної реалізації процесор повинен переглянути вміст відеопам'яті навколо заданої точки, рухаючись по всіх напрямах до виявлення кордону контуру і змінюючи колір пікселів на своєму шляху. При цьому потрібно читання великого обсягу даних відеопам'яті, їх аналіз та запис модифікованих даних назад у відеопам'ять. Процесор інтелектуального адаптера здатний виконати цю операцію швидко і не виходячи з цим потоком даних на зовнішню магістраль. Копіювання блоку з одного місця на інше екрана застосовується для "прокручування" зображення екрану в різних напрямках. Ця операція інтелектуальним адаптером може бути сильно прискорена. Для формування курсору на графічному екрані застосовують команди роботи зі спрайтами. Спрайт (Sprite) - невеликий прямокутний фрагмент зображення, який може переміщатися по екрану як єдине ціле. Апаратна підтримка вікон (Hardware Windowing) спрощує і прискорює роботу з екраном в багатозадачних (багатовіконних) системах. На традиційному графічному адаптері при наявності декількох, можливо перекривають один одного вікон програмі доводиться відслідковувати координати оброблюваних точок з тим, щоб не вийти за межі свого вікна. Апаратна підтримка вікон спрощує висновок зображень: кожній задачі виділяється своє вікно - область відеопам'яті необхідного розміру, в якому вона працює монопольно. Взаємне розташування вікон повідомляється інтелектуальному адаптера, і він для регенерації зображення синхронно з рухом променя по растру сканує відеопам'ять не лінійно, а перескакуючи з області пам'яті одного вікна на інше. Якщо обсяг відеопам'яті перевищує необхідний для даного формату екрану і глибини квітів, то в ній можна будувати зображення, що перевищує за розміром видиму частину. Інтелектуальному адаптеру можна доручити панорамування - відображення заданої області. При цьому горизонтальна і вертикальна прокрутка зображення не потребують операцій блокових пересилань - досить лише змінити покажчик початкової адреси відображуваної області. Вищеописані функції інтелектуального адаптера відносяться до двовимірної графіки (2D). Сучасні графічні адаптери беруть на себе і багато функцій побудови тривимірних зображень. У комп'ютерній графіці тривимірне зображення складається з ряду поверхонь різної форми. Ці поверхні "збираються" з окремих полігонів (трикутників), кожен з яких має тривимірні координати вершин і опис поверхні (колір, візерунок). Переміщення об'єктів (або спостерігача) призводить до необхідності перерахунку всіх координат і визначення видимості полігонів окремих перекриваються поверхонь. Крім того враховується перспектива, освітленість поверхонь і відображення світла від них, прозорість і багато факторів. Прискорення побудов в інтелектуальному адаптері забезпечується декількома чинниками. По-перше, це скорочення обсягу передачі по магістралі. По-друге, під час роботи процесора адаптера центральний процесор вільний, що прискорює роботу програм навіть в однозадачной режимі. По-третє, процесор адаптера, на відміну від центрального процесора орієнтований на виконання меншої кількості інструкцій, а тому здатний виконувати їх набагато швидше центрального. І по-четверте, швидкість обміну даних усередині адаптера може підвищуватися за рахунок кращого узгодження звернень до відеопам'яті з процесом регенерації зображення, а також за рахунок розширення розрядності внутрішньої шини даних адаптера. У сучасних графічних адаптерах широко застосовується двопортова відеопам'ять УКАМ і \ VRAM, а розрядність внутрішньої шини 64 біт (при 32-бітної зовнішньої шини) вважається нормою. На підході і адаптери з 128-розрядної внутрішньої шиною. Архітектура сучасних відеоадаптерів представлена на рис. 2.4

По відношенню до центрального процесора і оперативної пам'яті комп'ютера розрізняють графічні співпроцесори і акселератори. Графічний співпроцесор являє собою спеціалізований процесор з відповідним 'апаратним оточенням, який підключається до шини комп'ютера і має доступ до його оперативної пам'яті. В процесі своєї роботи співпроцесор користується оперативною пам'яттю, конкуруючи з центральним з доступу і до пам'яті і до шини. Графічний акселератор працює автономно і при вирішенні своєї задачі зі своїм великим обсягом даних може і не виходити на системну шину. Акселератори є вже традиційною складовою частиною практично всіх сучасних графічних адаптерів. Спеціально для потужних графічних адаптерів в 1996 році з'явився новий канал зв'язку з оперативною пам'яттю комп'ютера-АВР. Графічний акселератор є майстром шини АВР і може користуватися основною пам'яттю комп'ютера для своїх потреб при тривимірних побудовах.

90. Послідовний інтерфейс. СОМ-порт При послідовної зв'язку (Serial Interface і Serial Port) ПК посилає або приймає байти інформації побітно, тому для передачі даних в одну сторону використовується одна сигнальна лінія. Послідовна передача даних може здійснюватися як в асинхронному, так і в синхронному режимах. При асинхронної передачі біти передаються синхронно, а байти асинхронно (старт - стопного передача). Сигнал на лінії може бути високого або низького рівня, що відповідає логічному нулю або одиниці, і кажуть, що лінія відзначена (marking), коли рівень високий, і порожня (spacing), коли рівень низький. Лінія підтримується в зазначеному стані, коли по ній немає передачі даних. При початку передачі байта даних сигнал падає в О, відзначаючи стартовий біт. Потім слідують вісім бітів даних (іноді менше) у вигляді набору високих і низьких рівнів. Останній біт даних може супроводжуватися бітом парності, використовуваним для виявлення помилок, а потім у послідовність включаються 1 або більше стоп-бітів, яким відповідає високий рівень. Ці стоп-біти починають зазначене стан, який буде зберігатися доти, поки не почнеться передача наступного байта даних; число використовуваних стоп-бітів істотно, оскільки вони встановлюють мінімальний час, який має пройти перед наступним стартовим бітом. На рис. 3.1 показана ця послідовність.

Звичайно, передає і приймальня станції повинні використовувати один і той же протокол для цих ланцюжків бітів і вони повинні працювати з однією і тією ж швидкістю обміну (вимірюваної в бітах в секунду). Для асинхронного режиму прийнятий ряд стандартних швидкостей обміну: 50, 75, 110, 150, 300, 600 1200, 2400, 4800, 9600, 19200, 38400, 57600 і 115200 біт / с. Внутрішній генератор синхронізації приймача використовує лічильник-дільник опорної частоти, обнуляє в момент прийому початку старт-біта. Цей лічильник генерує внутрішні строби, за якими приймач фіксує наступні прийняті біти. В ідеалі ці строби розташовуються в середині бітових інтервалів, що забезпечує можливість прийому даних і при деякому неузгодженості швидкостей приймача і передавача. Неважко помітити, що при передачі 8 біт даних, одного контрольного і одного стоп-біта гранично допустиме неузгодженість швидкостей, при якому дані будуть розпізнані вірно, не може перевищувати 5%. З урахуванням фазових спотворень (затягнутих фронтів сигналу) і дискретності роботи внутрішнього лічильника синхронізації реально допустимо менше відхилення частот. При обміні можуть легко виникати помилки, тому комунікаційне обладнання надає різноманітну інформацію про статус як самого порту, так і приєднаної до нього модему. Завданням модему є перетворення сигналу, що генерується портом комунікації, в акустичний сигнал, який може потім бути переданий по телефонному каналу. Більшість модемів надають також додаткові комунікаційні можливості, такі як автоматичний виклик і відповідь, які не підтримуються самим портом комунікації. Асинхронний обмін в PC реалізується за допомогою COM-порту з використанням протоколу RS-232C. Синхронний режим передачі передбачає постійну активність каналу зв'язку. Здійснення починається з сінхробайта, за яких впритул слід потік інформаційних біт. Якщо у передавача немає даних для передачі, він заповнює паузу посилкою байтів синхронізації безперервної. Очевидно, що при передачі великих масивів даних накладні витрати на синхронізацію в даному режимі обміну будуть нижчими, ніж в асинхронному. Однак у синхронному режимі необхідна зовнішня синхронізація приймача з передавачем, оскільки навіть мале відхилення частот призведе до швидко накопичується помилку і спотворення отриманих даних. Зовнішня синхронізація можлива або за допомогою окремої лінії для передачі сигналу синхронізації, або з використанням самосінхронізірующіхся кодування даних (наприклад, манчестерський код або NRZ), при якому на приймальній стороні з прийнятого сигналу можуть бути виділені і імпульси синхронізації. У будь-якому випадку синхронний режим вимагає або дорогах ліній зв'язку, або дорогого обладнання (а може, і того й іншого). Для ПК IBM PC існують спеціальні плати - адаптери SDLC (досить дорогі), що підтримують синхронний режим обміну. Вони використовуються в основному для зв'язку з великими машинами (mainframes) ЮМ і в даний час мало поширені.

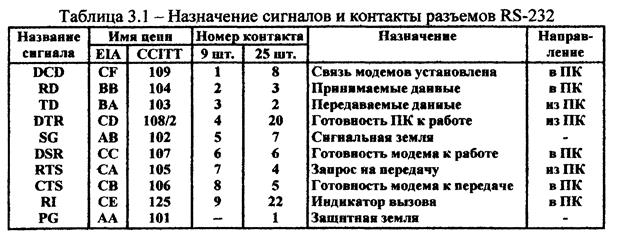

91. Програмна модель СОМ-порта Послідовна зв'язок настільки складна, що були розроблені спеціальні мікросхеми, що виконують роботу з перетворення паралельного коду в послідовний для передачі та зворотного перетворення при прийомі даних. Ці ж мікросхеми формують і обробляють синхроімпульси та управляючі сигнали інтерфейсу (управління та стан модему). Такі мікросхеми називають універсальним асинхронним приймачем-передавачем (universal asynchronous receiver transmitter або UART). IBM PC використовує UART сімейства 8250 фірми Intel (8250/16450/16550A). Це сімейство являє собою удосконалення початкової моделі, спрямовані на підвищення швидкодії, зниження споживаної потужності і завантаження процесора при інтенсивному обміні. У сучасних ПК і периферійному обладнанні, при інтенсивних обмінах на швидкостях 9600 біт / с і вище без втрати даних, застосовують UART типу 16550А, яка має 16-байтним FIFO-буфери прийому та передачі і можливість використання DMA (зазначених можливостей немає в базовій моделі 8250). Працює з цією мікросхемою забезпечує більшість універсальних мікросхем контролерів портів вводу / виводу, що входять в чіпсети сучасних системних плат. До складу IBM PC можуть входити до чотирьох послідовних інтерфейсів, що працюють у стандарті RS-232 (вітчизняний аналог - стик С2) та іменованих СОМ1 - COM4, (інтерфейси COM3 і COM4 підтримуються тільки в моделях PS / 2). Їм виділені наступні адреси в області портів вводу-виводу: СОМ1: 3F8h-3FFh COM3: 338h-33Fh COM2: 2F8h-2FFh COM4: 238h-23Fh Операційна система підтримує 2 порти комунікації, тому в ПК є 2 мікросхеми. Їх базові адреси зберігаються у клітинці 0040:0000 для СОМ1 і 0040:0002 для COM2 (2-х байтовий адреса порту, який є молодшим із групи адрес портів, що дають доступ до UART). Кожен інтерфейс пов'язаний з певним рівнем контролера переривань: СОМ1 викликає переривання IRQ4 (Int OCh); COM2 викликає переривання IRQ3 (Int OBh); COM3 і COM4 не мають стандартних векторів переривань. Кожен з пристроїв СОМ-порту є контролер, оснащений 25 - або 9 - штирьковим роз'ємом на задній стінці корпусу ПК. Цей роз'єм може використовуватися для підключення периферійних пристроїв (миші, графопостроителя тощо) або організації зв'язку між ПК. Контакти стику RS-232 мають наступні найменування (див. табл. 3.1).

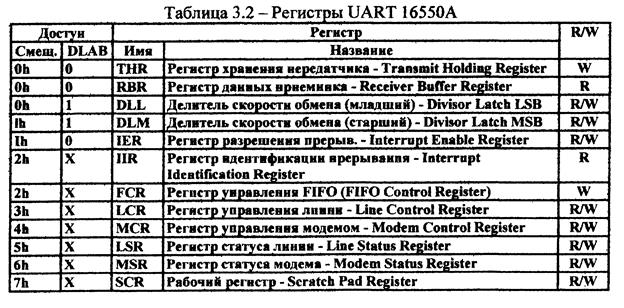

Контролер СОМ-порту є повністю програмованим пристроєм. Можна програмно задати наступні параметри обміну: кількість бітів даних і стоп-бітів, вид парності та швидкість обміну. Мікросхема іАЯТ 16550А має 12 програмованих однобайтних регістрів, за допомогою яких управляється і контролюється порт комунікації. Більшість з них займаються ініціалізацією порту. Доступ до цим 12 регістрів здійснюється через вісім адрес портів з номерами ЗР8Ь - (або 2Р8Ь - 2РЙ1). У п'яти випадках регістр, до якого організується доступ через даний порт, залежить від того, як встановлено біт 7 у регістрі управління лінії (т. зв. Біт ОЬАВ), який є єдиним регістром з адресою порту ЗРВ11. Призначення регістрів 16550А та їх відображення на адресний простір портів (зсув щодо базової адреси) представлено в табл. 3.2.

Нижче описано призначення регістрів. THR (регістр передавача) - сюди засилається байт для передачі. Дані, записані в цей регістр, будуть переслані в вихідний зсувний регістр (коли він буде вільний), з якого надійдуть на вихід за наявності дозволяючого сигналу CTS. Біт 0 передається (і приймається) першим. При довжині посилки менше 8 біт старші біти ігноруються. RBR (регістр приймача) - звідси зчитується прийнятий байт. Дані, отримані вхідним зрушуючим регістром, поміщаються в регістр RBR. Якщо до моменту закінчення прийому чергового символу попередній не був лічений з регістра RBR, фіксується помилка переповнення. При довжині посилки менше 8 біт старші (зайві) біти в регістрі мають нульове значення. DLL (регістр молодшого байта дільника частоти). Сюди засилається молодший байт дільника (див. DLM). DLM (регістр старшого байта дільника частоти). Дільник визначається за формулою D = 115200 / V, де V - швидкість передачі. Вхідна частота синхронізації 1,8432 МГц ділиться на заданий коефіцієнт, після чого виходить 16-кратна частота передачі даних. Наприклад, для швидкості 9600 бод дільник дорівнює 115200/9600 = 12 = 0Ch, тому потрібно вивести OCh в порт 3F8h і 0 в порт 3F9h. IER (регістр управління перериваннями). Одиничне значення біта дозволяє переривання. Призначення біт: 0: переривання по прийому символу (в режимі FIFO - переривання по тайм-ауту); 1: переривання по завершенню передачі символу; 2: переривання по обриву лінії або помилку в лінії; 3: переривання по зміні стану модему (обох лініях CTS, DSR, RI і DCD); 4-7: повинні бути 0. HR (регістр ідентифікації переривань і ознаки режиму FIFO). Коли відбувається переривання, тут міститься причина, що викликала його. Для спрощення програмного аналізу UART вибудовує внутрішні запити переривання по 4-рівневої пріоритетною системі. Порядок пріоритетів (за спаданням) наступний: стан лінії, прийом символу, звільнення регістру передавача і стан модема. При виникненні умови переривання UART вказує па джерело з вищим пріоритетом до тих пір, поки він не буде скинутий відповідної операцією. Тільки після цього буде виставлений запит з зазначенням такого джерела. Призначення біт: 0:1 - є не обслужених переривання, 0 - немає; 1-2: причина переривання: 0 - зміна стану модему (ліній CTS, DSR, RI або DCD); скидається читанням регістра стану модему; 1 - переданий символ; скидається записом символу в регістр передавача; 10 - прийнятий символ; скидається читанням приймача; 11 - помилка або обрив лінії; скидається читанням регістра стану лінії; 3: переривання по тайм-ауту (не в режимі FIFO); 4 - 5: не використовуються (повинні бути 0); 6-7: ознака режиму FIFO (11 - режим FIFO 16550А, 10 - режим FIFO 16550,00 - звичайний). FCR (регіструправленія FIFO). Призначення біт: 0: дозвіл (одиницею) режиму FIFO для передавача і приймача; 1: скидання лічильника FIFO-приймача (запис одиниці); 2: скидання лічильника FIFO-передавача (запис одиниці); 3: дозвіл операцій DMA (1 - дозволити); 4 - 5: зарезервовані; 6 - 7: рівень заповнення FIFO-буфера, при якому виробляється переривання (00 -1 байт, 01-4 байта, 10-8 байт, 11-14 байт). LCR (регістр управління лінією). Призначення біт: 0-1: число бітів даних (00 - 5, 01 - 6, 10 - 6,11 ~ 8); 2: число стоп-бітів (0 - 1, 1 - 1,5 при 5 бітах даних і 2 в протилежному випадку); 3-4: тип парності: Х0 - ні, 01 - непарна, 11 - парна; 5: постійна парність 0 - відміна постійної парності, 1 - постійна біт парності, залежить від бітів 3-4: біти 3-4 - 01 - біт парності завжди 1; біти 3-4 - 11 - біт парності завжди 0; біти 3 - 4 - Х0 - без біта парності; 6: 1 - імітувати обрив лінії (посилка нулів); 7: біт DLAB управління доступом до дільнику частоти (див. табл. 3.2). MCR (Регістр управління модемом). Призначення біт: 0: 1 - встановити вихід DTR; 1:1 - встановити вихід RTS; 2: 1 - встановити OUT1 (не використовується); 3:1 - встановити OUT2 (дозволити переривання OTRS-232); 4: 1 - діагностичний режим, в якому всередині UART організується внутрішня "заглушка". Вихід передавача переводиться в стан балка. 1, вхід приймача відключається, вихід зрушується регістру передавача логічно з'єднується з входом приймача, входи DSR, CTS, RI і DCD відключаються від вхідних ліній, на них внутрішньо подаються сигнали DTRC, RTSC, OUT 1C, IE, виходи управління модемом переводяться в пасивний стан (лог. 0). При цьому передані дані в послідовному вигляді негайно приймаються, що дозволяє перевіряти внутрішній канал даних порту (включаючи зсувні регістри) і відпрацювання переривань, а також визначити швидкість роботи UART; 5 - 7: повинні бути 0. LSR Регістр стану лінії. Біти 1-4 викликають переривання помилково, якщо воно дозволено. Призначення біт: 0: 1 - байт даних отриманий; 1: 1 - отримані дані були перезаписані (попередній символ не був вчасно лічений); 2:1 - помилка парності (імовірно, через шум в лінії); 3:1 - невірний стоп-біт (передача не синхронізовані); 4: 1 - виявлений обрив лінії (вхід приймача знаходиться в стані лог. 0 не менше, ніж час посилки символу.); 5: 1 - регістр зберігання передавача порожній (у режимі. FIFO вказує на відсутність символів в FIFO-буфері); 6: 1 - регістр передавача порожній (немає даних для передачі ні в сдвиговом регістрі, ні в буферних, THR або FIFO); 7: 1 - помилка прийнятих даних в режимі FIFO (буфер містить хоч один символ, прийнятий з помилкою формату, паритету чи обривом). У не-FIFO режимі завжди 0. У режимі FIFO ознаки помилок зберігаються в FIFO-буфері разом з кожним символом. У регістрі, вони встановлюються (і викликають переривання) в той момент, коли символ, прийнятий з помилкою, знаходиться на вершині FIFO (перший в черзі на зчитування). У разі обриву лінії в FIFO заноситься тільки один "обривного" символ, і UART чекає відновлення і подальшого старт-біта. Зазвичай регістр постійно проглядається в процесі комунікаційного обміну. При передачі даних регістр повідомляє, що попередній символ уже посланий, дозволяючи програмі записати новий символ поверх його. При прийомі даних регістр інформує програму про надходження наступного символу з тим, щоб програма могла прочитати його перш ніж він буде знищений наступним прибулим. MSR (регістр стану модему). Біти 0-3 викликають переривання по зміні стану модему, якщо воно дозволено. Призначення біт: 0:1 - змінився стан лінії CTS; 1:1 - змінився стан лінії DSR; 2: 1 - змінився стан лінії RI; 3:1 - змінився стан лінії DCD; 4: - поточний стан лінії CTS; 5: - поточний стан лінії DSR; 6: - поточний стан лінії RI; 7: - поточний стан лінії DCD. Примітка: "Змінилося стан лінії..." означає, що дана лінія RS-232 змінила свій стан в порівнянні з останнім читанням цього регістра. SCR (робочий регістр), на роботу UART не впливає, призначений для тимчасового зберігання даних (у 8250 відсутня).

92. Програмування послідовного зв’язку З дванадцяти регістрів тільки шість необхідні для простого послідовного зв'язку. Регістр зберігання передавача містить байт даних, які будуть надіслані, а регістр даних приймача - останній отриманий байт даних. Регістри управління і статусу лінії ініціалізують і управляють лінією зв'язку, використовуючи швидкість обміну, що міститься в двох регістрах дільника швидкості обміну. З решти регістрів регістри управління та статусу модему використовуються тільки для зв'язку через модем, регістр управління FIFO-буфером при його використанні, а два регістри, пов'язаних з перериваннями використовуються тільки в процедурах, керованих перериваннями. Переривання використовуються при зв'язку з метою ефективності. Звичайна комунікаційна процедура безупинно перевіряє регістр статусу лінії, очікуючи вводиться символу або вказівки, що все готово для передачі наступного байта даних. Оскільки процесор працює набагато швидше, ніж звичайні швидкості з якими передаються послідовні дані, то цей метод дарма витрачає процесорний час, який може використовуватися для обробки вступників або переданих даних. З цієї причини мікросхема UART може бути встановлена в режим, що викликає переривання при появі символу, виникненні помилки і т.п. Це переривання моментально викличе процедуру Вашої програми, яка, скажімо, буде передавати наступний символ з комунікаційного буфера. При програмуванні послідовної зв'язку необхідно виконати наступні етапи: - Ініціалізація послідовного порту; - П

|

|||||||||

|

Последнее изменение этой страницы: 2016-08-01; просмотров: 317; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.191.135.39 (0.022 с.) |