Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Лекция 3 Архитектура микропроцессора КР580ВМ80АСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Цель лекции: знакомство с архитектурой и основными функциональными узлами микропроцессора КР580ВМ80А.

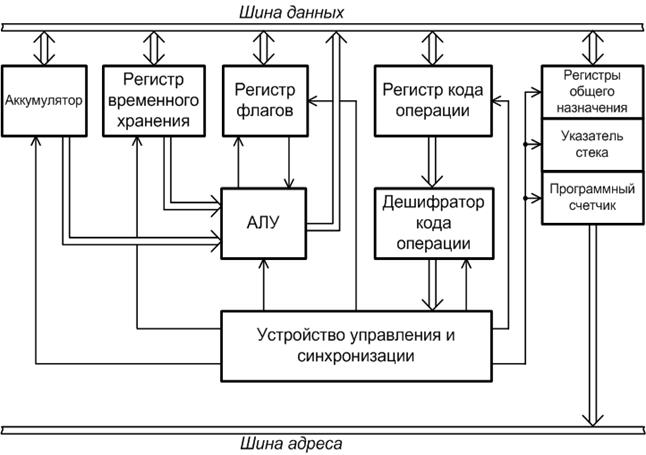

Структурная схема процессора изображена на рисунке 3.1

Рисунок 3.1- Структурная схема процессора

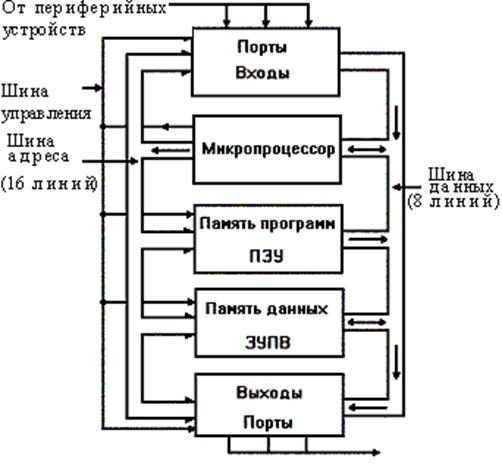

Общий принцип работы микропроцессорного устройства С помощью программного счетчика микропроцессора на шину адреса системы выдается адрес выполняемой команды. Считанная из памяти по этому адресу команда (ее код) поступает на шину данных, затем считывается микропроцессором, декодируется и выполняется. В программном счетчике (счетчике команд) автоматически формируется адрес следующей команды. После окончания исполнения текущей команды на шину адреса поступает адрес очередной команды, и процедура повторяется вновь. Архитектура типового микропроцессора приведена на рисунке 3.2.

Рисунок 3.2- Архитектура типового микропроцессора

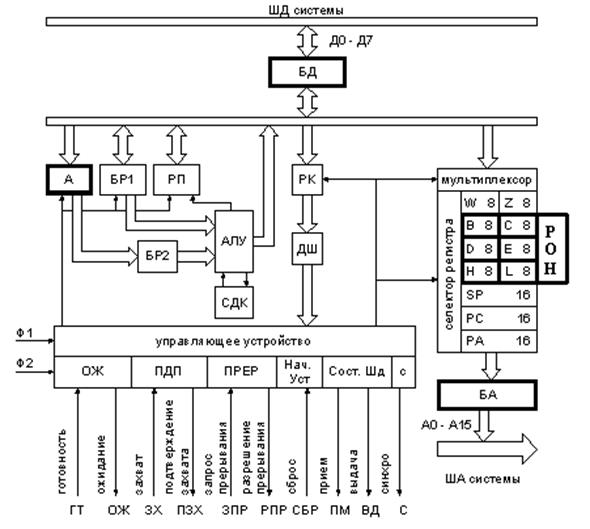

В микропроцессоре можно выделить пять основных блоков: 1) устройство ввода информации 2) управляющее устройство (УУ) 3) арифметико-логическое устройство (АЛУ) 4) запоминающие устройства (ЗУ) 5) устройство вывода информации. Микропроцессор координирует работу всех устройств цифровой системы с помощью шины управления (ШУ). Помимо ШУ имеется шестнадцатиразрядная адресная шина (ША), которая служит для выбора определенной ячейки памяти, порта ввода или порта вывода. По восьмиразрядной информационной шине или шине данных (ШД) осуществляется двунаправленная пересылка данных к микропроцессору и от микропроцессора. Постоянное запоминающее устройство (ПЗУ) содержит некоторую программу. Программы могут быть загружены в запоминающее устройство с произвольной выборкой (ЗУПВ) и из внешнего запоминающего устройства (ВЗУ). Это программы пользователя. МП КР580ВМ80А-однокристальный восьмиразрядный МП с шестнадцатиразрядной шиной адреса, с устройством управления построенным по жесткой логике. Основные характеристики микропроцессора: - Разрядность 8 бит - Адресуемая память V=216 байт=26*210байт=64килобайт, т.к.nш.а.=16 бит - Частота 2,5 МГц - Быстродействие 625000 опер/сек - Технология 6 микрон - Р=1,7 Вт Структурная схема микропроцессора состоит из двух частей: операционной части и управляющей части. Схема изображена на рисунке 3.3

Рисунок 3.3 – Структурная схема МП КР580ВМ80А Состав операционной части. 1) АЛУ (арифметико–логическое устройство) – восьмиразрядный комбинационный сумматор для выполнения арифметических операций и набор логических схем для выполнения логических операций, сдвигов и сравнения. 2) БР1 (буферный регистр аккумулятора) – хранит один операнд на время операции в АЛУ. Этот регистр хранит операнд из аккумулятора. 3) БР2 (буферный регистр) – хранит второй операнд на время операции в АЛУ. 4) А (аккумулятор) – восьмиразрядный главный регистр микропроцессора, хранит один операнд до операции в АЛУ и результат после операции в АЛУ. 5) РгФл (регистр флагов) – восьмиразрядный регистр, хранит пять признаков результата в АЛУ: - ZF – признак нулевого результата (ZF=1, если результат 000000002) - CF – признак основного переноса (CF=1, если есть перенос из восьмиго разряда в 9-й). - ACF – признак дополнительного переноса (ACF=1, если есть перенос из четырехго разряда в 5-й). - SF – признак знака (SF=восьмому биту результата). - PF – признак четности (PF=1, если количество единиц в восьмиразрядном результате чётное). 6) B, C, D, E, H, L – регистры общего назначения (РОН) – это шесть восьмиразрядных программно – доступных регистров для временного хранения данных и результата. Они могут объединяться в шестнадцатиразрядные регистровые пары – BC, DE, HL; регистры W и Z – программно – недоступны. 7) СДК (схема десятичной коррекции) – предназначена для коррекции результата при выполнении операций над двоично-десятичными числами. Состав управляющей части: 1) РгК (регистр команд) – хранит первый байт команды; 2) DC (дешифратор команд) – дешифрирует команду; подключает одну из логических схем в устройстве управления, которая вырабатывает определенный набор управляющих сигналов (Yi) для выполнения этой команды; 3) УУ (устройство управления) – формирует внутренние управляющие сигналы (Yi) для внутренних блоков МП и внешние управляющие сигналы для системы, а также воспринимает управляющие сигналы из системы; 4) РС (программный счётчик) – шестнадцатиразрядный адресный регистр для хранения следующего адреса памяти, по которому будет обращаться МП; 5) RA (регистр адреса) – шестнадцатиразрядный адресный регистр для хранения текущего адреса памяти, по которому в данный момент обращается МП; 6) SP (указатель стека) – шестнадцатиразрядный адресный регистр для хранения адреса последней занятой ячейки стековой памяти (вершины стека); 7) СИД (схема инкремент – декремент) – изменяет на единицу содержимое регистров SP, PC, RA. 8) БАдр (буфер данных) – буферная схема шины адреса – схема с тремя состояниями для сопряжения адресных выходов МП А15 – А0 с регистром адреса (RA). 9) БД (буфер данных) – буферная схема шины данных – схема с 3-мя состояниями для сопряжения внешних выводов D0 – D7 с внутренней шиной данных.

Формат данных и команд Данные (обрабатываемая информация и результаты обработки) хранятся в оперативной памяти и в процессоре в виде восьмиразрядных двоичных чисел. Таким образом, слово имеет следующий формат: Команды имеют длину от одного до трех байт. Код операции всегда размещен в первом байте команды. Второй байт команды отводится под непосредственный операнд или адрес порта, второй и третий байты являются адресом ячейки памяти. Команды допускают явное задание только одного адреса памяти, т. е. относятся к классу одноадресных команд. Для команд используются одно-, двух- и трехбайтовые форматы. Большинство команд является однобайтовыми. Однобайтовый формат: операнд или номер (адрес) устройства ввода-вывода. В первом байте двухбайтовой команды указывается вид выполняемой операции, во втором байте приводится число, являющееся операндом при выполнении операции, либо адрес устройства ввода или вывода при обмене данными с периферийными устройствами. Трехбайтовый формат команды: байты трехбайтовой команды имеют следующее назначение: в первом указывается вид выполняемой операции, следующие два байта используются для указания двухбайтового адреса команды (при выполнении безусловных и условных переходов, обращении к подпрограммам), или адреса ячейки оперативной памяти, содержимое которой является операндом, или двухбайтового операнда. Во всех случаях байт В2 является младшим, байт В3 - старшим. Способы адресации Для выполнения какой-либо операции в команде должно содержаться указание вида операции, а также откуда берутся участвующие в операции числа и куда помещается результат выполненной операции (т.е. указание об источниках и приемнике операндов). Под способами адресации понимают способы указания источников и приемников операндов. Прямая адресация. При этом способе адресом операнда является указанный в команде (в байте кода операции) адрес регистра микропроцессора. Адреса регистров приведены в следующей таблице: Под М понимается ячейка оперативной памяти, адресом которой служит содержимое пары регистров HL. Непосредственная адресация. При этом способе адресации операнды (один или два) задаются непосредственно в команде вслед за байтом кода операции во втором байте либо во втором и третьем байтах. Команда с мнемоникой ADI предусматривает суммирование содержимого аккумулятора с числом, приведенным во втором байте команды (в примере это число равно 4С(6). Команда MVI производит пересылку числа, приведенного во втором байте команды (в примере это число равно 4Е(6), в регистр D, адрес которого (010) указан в разрядах первого байта команды. Команда LXI производит пересылку чисел, приведенных во втором и третьем байтах (в примере — чисел 65(6 и А5 соответственно в младший и старший регистры пары регистров DE. В разрядах D5D4D3 первого байта пара регистров указана адресом (010) одного из регистров этой пары. Косвенная адресация. При этом способе адресации в команде отмечается пара регистров блока РОН (путем указания адреса одного из регистров этой пары), содержимое которой служит адресом, по которому в оперативной памяти находится операнд. Примеры команд с косвенной адресацией. LDAX В 00 001 010 А ←[(ВС)] STAX В 00 000 010 [(ВС)]←(А) Здесь запись [(ВС)] означает ячейку памяти, адресом которой служит содержимое пары регистров ВС. По команде LDAX В аккумулятор загружается содержимым ячейки оперативной памяти, адресом которой служит содержимое пары регистров ВС (для указания именно этой пары регистров в разрядах D5D4D3 команды приведен адрес 001 регистра С). По команде STAX В содержимое аккумулятора запоминается в ячейке, адресом которой служит содержимое пары регистров ВС (для указания пары регистров в разрядах D5D4D$ команды приведен адрес ООО регистра В) Контрольные вопросы: 1. Какие функции выполняют элементы управляющей части? 2. Какие функции выполняют элементы операционной части? 3. Какие функции выполняют регистры? 4. Какие существуют форматы данных и команд? 5. Какие способы адресации микропроцессора.

|

||||

|

Последнее изменение этой страницы: 2021-02-07; просмотров: 413; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.116.49.143 (0.008 с.) |