Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Основные функциональные блоки микроконтроллера МК-51 Система прерыванийСодержание книги

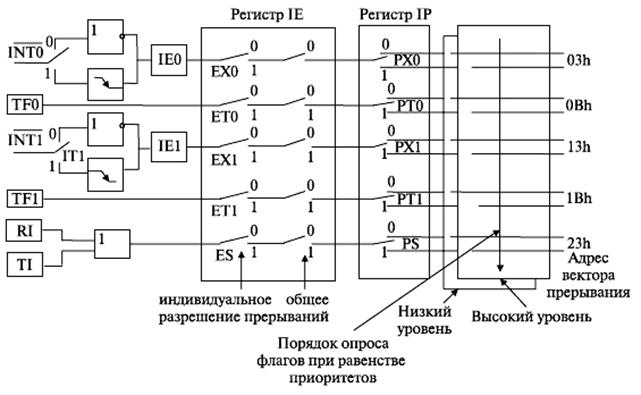

Поиск на нашем сайте Системы прерываний - важная часть любой управляющей системы. От ее работы во многом зависит то, насколько эффективно микропроцессорная система выполняет свои функции. Общая структура системы прерываний МК-51 представлена на рисунке 19.3.

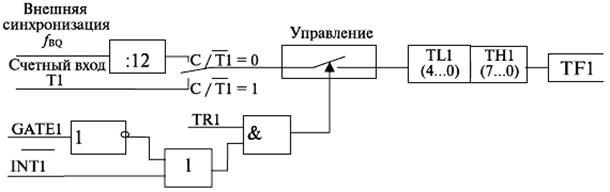

Рисунок 19.3 – Структура системы прерываний Микроконтроллеры семейства МК-51 обеспечивают поддержку пяти источников прерываний: - двух внешних прерываний, поступающих по входам INT0 и INT1 (линии порта Р3: Р3.2 и Р3.3 соответственно); - двух прерываний от таймеров/счетчиков Т/С0 и Т/С1; - прерывание от последовательного порта. Каждому виду прерывания может быть программно присвоен один из двух возможных приоритетов: 0 - низший или 1 - высший. Настройка приоритетов осуществляется установкой или сбросом соответствующего бита регистра приоритетов прерываний IP. Аппаратно реализуемый вызов обработчика прерываний состоит из следующих действий: - сохранение значения программного счетчика в стеке; - загрузка в программный счетчик начального адреса точки входа в соответствующий обработчик прерывания. По указанному адресу должна размещаться первая команда обработчика прерывания. Как правило, такой командой является команда безусловного перехода в то место программы, где фактически располагается обработчик. При переходе на подпрограмму обработки прерывания автоматически независимо от состояния регистра IE запрещаются все прерывания, которые имеют уровень приоритета, равный уровню приоритета обслуживаемого прерывания, - то есть вложенные прерывания с равным уровнем приоритета запрещены. Таким образом, низкоприоритетное прерывание (имеющее "0" в соответствующем разряде регистра IP) может прерываться высокоприоритетным (имеющим "1" в соответствующем разряде регистра IP), но не низкоприоритетным. Обслуживание высокоприоритетного прерывания не может быть прервано другим источником. Возврат из обработчика прерываний осуществляется с помощью команды RETI, которая восстанавливает из стека значение программного счетчика PC, сохраненного там в момент вызова обработчика прерывания, и логику приоритетов прерываний. Блок таймеров/счетчиков Таймеры/счетчики (Т/С) предназначены для подсчета внешних событий, получения программно управляемых временных задержек и выполнения времязависимых функций. В состав блока Т/С входят следующие основные элементы: - два шестнадцатиразрядных регистра Т/С0 и Т/С1, - восьмиразрядный регистр режимов TMOD, - восьмиразрядный регистр управления TCON, - схема инкремента, - схемы управления. Регистры Т/С0 и Т/С1 выполняют функцию хранения текущего состояния счетчика. Каждый из них состоит из пары восьмиразрядных регистров: (ТН0, TL0) для Т/С0 и (TH1, TL1) для Т/С1. Регистры ТН0 и TH1 содержат старшие, а регистры ТL0 и TL1 - младшие разряды регистров Т/С0 и Т/С1. Каждый из этих регистров программно доступен по записи и чтению. Начальное значение счета заносится в регистры ТHx и TLx таймера/счетчика программно. В процессе счета содержимое регистров Т/С инкрементируется. Перенос, возникающий при выполнении счета, фиксируется в бите TFx регистра TCON и может быть использован в качестве запроса прерывания. Включение/выключение таймера/счетчика в работу производится битами TR1 и TR0 регистра управления TCON. Они устанавливаются и сбрасываются программно, доступны по чтению. Установка бита в "1" приводит к включению в работу соответствующего таймера/счетчика, а сброс этого бита в "0" приводит к его остановке. Таймеры/счетчики могут функционировать в одном из четырех режимов, определяемых разрядами M1.x и M0.x регистра TMOD. Режимы 0, 1, 2 полностью идентичны для обоих таймеров/счетчиков. Установка таймера/счетчика 0 в режим 3 влияет на режим работы таймера/счетчика 1. Режим 0. Таймер/счетчик представляет собой устройство на основе 13-разрядного регистра, состоящего из восьмиразрядного регистра TH и пяти младших разрядов регистра TL. Логика работы таймера/счетчика в режиме 0 показана на рисунке 19.4 на примере T/C1.

Рисунок 19.4 - Логика работы таймера/счетчика 1 в режиме 0

При работе таймера/счетчика в режиме счетчика внешних событий его содержимое увеличивается каждый раз при переключении из "1" в "0" сигнала на счетном входе микроконтроллера (вывод T0 (P3.4) для T/C0 и вывод T1 (P3.5) для T/C1). При этом частота изменения сигналов на счетном входе должна быть как минимум в 2 раза ниже внешней частоты синхронизации микроконтроллера. Режим 1. Аналогичен режиму 0, за исключением того, что в этом режиме таймер/счетчик представляет собой устройство на основе не 13-разрядного, а шестнадцатиразрядного регистра, состоящего из регистров THx и TLx. Логика работы таймера/счетчика в этом режиме полностью соответствует режиму 0. Режим 2. Таймер/счетчик представляет собой устройство на основе восьмиразрядного регистра TL. При каждом переполнении регистра TL, кроме установки в регистре TCON флага TF, происходит автоматическая перезагрузка содержимого регистра TL из регистра TH. Логика работы таймера/счетчика в этом режиме также соответствует режиму 0. Режим 3. В режиме 3 T/C1 заблокирован и просто сохраняет свое состояние. Таймер/счетчик T/C0 в режиме 3 представляет собой два независимых устройства на основе восьмиразрядных регистров TH0 и TL0. Устройство на основе регистра TL0 может работать как в режиме таймера, так и в режиме счетчика внешних событий. За ним сохраняются все биты управления T/C0, оно реагирует на воздействия по входам T0 и INT0. При переполнении TL0 устанавливается флаг TF0. Устройство на основе регистра TH0 может работать только в режиме таймера. Оно использует бит включения TR1, при переполнении TH0 устанавливается флаг TF1. Других битов управления устройство на основе TH0 в этом режиме не имеет. Логи ка работы T/C0 в режиме 3 показана на рисунке 19.5.

Рисунок 19.5 - Логика работы таймера/счетчика 0 в режиме 3

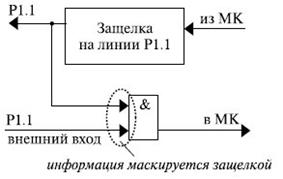

Установка T/C0 в режим 3 лишает T/C1 бита включения TR1. Поэтому T/C1 в режимах 0, 1, 2 при GATE1 = 0 всегда включен и при переполнении в режимах 0 и 1 T/C1 обнуляется, а в режиме 2 перезагружается, не устанавливая флаг, если IT/C0 находится в режиме 3. Управление от входов INT1, T1 и использование бит управления C/T1, GATE1 для T/C1 не зависят от режима IT/C0. T/C1 аппаратно связан с блоком синхронизации последовательного интерфейса (ПИ). При работе в режимах 0, 1, 2 при переполнении T/C1 всегда вырабатывается импульс, который может использоваться для тактирования ПИ. Поэтому режим 3 для IT/C0 удобно применять тогда, когда требуется работа ПИ, тактируемого таймером/счетчиком 1, и двух таймеров/счетчиков или ПИ, таймера и счетчика. Когда IT/C0 переведен в режим 3, T/C1 можно выключить, переведя его также в режим 3, использовать с последовательным портом для выработки импульсов тактирования или в любых других приложениях, не требующих прерывания. Организация ввода-вывода информации в микроконтроллере Однокристальные микроконтроллеры обладают широкими возможностями по вводу и выводу информации. Микроконтроллеры семейства МК-51 для этих целей имеют: - четыре параллельных восьми-разрядных порта P0-P3, каждая линия которых может индивидуально настраиваться на ввод либо вывод информации; - один последовательный порт. Параллельные порты. Помимо возможности использования любого из параллельных портов для ввода или вывода информации за каждым из них аппаратно закреплены определенные функции. Порт P0: - выводит младший байт адреса (АсемиА0) при работе с внешней памятью программ и внешней памятью данных; - выдает из МК и принимает в МК байт данных при работе с внешней памятью; при этом выдача адреса и обмен данными мультиплексируются во времени аппаратными средствами микроконтроллера, а для хранения младшего байта адреса в микропроцессорной системе должен быть предусмотрен внешний по отношению к МК регистр адреса; - задает данные при программировании внутреннего ППЗУ в тех БИС, где оно предусмотрено, и читает содержимое внутренней памяти программ. Порт P1. Через порт P1 вводится младший байт адреса (АсемиА0) при программировании внутреннего ППЗУ и чтении внутренней памяти программ. Порт P2. Порт P2 применяется для вывода старшего байта адреса (А15-А8) при обращении к внешней памяти программ и данных и ввода разрядов адреса А11-А8 при программировании внутреннего ППЗУ и чтении внутренней памяти программ. Порт Р3. Каждый из разрядов порта Р3 используется для выполнения альтернативных функций Для выполнения этим портом альтернативных функций необходимо, чтобы защелки соответствующих разрядов содержали "1". Каждая линия каждого параллельного порта может независимо от других настраиваться как на ввод, так и на вывод данных. Для использования линии в качестве входа необходимо, чтобы его защелка содержала "1". Несмотря на различия в электрической организации этих портов, логическая схема их работы выглядит так, как представлено на рисунке 19.7 на примере линии 1 порта Р1.

Рисунок 19.7 - Логическая схема работы линии Р1.1 при вводе и выводе информации При выводе информация записывается в некоторую внутреннюю защелку P1.1. Информация, вводимая по этой линии, маскируется этой защелкой. Если данная линия не настроена на ввод, то есть в защелку не занесена "1", то в микроконтроллер будет вводиться только "0".

|

||

|

Последнее изменение этой страницы: 2021-02-07; просмотров: 305; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.01 с.) |