Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Структура микропроцессорной системыСодержание книги

Поиск на нашем сайте МПС - сложная система, включающая в себя большое количество различных устройств. Основой ее является микропроцессор. Связь устройств ЭВМ между собой осуществляется с помощью сопряжений, которые в вычислительной технике называются интерфейсами. Интерфейс - это совокупность программных и аппаратных средств, предназначенных для передачи информации между компонентами ЭВМ и включающих в себя электронные схемы, линии, шины и сигналы адресов, данных и управления, алгоритмы передачи сигналов и правила интерпретации сигналов устройствами. В широком смысле интерфейс включает также механическую часть (совместимость по типоразъемам) и вспомогательные схемы, обеспечивающие электрическую совместимость устройств по уровням логических сигналов, входным и выходным токам и т. д. Подробное изучение интерфейсов и системных шин не входит в задачи данного курса. Поэтому эти вопросы мы будем рассматривать лишь с точки зрения общего представления об организации работы микропроцессорной системы и принципах взаимодействия составляющих ее устройств. Основным способом организации МПС является магистрально-модульный (рис. 8.1): все устройства, включая и микропроцессор, представляются в виде модулей, которые соединяются между собой общей магистралью. Обмен информацией по магистрали удовлетворяет требованиям некоторого общего интерфейса, установленного для магистрали данного типа. Каждый модуль подключается к магистрали посредством специальных интерфейсных схем.

Рисунок 13.1 – Магистрально-модульный принцип построения МП системы

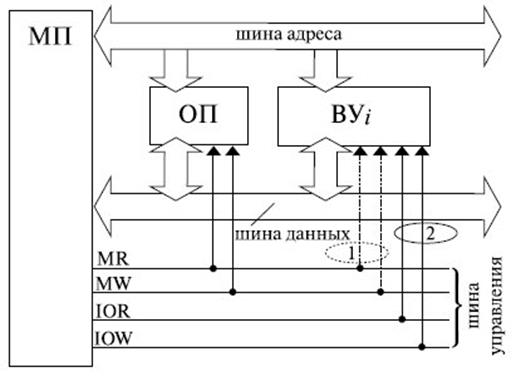

На интерфейсные схемы модулей возлагаются следующие задачи: - обеспечение функциональной и электрической совместимости сигналов и протоколов обмена модулей и системной магистрали; - преобразование внутреннего формата данных модуля в формат данных системной магистрали и обратно; - обеспечение восприятия единых команд обмена информацией и преобразование их в последовательность внутренних управляющих сигналов. Эти интерфейсные схемы могут быть достаточно сложными. Обычно они выполняются в виде специализированных микропроцессорных БИС. Такие схемы принято называть контроллерами. Контроллеры обладают высокой степенью автономности, что позволяет обеспечить параллельную во времени работу периферийных устройств и выполнение программы обработки данных микропроцессором. Кроме того, предварительно буферируя данные, контроллеры обеспечивают пересылку сразу для многих слов, расположенных по подряд идущим адресам, что позволяет использование так называемого "взрывного" (burst) режима работы шины - 1 цикл адреса и следующие за ним многочисленные циклы данных. Недостатком магистрально-модульного способа организации ЭВМ является невозможность одновременного взаимодействия более двух модулей, что ставит ограничение на производительность компьютера. Взаимодействие микропроцессора с оперативной памятью (ОП) и внешними устройствами (ВУ) проиллюстрировано на рисунке 13.2.

Рисунок 13.2 - Взаимодействие микропроцессора с оперативной памятью и внешними устройствами

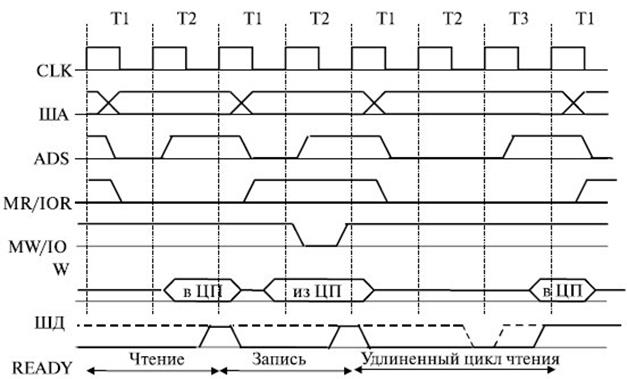

Микропроцессор формирует адрес внешнего устройства или ячейки оперативной памяти и вырабатывает управляющие сигналы – либо IOR/IOW при обращении на чтение/запись из внешнего устройства, либо MR/MW для чтения/записи из оперативной памяти. Для обмена информацией с внешними устройствами в МП имеются только две команды: - команда ввода IN AX, DX записывает в регистр AX число из внешнего устройства, адрес которого находится в регистре DX; при этом вырабатывается сигнал IOR (INput/OUTput Read).); - команда вывода OUT DX, AX выводит информацию из регистра AX во внешнее устройство, адрес которого находится в регистре DX; при этом вырабатывается сигнал IOW (INput/OUTput Write). Сигналы IOR/IOW формируются при выполнении только этих команд. Формирование сигналов MR/MW происходит в командах, для которых операнд и/или приемник результата располагаются в оперативной памяти, например, ADD [EBX], AX. В связи с этим возможны два основных способа организации адресного пространства микропроцессорной системы: 1) с общим адресным пространством внешних устройств и оперативной памяти; 2) с независимыми адресными пространствами. В первом случае к портам ввода/вывода можно обращаться как к ячейкам оперативной памяти. Достоинством такого подхода является возможность использовать различные режимы адресации при обращении к внешним устройствам, а также выполнять над содержимым портов ввода/вывода различные арифметико-логические операции. Но в то же время при этом сокращается емкость адресуемой ОП и снижается защищенность системы, так как она лишается дополнительных средств защиты, связанных с выполнением команд ввода/вывода (не работает поле IOPL регистра флагов). К тому же нарушение в логике работы программы (формирование неверного адреса оперативной памяти) может привести к ложному срабатыванию внешнего устройства. Если первый недостаток не столь существенен при современных объемах запоминающих устройств, то второй может весьма негативно сказаться на работе МПС. Возможность использования сложных режимов адресации при обращении к внешним устройствам для микропроцессорных систем на основе универсальных МП не столь важна. Поэтому в настоящее время при построении МПС предпочтение отдается второму подходу. Особенности обмена информацией микропроцессора с внешними устройствами. Упрощенная временная диаграмма этого процесса представлена на рисунке 13.3.

Рисунок 13.3 - Временная диаграмма обмена информацией между микропроцессором и внешним устройством

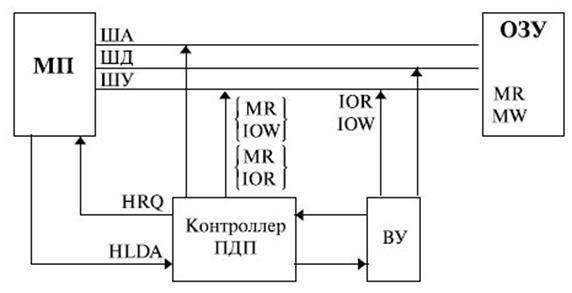

При таком обмене микропроцессор использует стандартный цикл шины длительностью два периода тактового генератора, начало которого определяется сигналом A DS шины. Однако если в обмене задействованы относительно медленное внешнее устройство или оперативная память, которые не успевают завершить обмен в текущем цикле работы микропроцессора, то они сбрасывают сигнал READY, который проверяется микропроцессором в конце второго тактового сигнала цикла. При READY = 0 МП вставляет дополнительные такты ожидания в цикл шины, чтобы дать возможность внешнему устройству завершить операцию ввода/вывода. Однако сигнал неготовности внешнего устройства не может длиться более установленного времени (для шины ISA - 2,5 мкс), в противном случае генерируется прерывание по ошибке ввода/вывода. Это предотвращает зависание системы в случае, например, механического повреждения данного контакта. В общем случае стандартный цикл шины при обмене уже включает несколько дополнительных тактов ожидания. При этом циклы обращения к памяти короче циклов обращения к портам ввода/вывода. Минимальная длительность цикла определяется чипсетом и может программироваться опциями BIOS Setup заданием тактов ожидания. Если ОП или внешнее устройство не нуждаются в дополнительных тактах, то их контроллеры выставляют на шину сигнал OWS, по которому дополнительные такты не вставляются. Прямой доступ к памяти В МПС используются два основных способа организации передачи данных между памятью и периферийными устройствами: программно управляемая передача и прямой доступ к памяти ПДП (Direct Memory Access - DMA). Программно управляемая передача данных осуществляется при непосредственном участии и под управлением процессора. Например, при пересылке блока данных из внешнего устройства в оперативную память процессор должен выполнить следующую последовательность шагов: 1) сформировать начальный адрес области обмена ОП; 2) занести длину передаваемого массива данных в один из своих внутренних регистров, который будет играть роль счетчика; 3) выдать команду чтения информации из ВУ; при этом на шину адреса из МП выдается адрес ВУ, на шину управления - сигнал чтения данных из ВУ, а считанные данные заносятся во внутренний регистр МП; 4) выдать команду записи информации в ОП; при этом на шину адреса из МП выдается адрес ячейки оперативной памяти, на шину управления - сигнал записи данных в ОП, а на шину данных выставляются данные из регистра МП, в который они были помещены при чтении из ВУ; 5) модифицировать регистр, содержащий адрес оперативной памяти; 6) уменьшить счетчик длины массива на длину переданных данных; 7) если переданы не все данные, то повторить шаги 3-6, в противном случае закончить обмен. Программно управляемый обмен ведет к нерациональному использованию мощности микропроцессора, который вынужден выполнять большое количество относительно простых операций, приостанавливая работу над основной программой. При этом действия, связанные с обращением к оперативной памяти и к внешнему устройству, обычно требуют удлиненного цикла работы микропроцессора, что приводит к еще более существенным потерям производительности. Альтернативой программно управляемому обмену служит прямой доступ к памяти - способ быстродействующего подключения внешнего устройства, при котором оно обращается к оперативной памяти, не прерывая работы процессора. Такой обмен происходит под управлением отдельного устройства - контроллера прямого доступа к памяти (КПДП). Схема включения КПДП в состав микропроцессорной системы представлена на рисунке 13.4

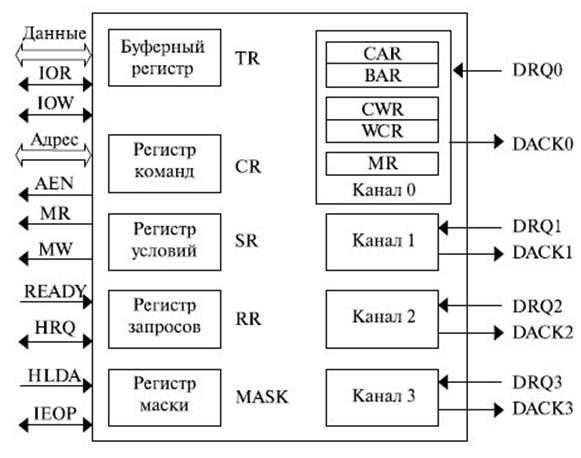

Перед началом работы контроллер ПДП необходимо инициализировать: занести начальный адрес области ОП, с которой производится обмен, и длину передаваемого массива данных. В дальнейшем по сигналу запроса прямого доступа контроллер фактически выполняет все те действия, которые обеспечивал микропроцессор при программно управляемой передаче. Последовательность действий КПДП при запросе на прямой доступ к памяти со стороны внешнего устройства следующая: 1) Принять запрос на ПДП (сигнал DRQ) от ВУ. 2) Сформировать запрос к МП на захват шин (сигнал HRQ). 3) Принять сигнал от МП (HLDA), подтверждающий факт перевода микропроцессором своих шин в третье состояние. 4) Сформировать сигнал, сообщающий устройству ввода-вывода о начале выполнения циклов прямого доступа к памяти (DACK). 5) Сформировать на шине адреса компьютера адрес ячейки памяти, предназначенной для обмена. 6) Выработать сигналы, обеспечивающие управление обменом (IOR, MW для передачи данных из ВУ в оперативную память и IOW, MR для передачи данных из оперативной памяти в ВУ). 7) Уменьшить значение в счетчике данных на длину переданных данных. 8) Проверить условие окончания сеанса прямого доступа (обнуление счетчика данных или снятие сигнала запроса на ПДП). Если условие окончания не выполнено, то изменить адрес в регистре текущего адреса на длину переданных данных и повторить шаги 5-8. Прямой доступ к памяти позволяет осуществлять обмен данными между внешним устройством и оперативной памятью параллельно с выполнением процессором программы. Структура КПДП представлена на рисунке 13.5. Контроллер состоит из четырех идентичных каналов, позволяющих подключить к системе до четырех устройств, работающих в режиме ПДП. В состав каждого канала входят следующие регистры: а) MR (Mode Register) - регистр режима. Определяет следующие параметры передачи: 1) порядок изменения (увеличения или уменьшения) адреса ОП при передаче; 2) возможность автоинициализации; 3) режим обслуживания: 4) одиночная передача (контроллер возвращает магистраль процессору после каждого цикла ПДП); 5) блочная передача (контроллер владеет магистралью в течение передачи всего массива); 6) по требованию (окончание передачи определяется снятием сигнала DRQ или подачей сигнала IEOP на внешний вход КПДП); 7) каскадирование;

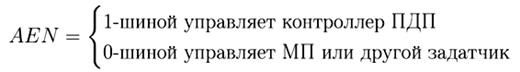

б) CAR (Current Address Register) - регистр текущего адреса; в) BAR (Base Address Register) - базовый регистр адреса; г) CWR (Current Word Register) - текущий счетчик данных; д) WCR (W0ord ConTRol Register) - базовый счетчик данных. Значения в регистрах BAR и WCR устанавливаются при инициализации и в ходе циклов ПДП не меняются. В регистры CAR и CWR в начале выполнения ПДП заносятся значения из регистров BAR и WCR соответственно. При выполнении ПДП эти регистры изменяются. Управляющие регистры, общие для всего контроллера: а) CR (Command Register) - регистр команд - определяет: 1) режим память-память или обычный. В режиме память-память осуществляется обмен по схеме ПДП между двумя областями ОП (только для каналов 0 и 1) с использованием буферного регистра TR (Temporary Register); 2) запрет/разрешение ПДП; 3) порядок изменения приоритетов каналов: 4) фиксированный приоритет; 5) циклическое изменение приоритета после обработки запроса на ПДП по одному из каналов; 6) явное указание наиболее приоритетного канала; 7) уровень сигналов DRQ и DACK (настройка на активный уровень сигналов под особенности работы внешних устройств); б) SR (Status Register) - регистр условий: используется для фиксации признаков обмена по каждому из каналов и программных запросов на ПДП. Во избежание ложных срабатываний внешних устройств, не использующих в данный момент режим прямого доступа, контроллер ПДП во время режима ПДП вырабатывает сигнал AEN, который блокирует работу остальных внешних устройств:

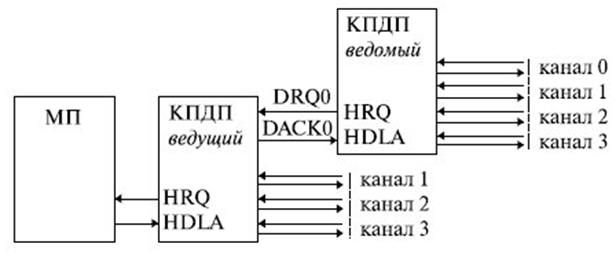

Для увеличения количества внешних устройств, которые могут быть подключены к микропроцессору в режиме ПДП, используется каскадное включение КПДП, изображенное на рисунке 13.6. При этом ведомый КПДП подключается к одному из каналов ведущего контроллера по схеме подключения внешнего устройства, а непосредственно с микропроцессором связывается только ведущий контроллер. В стандартной конфигурации персональной ЭВМ применяются два КПДП (ведущий и ведомый), которые позволяют подключить до семи внешних устройств, причем два канала закреплены за накопителями на жестком и гибком дисках.

В максимальной конфигурации при использовании ведущего и четыре ведомых КПДП, подключенных к каждому из каналов ведущего, к МП можно подключить до 16 внешних устройств, работающих в режиме ПДП.

|

||

|

Последнее изменение этой страницы: 2021-02-07; просмотров: 330; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.013 с.) |