Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Формирование физического адреса в универсальном микропроцессоре при различных режимах работы

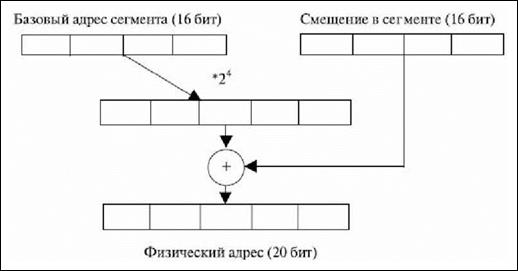

При работе в реальном режиме возможности процессора ограничены: емкость адресуемой памяти составляет 1 Мбайт, отсутствует страничная организация памяти, сегменты имеют фиксированную длину 2 байт. Этот режим обычно используется на начальном этапе загрузки компьютера для перехода в защищенный режим. В реальном режиме сегментные регистры процессора содержат старшие 16 бит физического адреса начала сегмента. Сдвинутый на 4 разряда влево селектор дает 20-разрядный базовый адрес сегмента. Физический адрес получается путем сложения этого адреса с шестнадцатиразрядным значением смещения в сегменте, формируемого по заданному режиму адресации для операнда или извлекаемому из регистра EIP для команды, как показано на рисунке 7.1. По полученному адресу происходит выборка информации из памяти.

Рисунок 7.1 – Схема получения физического адреса

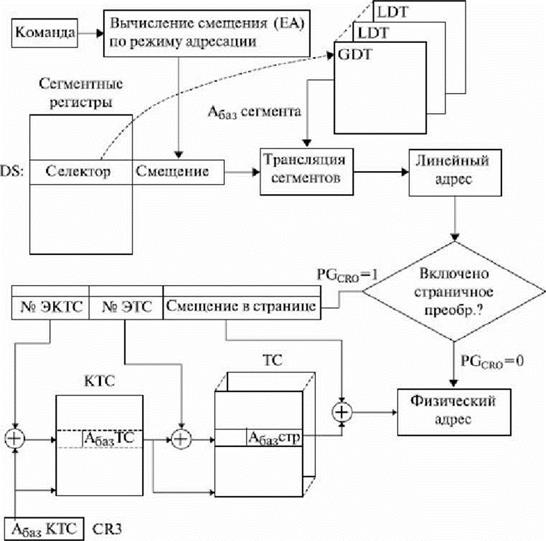

Наиболее полно возможности микропроцессора по адресации памяти реализуются при работе в защищенном режиме. Объем адресуемой памяти увеличивается до 4 Гбайт, появляется возможность страничного режима адресации. Сегменты могут иметь переменную длину от одного байта до 4 Гбайт. Общая схема формирования физического адреса микропроцессором, работающим в защищенном режиме, представлена на рисунке 7.2.

Рисунок 7.2 - Формирование физического адреса при сегментно-страничной организации памяти

Основой формирования физического адреса служит логический адрес. Он состоит из двух частей: селектора и смещения в сегменте. Селектор содержится в сегментном регистре микропроцессора и позволяет найти описание сегмента (дескриптор) в специальной таблице дескрипторов. Дескрипторы сегментов хранятся в специальных системных объектах глобальной (GDT) и локальных (LDT) таблицах дескрипторов. Дескриптор играет очень важную роль в функционировании микропроцессора, от формирования физического адреса при различной организации адресного пространства и до организации мультипрограммного режима работы. Сегменты микропроцессора, работающего в защищенном режиме, характеризуются большим количеством параметров. Поэтому в универсальных тридцатидвух разрядных микропроцессорах информация о сегменте хранится в специальной восьмибайтной структуре данных, называемой дескриптором, а за сегментными регистрами закреплена основная функция определение местоположения дескриптора.

Структура дескриптора сегмента представлена на рисунке 7.3.

Рисунок 7.3 – Структура дескриптора сегмента

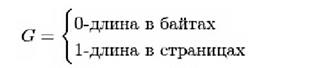

тридцатидвух разрядное поле базового адреса позволяет определить начальный адрес сегмента в любой точке адресного пространства в 2 байт (4 Гбайт). Поле предела (limit) указывает длину сегмента (точнее, длину сегмента минус единицу: если в этом поле записан 0, то это означает, что сегмент имеет длину один) в адресуемых единицах, то есть максимальный размер сегмента равен 220 элементов. Величина элемента определяется одним из атрибутов дескриптора битом G:

Таким образом, сегмент может иметь размер с точностью до 1 байта в диапазоне от 1 байта до 1 Мбайт (при G = 0). При объеме страницы в 4 Кбайт можно задать объем сегмента до 4 Гбайт (при G = 1):

Бит размерности (Default size) определяет длину адресов и операндов, используемых в команде по умолчанию:

Этот бит доступен только программам, работающим на высшем уровне привилегий. Микропроцессор в своей работе его не меняет и не использует. Запись в сегмент кода запрещена. При любой попытке записи возникает программное прерывание. В сегменте данных: - ED (Expand Down) - бит направления расширения. При ED = 1 этот сегмент является сегментом стека и смещение в сегменте должно быть больше размера сегмента. При ED = 0 - это сегмент собственно данных (смещение должно быть меньше или равно размеру сегмента); - бит разрешения записи W (Writeable). При W = 1 разрешено изменение сегмента. При W = 0 запись в сегмент запрещена, при попытке записи в сегмент возникает программное прерывание. В случае обращения за операндом смещение в сегменте формируется микропроцессором по режиму адресации операнда, заданному в команде. Смещение в сегменте кода извлекается из регистра - указателя команд EIP. Сумма извлеченного из дескриптора начального адреса сегмента и сформированного смещения в сегменте дает линейный адрес (ЛА). Если в микропроцессоре используется только сегментное представление адресного пространства, то полученный линейный адрес является также и физическим.

Если помимо сегментного используется и страничный механизм организации памяти, то линейный адрес представляется в виде двух полей: старшие разряды содержат номер виртуальной страницы, а младшие смещение в странице. Преобразование номера виртуальной страницы в номер физической проводится с помощью специальных системных таблиц: каталога таблиц страниц (КТС) и таблиц страниц (ТС). Положение каталога таблиц страниц в памяти определяется системным регистром CR3. Физический адрес вычисляется как сумма полученного из таблицы страниц адреса физической страницы и смещения в странице, полученного из линейного адреса.

|

|||||||||

|

Последнее изменение этой страницы: 2021-02-07; просмотров: 278; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.145.114 (0.005 с.) |