Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Организация внутренней кэш-памяти микропроцессораСодержание книги

Поиск на нашем сайте

Внутренний кэш тридцатидвух разрядного универсального микропроцессора является общим при обращении как к командам, так и к данным. Обращение ведется по физическим адресам. Кэш-память обычно реализуется в виде ассоциативного ЗУ, в котором для каждой строки сохраняются дополнительные сведения, называемые тегом, или признаком, в качестве которого выступает адресный код или его часть. Когда в АЗУ подается адрес, с ним одновременно сравниваются все теги. Внутренняя кэш-память в микропроцессоре i486 реализует сквозную запись. Начиная с МП Pentium используется сквозная или обратная запись. Во внешней КП применяется любой способ записи или их комбинация. Внутренняя кэш-память МП i486 имеет емкость 8 Кбайт и организована в виде четырехканальной ассоциативной памяти. Это означает, что данные из какой-либо строки ОЗУ могут храниться в любой из 4 строк кэш-памяти.

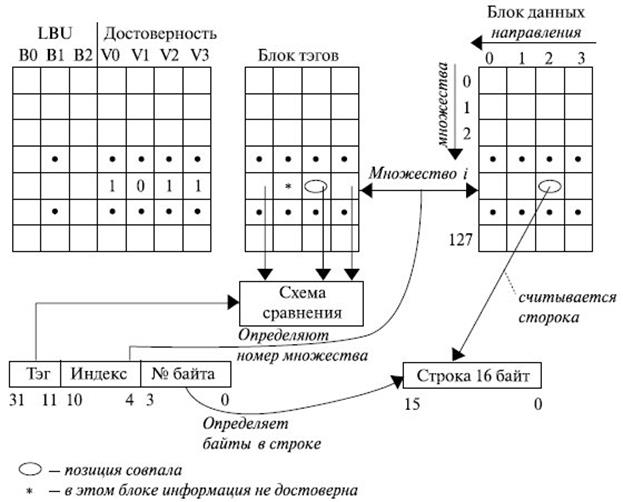

КП состоит из следующих блоков, изображенная на рисунке 8.3,: - блока данных, - блока тегов, - блока достоверности и LRU.

Рисунок 8.3 - Структура внутренней кэш-памяти МП i486

Блок данных содержит 8 Кбайт данных и команд. Он разделен на 4 массива (направления), каждый из которых состоит из 128 строк. Строка содержит данные из 16 последовательных адресов памяти начиная с адреса, кратного 16. Индекс массивов блока данных, состоящий из 7 бит, соответствует 4 строкам КП, по одной из каждого массива. Четыре строки КП с одним и тем же индексом называются множеством. В блоке тегов имеется один тег длиной 21 бит для каждой строки данных в КП. Блок тегов также разделен на 4 массива по 128 тегов. Тег содержит старшие 21 бит физического адреса данных, находящихся в соответствующей строке КП. В блоке достоверности и LRU содержится по одному семиразрядному значению для каждого из 128 множеств строк КП: 4 бита достоверности (V) по одному на каждую строку множества и 3 бита (B0... B2), управляющие механизмом LRU. Биты достоверности показывают, содержит ли строка достоверные (V = 1) или недостоверные (V = 0) данные. При программной очистке КП и аппаратном сбросе процессора все биты достоверности сбрасываются в 0. Адресация кэш-памяти осуществляется путем разделения старших 28 бит физического адреса на 2 части. Младшие 7 бит из этих разрядов (разряды 10…4 физического адреса) образуют поле индекса и определяют множество, в котором могут храниться данные. Старшие 21 бит (разряды 31…11 физического адреса) служат полем тега и применяются для определения того, находится ли информация с данным физическим адресом в какой-либо строке выбранного множества. Поиск в кэш-памяти информации с заданным физическим адресом выполняется следующим образом: Физический адрес, по которому происходит обращение, разбивается на 3 поля: Тег, Индекс, № байта. 7 разрядов А10…А4 поля индекса определяют одно из 128 множеств. В выбранном множестве содержатся 4 строки с информацией. Чтобы определить, присутствует ли нужная информация в одной из строк этого множества, проводится сравнение старших 21 бита физического адреса (поле Тег) с тегами строк выбранного множества. Сравнение проводится только для достоверных строк, то есть тех, у которых в блоке достоверности установлен бит достоверности V = 1. Если для одной из строк ее тег и разряды А31...А11 физического адреса совпали, то это означает, что произошло кэш-попадание и необходимая информация есть в кэш-памяти. Считывается найденная строка из 16 байт. Искомый байт в ней определяется 4 младшими разрядами физического адреса (А3…А0). Если на этапе 3 совпадения не произошло или все строки множества недостоверны, эта ситуация определяется как кэш-промах. В этом случае по сформированному микропроцессором физическому адресу выполняется обращение к оперативной памяти. Из ОЗУ извлекается нужная информация, и содержащая ее строка записывается в свободную строку выбранного множества. Старшие 21бит физического адреса записываются в поле тега этой строки. Если все строки в выбранном множестве достоверны, то замещается строка, к которой дольше всего не было обращений согласно механизму LRU. Этот механизм действует точно так же, как и при вытеснении строк из буфера ассоциативной трансляции TLB. Режим работы кэш-памяти определяется программно установкой разрядов CD (запрет кэширования) и NW (запрет сквозной записи) в управляющем регистре CR0. Кэширование можно разрешить (это состояние после инициализации при сбросе), можно запретить при наличии достоверных строк (в этом режиме КП действует как быстрое внутреннее ОЗУ) или, наконец, кэширование может быть полностью запрещено.

|

||||

|

Последнее изменение этой страницы: 2021-02-07; просмотров: 404; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.220 (0.012 с.) |