Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Структурная схема микропроцессорной системы на основе микропроцессорного комплекта К580Содержание книги

Поиск на нашем сайте

Структура, организация микро ЭВМ • Микропроцессор является основным компонентом любого микрокомпьютера или микро-ЭВМ. • В основу построения микро-ЭВМ положено три принципа: • Модульность — в языках программирования — принцип, согласно которому логически связанные между собой подпрограммы, переменные и т. д. группируются в отдельные файлы (модули). • Магистральность – это способ соединения между различными модулями компьютера, когда входные и выходные устройства модулей соединяются одними и теми же проводами, совокупность которых называется шиной. • Микропрограммируемость – это способ реализации принципа программного управления. • Современные ЭВМ могут иметь различную архитектуру, но обязательно содержат в своей структуре следующие элементы: • Арифметико-логическое устройство (АЛУ), выполняющее арифметические и логические операции. • Устройство управления (УУ), которое организует процесс выполнения программ. • Запоминающее устройство (память) для хранения программ и данных. • Внешние устройства для ввода–вывода информации (ВУ). Принципы фон Неймана • Принцип программного управления обеспечивает автоматизацию процессов вычислений на ЭВМ. • Согласно этому принципу программа состоит из набора команд, которые выполняются процессором автоматически друг за другом в определенной последовательности. • Принцип однородности памяти. Программы и данные хранятся в одной и той же памяти. Поэтому компьютер не различает, что храниться в данной ячейке памяти – число, текст или команда. Над командами можно выполнять такие же действия, как и над данными. • Иногда этот принцип называют «принцип хранимой команды» • Принцип адресности. Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка. Это позволяет обращаться к произвольной ячейке (адресу) без просмотра предыдущих. Структура типового МП • Шина данных (Data Bus) 8-ми разрядная, т.к. разрядность микропроцессора КР580ВМ80А равна 8-ми (D0-D7). (D0 – младший разряд, D7 – старший разряд, всего 8 разрядов). Предназначена для передачи данных от микропроцессора к периферийным устройствам, а также в обратном направлении (двунаправленная)

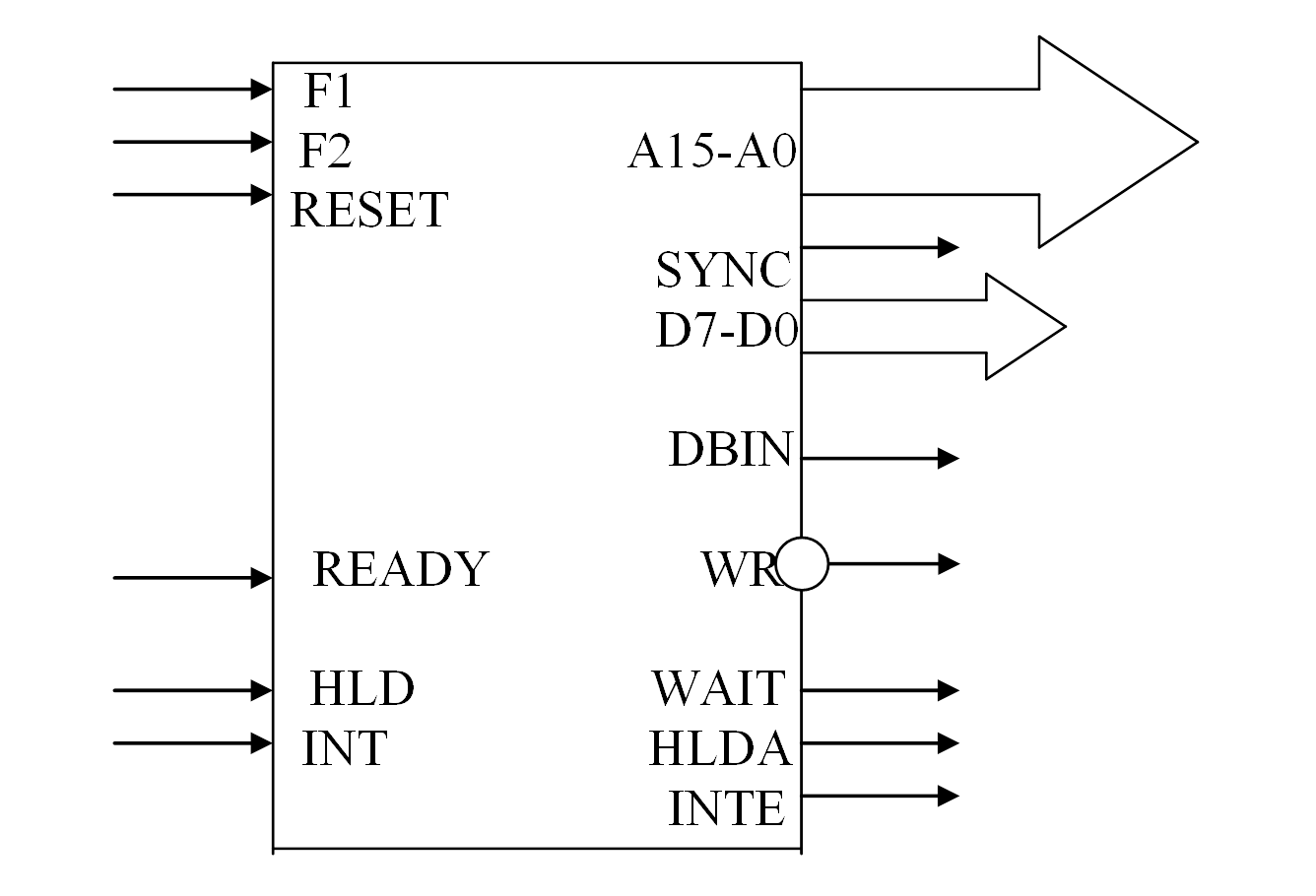

• Шина адреса (Address Bus), 16-ти разрядная (А0-А15), служит для определения адреса (номера) устройства, с которым процессор обменивается информацией в данный момент. Каждому устройству (кроме процессора), каждой ячейке памяти в микропроцессорной системе присваивается собственный адрес. • Шина управления (Control Bus), постоянной размерности не имеет, состоит из отдельных управляющих сигналов. Каждый из этих сигналов во время обмена информацией имеет свою функцию. • Некоторые сигналы служат для стробирования передаваемых или принимаемых данных, для подтверждения приема, сброса данных, или для сброса всех устройств в исходное состояние • ОЗУ хранит информацию только при наличии напряжения питания. ОЗУ-это простейший регистр построенный на D – триггерах. • ПЗУ - предназначено для долговременного хранения информации, её нельзя оперативно менять. В ПЗУ информация записывается один раз либо в процессе производства, либо непосредственно перед применением, при помощи специальных программаторов. • Соединение всего многообразия внешних устройств с шинами МК осуществляется с помощью интерфейсов, которые следует понимать как унифицированное средство объединения различных устройств в единую систему. • ППА –программируемый параллельный адаптер КР580ВВ55. • ПСА – программируемый связной адаптер КР580ВВ51. • Обмен данными с внешними устройствами осуществляется через порты ввода/вывода. • Для микропроцессора Intel 8080 общее число портов ввода/вывода может составлять 256. • В качестве внешних устройств используются клавиатура, дисплей, принтеры, датчики и т.п. • Микропроцессор Intel 8080A ориентирован на работу с памятью, имеющую байтовую организацию (8 бит). Это значит, что микропроцессор считывает информацию побайтно. • Программа и данные хранятся в памяти в ячейках длиной 1 байт (8 бит); каждая ячейка имеет адрес длиной 2 байта (16 бит). Всего процессор может напрямую обращаться к 64К памяти. Схема подключения выводов микропроцессора КР580ВМ80А и их назначения. Выводы синхронизации: • F1, F2 – выводы двух неперекрывающихся последовательностей синхроимпульсов; • SYNC – выход синхронизации, сигнал определяет начало каждого машинного цикла команды;

• RESET – вход сигнала начальной установки процессора. После прекращения действия сигнала программный счетчик устанавливается в нулевое состояние и процессор начинает работать с нулевого адреса. Выводы управления ожиданием: • READY – готово внешнее устройство (READY = 1) или не готово (READY = 0). Синхронизирует обмен информации с внешними устройствами. • WAIT – указывает, что процессор находится в состоянии ожидания (WAIT = 1). Выводы управления памятью: • WR – управление записью в память или во внешние устройства; низкий уровень указывает, что процессор выдал данные на магистраль данных D7-D0. Выводы управления магистралью данных: • DBIN – указывает, что магистраль данных (D7-D0) находится в режиме приема. Используется для управления чтением данных из памяти или внешнего устройства. Выводы управления прерыванием: • INT – запрос прерывания внешним устройством, запрашивающих обмен с процессором в режиме прерывания. • INTE – выход сигнала разрешения прерывания (INTE = 1), указывающего на то, что процессор готов к обмену в режиме прерывания; (INTE = 1 – если готов, INTE = 0 – если не готов). Выводы управления захватом магистралей в режиме ПДП: • HLD – вход запроса захвата магистралей D7-D0 и магистрали адреса А15-А0 внешними устройствами. Процессор переходит в режим ЗАХВАТ и отключает магистрали D7-D0 и А15-А0 (переходит в высокоимпедансное состояние). • HLDA – выход подтверждения захвата. Указывает, что процессор находится в состоянии ЗАХВАТ. Магистрали данных и адреса при этом отключены от выводов. Командный цикл микропроцессора • Выполнение команд в МП осуществляется в строго определенной последовательности обусловленной рядом факторов, в том числе используемыми синхросигналами. В основе работы МП лежит командный цикл - действия по выбору из памяти и выполнению одной команды. В зависимости от типа и формата команды, способов адресации и числа операндов командный цикл может включать в себя различное число обращений к памяти и ВУ и следовательно - иметь различную длительность. Машинные циклы и их идентификация • Действия МПС по передаче в/из МП одного байта данных/команды называются машинным циклом. • Командный цикл представляет собой последовательность машинных циклов (МЦ), причем КЦ i8080 может содержать от 1 до 5 МЦ. • МЦ может состоять из нескольких машинных тактов. • Машинный такт (Т) – это период синхросигналов. Его длительность может быть установлена в некоторых пределах. В МП КР580 длительность может быть установлена произвольно в диапазоне 0,5…2 мкс (при тактовой частоте 2 МГц) • МЦ микропроцессора i8080 предусматривает возможность обмена как в синхронном, так и в асинхронном режиме. • Если в составе МПС использованы только "быстрые" устройства, т.е. такие, которые могут работать с тактовой частотой МП, то передача информации в МЦ осуществляется в синхронном режиме. • При работе с "медленными" устройствами, быстродействие которых не позволяет переключаться с частотой тактового генератора МП, необходимо "растянуть" во времени МЦ, реализовав асинхронный принцип обмена. Принципы программирования микропроцессоров. • Все языки программирования условно можно разделить на три уровня: • машинный код; • автокод (язык ассемблера); • языки высокого уровня (процедурные языки и языки искусственного интеллекта.

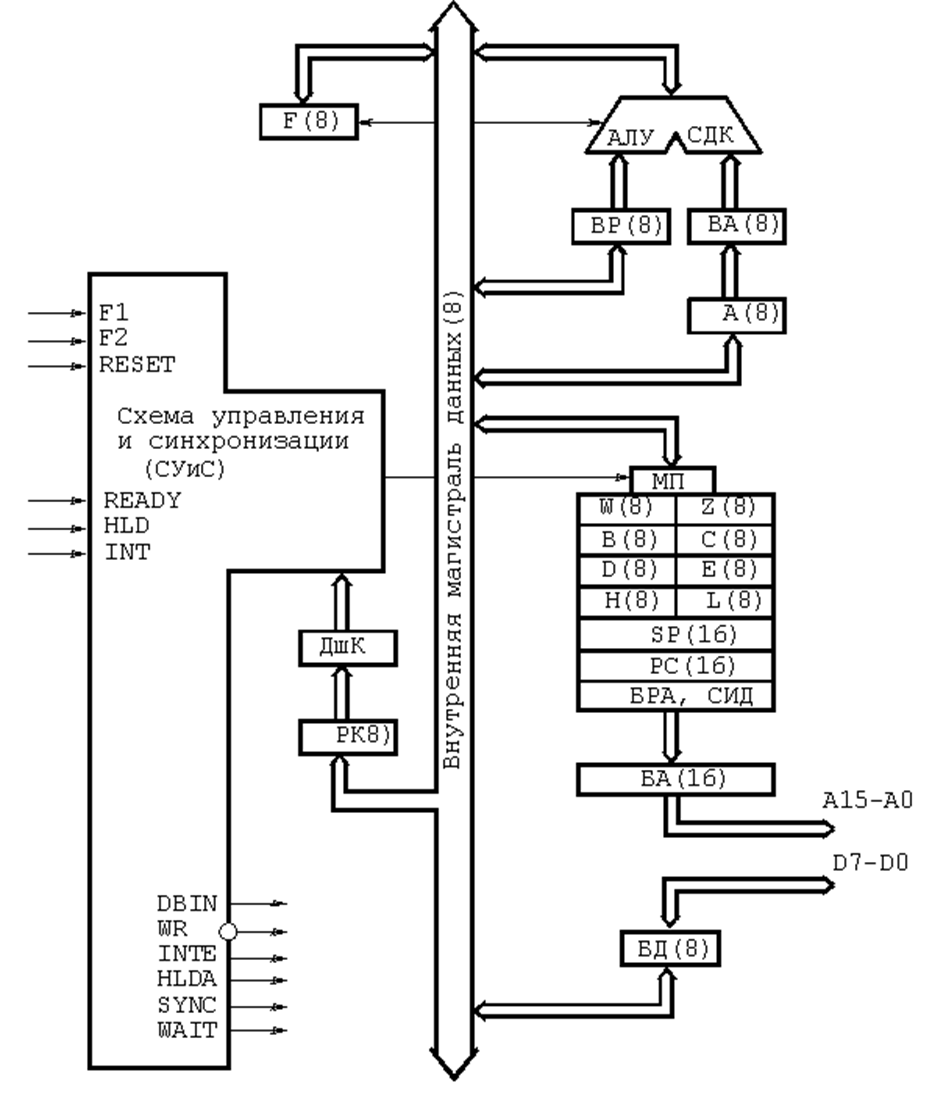

Ассемблерная мнемоника • Язык ассемблера - это символическое представление машинного языка. Все процессы в машине на самом низком, аппаратном уровне приводятся в действие только командами (инструкциями) машинного языка. • Программа на ассемблере представляет собой совокупность блоков памяти, называемых сегментами памяти. Структурная схема микропроцессора КР580ВМ80А (i8080А) • Микропроцессор КР580ВМ80А реализован на основе общей внутренней магистрали данных и включает в себя следующие функциональные узлы: блок регистров с адресной логикой; блок АЛУ; двунаправленную буферизованную магистраль данных; блок управления и синхронизации. Блок регистров • Содержит шесть 16-ти битовых регистров, образующих статическую память с произвольным доступом (регистр – пространство из восьми бит, схема или устройство хранения информации). • Три из них могут использоваться как шесть отдельных 8-ми разрядных программно-доступных регистров B, C, D, E, H, L общего назначения для хранения операндов или как три 16-ти разрядных программно-доступных пары BC, DE, HL для хранения адресов или двухбайтовых операндов. При выполнении арифметических и логических операций с регистровой адресацией в регистрах хранятся 8-ми разрядные операнды, которые передаются в АЛУ для участия в операции. Второй операнд и результат операции хранятся в блоке АЛУ. • Содержимое каждого из регистров можно переслать в блок АЛУ или в память через 8-ми битовые мультиплексоры (МП) и внутреннюю магистраль данных. Регистр-счетчик (РС) • Используется в качестве программного счетчика и хранит адрес текущей команды программы. • Его содержимое автоматически увеличивается после выборки каждого байта команды схемой адресной логики. • Загрузка и выдача содержимого РС осуществляется через мультиплексоры и внутреннюю магистраль данных. Указатель стека (SP) • SP хранит адрес ячейки стековой области памяти, к которой было сделано последнее обращение. • Содержимое SP уменьшается на 1 перед каждым занесением слова в стек или увеличивается на 1 после каждого извлечения из стека. Пара регистров W и Z • Это 8-разрядные регистры. Они недоступны программисту. Используются для запоминания двухбайтовых и трёхбайтовых команд перехода, передаваемых с внутренней магистрали данных в счётчик команд Адресная логика • предназначена для хранения, программного изменения и выдачи на магистраль А15-А0 адресов данных и команду. • Она содержит буферный регистр адреса (БРА), логическую схему инкремента-декремента (СИД) и адресный буфер.

• Буферный регистр адреса принимает и хранит адрес с любого 16-ти разрядного регистра. Его выход связан со входами СИД и БРА. Блок АЛУ. • Предназначен для выполнения арифметических и логических операций над числами в параллельном 8-ми разрядном двоичном коде. • Информация обрабатывается в АЛУ с использованием регистра временного хранения (ВР), аккумулятора временного хранения (ВА), аккумулятора (А) и регистра признаков F. Регистр флагов F • 8 разрядный регистр, содержащий информацию о текущем состоянии микропроцессора. • Имеет пять однобитовых флагов состояния, которые индицируют результаты выполнения арифметических и логических операций. В зависимости от состояния этих флагов некоторые машинные команды могут изменять последовательность выполнения команд в программе.

Двунаправленная магистраль данных • Служит для организации связи микропроцессора с другими микросхемами, входящими в состав микро-ЭВМ. • Она включает в себя внутреннюю магистраль данных, буфер данных (БД) и соединена с выводами магистрали данных D7-D0 микропроцессора. • Буфер данных – 8-ми разрядный двунаправленный с тремя состояниями – предназначен для развязки внутренней и внешней магистрали данных. Он состоит из буферного регистра данных и формирователей. • В режиме вывода информация с внутренней магистрали загружается в буферный регистр, а затем передается на внешнюю магистраль данных через формирователи. • При вводе данные из внешней магистрали через формирователи непосредственно передаются на внутреннюю магистраль. Буферный регистр данных при этом отключается. Он отключается также при выполнении операций, не связанных с передачей информации процессором. Блок управления и синхронизации • Предназначен для приема команд, синхронизирующих и управляющих внешних сигналов, а также для формирования внутренних сигналов микроопераций и внешних синхронизирующих и управляющих сигналов. Он содержит регистр команд (РК), дешифратор команд (ДшК), схемы формирования машинных циклов и другие устройства. Способы адресации микропроцессора • Микропроцессор I8080/8085 использует пять способов адресации: неявную, регистровую, непосредственную, прямую, косвенную регистровую. • Неявная адресация В команде операнд явно не задается, он подразумевается (например команда СМА). • Регистровая адресация Когда используются команды с этим способом адресации, операция и источник данных (операнд) точно определены. • Операнд отыскивается микропроцессором во внутреннем регистре микропроцессора (например команда MOV D,C). • Непосредственная адресация Команды непосредственной адресации являются командами, по которым данные следуют непосредственно за командой. • Прямая адресация В случае прямой адресации второй и третий байт команды прямо указывают на расположение операнда в памяти. Это команды трехбайтового формата (исключение составляют ввода/вывода). • Косвенная регистровая адресация . Команды с такой адресацией обращаются в память, используя содержимое пары регистров для указания на адрес операнда. Если в мнемонике команды стоит буква М, то операнд находится в памяти по адресу, записанному в регистровой пара HL.

Основные группы операций. • Микропроцессоры выполняют набор команд, которые реализуют следующие основные группы операций: • операции пересылки, • арифметические операции, • логические операции, • операции сдвига, • операции сравнения и тестирования, • битовые операции, • операции управления программой; Команды ветвлений и переходов микропроцессора Intel 8080 • Команды ветвлений содержат группы команд перехода, вызова, возврата и повторного запуска. • Эта группа команд изменяет последовательный нормальный ход программы. • Команды переходов существуют двух типов – безусловного и условного переходов. • Безусловные переходы просто выполняют операцию перехода по указанному адресу; условные – проверяют состояние одного из индикаторов микропроцессора. • Условия, которые проверяются командами условных переходов, задаются в следующей форме: • Условия: • JNZ – не нуль(Z = 0) • JZ – нуль(Z = 1) • JNC – нет переноса(CY = 0) • JC – перенос (C = 1) • JPO – нечетность (P = 0) • JPE – четность (P = 1) • JP – плюс (S = 0) • JM – минус (S = 1) • JMP addr (Jump). Переход или ветвление (РС) addr. Управление передается команде, адрес которой установлен в байте 2 и 3 текущей команды. Команды стека, ввода/вывода и управления микропроцессором • Эти команды выполняют операции помещения в стек и извлечения из него, ввода и вывода данных, обмен данными, подтверждения и запрета прерываний, останова процессора.

|

|||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-04-21; просмотров: 1501; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.133.152.151 (0.013 с.) |