Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Тема 15. Комбинационные цифровые устройства.Содержание книги

Поиск на нашем сайте

Передача и хранение информации проводится с помощью знаков, под которыми следует понимать совокупность признаков распознания какого-либо объекта или явления. Сообщение – это последовательность знаков, которые содержат некоторую информацию. Аналоговый сигнал – это такой сигнал, который принимает произвольные значения в любой момент времени Импульсный сигнал – это такой сигнал, который в течение короткого промежутка времени изменяется от другого постоянного значения (дискретные значения). С помощью импульсных сигналов можно составить сообщение, которое отображает дискретную или аналоговую информацию. Кодирование информации – это представление сообщения в виде комбинаций из числа исходных знаков, а кодированные сигналы называют цифровыми сигналами. В вычислительной технике используется код с основанием два, например, цифры 0 и 1 в двоичной системе счисления. Символу 1 соответствует положительный импульс напряжения, 0 – отрицательный или отсутствие импульса. В двоичных символах можно закодировать и передать любую информацию. К математическим основам цифровой техники относятся системы счисления (СС). Системы счисления в зависимости от основания бывают: десятичные с основанием десять, восьмеричные с основанием восемь, двоичные с основанием два и т.д. В цифровых устройствах используют элементы, которые имеют два устойчивых состояния и в этой связи двоичная система счисления чаще всего применяется для представления и обработки информации. Все системы счисления разделяются на позиционные и непозиционные. Большое распространение для информационных систем получили позиционные системы счисления. Позиционная система счисления - это система представления чисел, в которой количественные значения каждой цифры, входящий в запись числа зависит от позиции в ряду цифр, представляющих число. Позиционные системы счисления, в которых для всех разрядов числа используется одинаковое основание, называются однородными. В однородной позиционной системе счисления с основанием «к» положительное число М(к) записывают в виде последовательности к-тых цифр:

Сумматоры Сумматоры выполняют следующие операции:

и т.д.

Различают последовательные и параллельные сумматоры. Последовательные сумматоры производят суммирование разряд за разрядом. Параллельные сумматоры производят суммирование по всем разрядам сразу. В сумматоре предусматривается устройство, которое функционирует перенос в старший разряд.

Рассмотрим схему полусумматора, представленного на рис 15-1.

Рис 15-1.Логическая схема полусумматора.

Этот полусумматор обеспечивает существование одноразрядных чисел при и

Таблица истинности полусумматора

Полный одноразрядный сумматор

Полный одноразрядный сумматор складывает три одноразрядных двоичных числа

Действие этого сумматора можно описать следующими логическими функциями:

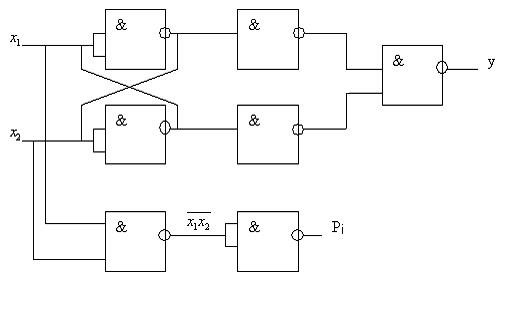

Логическая схема полного одноразрядного сумматора представлена на рис 15-2.

Рис 15-2. Логическая схема полного одноразрядного сумматора.

Условное обозначение полного одноразрядного сумматора.

Таблица истинности полного одноразрядного сумматора.

Полный сумматор, построенный на двух полусумматорах.

Рис 15-3.Схема полного сумматора, построенного на 2х полусумматорах

Таблица истинности полного сумматора.

Сумматор по модулю два.

Рис 15-4. Схема сумматора по модулю два.

Таблица истинности логической функции сумматора по модулю два.

(единица в следующий разряд)

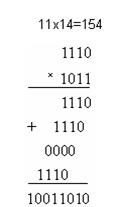

Умножители Рассмотрим умножение двоичных чисел на конкретном примере:

Из примера видно, что умножение двоичных чисел выполняется достаточно просто, так как умножение производится на «1» и «0». При этом множитель сдвигается каждый раз влево на один разряд и затем они суммируются. Эту операцию можно реализовать с помощью регистра сдвига и сумматора. Шифраторы(СД). Это комбинаторное цифровое устройство кодирования, преобразующие десятичные числа в двоичную систему счисления.

Допустим на пульте находится 10 клавиш (от 0 до 9) и при нажатии одной из клавиш подается единичный сигнал x0,x1,..,x9, а на входе появится двоичный код. Следовательно необходим в данном случае преобразователь, имеющий 10 входов и 4 выхода. На входе должна появится «1» при нажатии любой нечетной клавиши. Для остальных цифр кодирование смотри логическую схему шифратора.

Логическая схема шифратора показана на рис 15-5.

Рис 15-5. Логическая схема шифратора.

Действие шифратора можно описать следующими логическими функциями:

Условное обозначение шифратора.

Таблица истинности шифратора

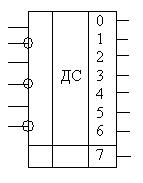

Дешифраторы Дешифратор-это узел, преобразующий код, поступающий на его входы, в сигнал только на одном из его выходов. Дешифратор двоичного n-разрядного кода имеет

Рассмотрим схему линейного дешифратора на три входы(рис 15-6)

Рис 15-6. Логическая схема дешифратора.

Таблица истинности для дешифратора сможет быть представлена такой же как для дешифратора только наоборот.Распознавание дешифратора двоичных чисел состоит в том, что в зависимости от номера набора, поступившего на его вход сигнал «1», появится на одном определенном выходе (остальные выходы дадут «0»)

Таблица истинности для данного линейного дешифратора на 3 входа: (полный дешифратор 3-х разрядных чисел)

Рассмотрение данной схемы (рис 4-6) показывает, что каждая из функций представляет конъюнкцию 3-х переменных и может быть реализована с помощью 3-х ходовых схем логического элемента «И». Следует заместитель, что бывают дешифраторы с синхронизирующим входом, при котором дешифрация кода будет произведена во время подачи синхронимпулься, который поступает на вход синхронизации(обычно обозначается «с»). Кроме того еще должен быть управляющий единичный сигнал.

Условное обозначение 3-х линейно дешифратора.

Преобразование кодов. Общие понятия: Преобразователи кодов – это устройства для автоматического изменения по заданному алгоритму для соответствия между входными и выходными кодами без изменения их смыслового содержания. 1 тип: Элементы входного кода соответствует элементу выходного кода. Здесь эту роль выполняют последовательно-параллельные регистры. Такое устройство с объектом по 2-х проводному каналу на выходе передатчика строит преобразование параллельного кода в последовательный на выходе и наоборот.

2 тип: Элементы выходного кода не соответствуют элементам входного.

1)сначала входного n-разрядный код преобразовывается в промежуточный дешифратор 2)промежуточный преобразуется в требуемый n-разрядный код шифратором.

Мультиплексоры(коммутаторы).

Мультиплексор (MUX) – это комбинационное цифровое устройство, которое осуществляет коммутацию двоичного сигнала Хn с одного из n-входов на всего один выход. Процесс происходит в присутствии С-синхронизируещего импульса, а номер входа «n", подключаемого к выходу определяется сигналами А0, А1 и т.д. на так называемых адресных входах. (Адрес – это двоичная запись номера «n» коммутирующего входа). Мультиплексор – это узел, осуществляющий преобразования параллельных цифровых кодов в последовательные.

Рис 15-7. Логическая схема мультиплексора с синхронизации входом

Условное обозначение мультиплексора

Таблица истинности мультиплексора

Формула перехода мультиплексора для выхода y:

Рис.15-8. Логическая схема мультиплексора без синхронизирующего входа. Действие мультиплексора без синхронизирующего входа можно описать следующей логической функцией F1:

Таблица истинности:

Демультиплексор Демультиплексор или распределитель выполняет функцию обратную мультиплексора, т.е. преобразует последовательный вход в параллельный. Он осуществляет подключения входного сигнала на один из нескольких своих выходов (каналов направления). Для случая, когда n=4, демультиплексор в соответствии с сигналами на адресных входах V1 и V2 передает двоичную информацию со входа на один их четырех выходов y1, y2, y3, y4. В схеме даны описания логическими функциями перехода для каждого выхода.

Рис. 15-9. Логическая схема демультиплексора.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-01-26; просмотров: 324; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.118.33.186 (0.008 с.) |

, где а – содержимое разряда; n- номер разряда. Чтобы записать числа в различных системах счисления используются различные цифры: в 2СС (0;1), в 8СС (0,1,2,3,4,5,6,7), в 16СС (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F). Согласно (1) приведём примеры записи целых чисел в различных системах счисления и перевода в десятичную систему:

, где а – содержимое разряда; n- номер разряда. Чтобы записать числа в различных системах счисления используются различные цифры: в 2СС (0;1), в 8СС (0,1,2,3,4,5,6,7), в 16СС (0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F). Согласно (1) приведём примеры записи целых чисел в различных системах счисления и перевода в десятичную систему:

=1.Значение младшего разряда сопровождается переходом в старший разряд.

=1.Значение младшего разряда сопровождается переходом в старший разряд. и имеет два выхода (

и имеет два выхода ( и

и  )

)

-выходов в связи с тем, что каждому из двух значений входного кода должен соответствовать единичный сигнал на одном из выходов дешифратора.

-выходов в связи с тем, что каждому из двух значений входного кода должен соответствовать единичный сигнал на одном из выходов дешифратора.