Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Триггеры в интегральном исполнении.Содержание книги

Поиск на нашем сайте

Обычно триггеры выполняют в виде интегральных микросхем. Такие триггеры состоят из логических элементов и блок-схема такого симметричного триггера со счетным входом изображена на рис. 14-18 Он состоит из алогических элементов «ИЛИ» (цепь запуска) и «НЕ» (однокаскадные усилители -инверторы), соединенных цепями перекрестной обратной связи. Симметричный триггер работает следующим образом. Предположим, что на вход первого инвертора HE1 сигнал не подан - «О». В этом случае на его выходе появится сигнал «1». Этот сигнал, пройдя через логический элемент ИЛИ2, поступит на инвертор НЕ1. В результате на выходе инвертора НЕ2 установится напряжение, соответствующее «О». Сигнал «О» поступит на вход элемента ИЛИ1 а далее на вход инвертора HE1. Если учесть предположение, что входные сигналы триггера равны «О» то триггер все время будет находится в устойчивом состоянии. Это состояние изменится только тогда, когда на Bxl будет подан сигнал «1». Процесс перехода триггера в новое устойчивое состояние произойдет аналогично описанному выше.

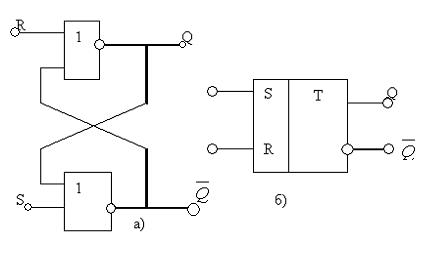

Рис. 14-18 Блок-схема и условное обозначение статического триггера.

Рис. 14-19. Схема для установочного запуска триггеров. Симметричные триггеры, применяемые в ЭВМ, должны отвечать следующим требованиям: 1.Триггер должен сохранять устойчивое состояние в реальных условиях эксплуатации ЭВМ, т.е. 2.При каждом воздействии запускающего импульса триггер должен бесперебойно срабатывать. 3.Триггер должен обладать заданной нагрузочной способностью, т.е. он должен нормально рабо Резисторы R1, R2,..., Rn включаются для выравнивания токов во всех каналах запуска, диоды VД1,... VДn применяются для разделения цепей установочного запуска. В случае применения триггеров со счетным входом установочный импульс может подаваться на коды триггеров после дифференцируемых емкостей. Интегральная технология и использование методов алгебры логики позволили создать большое число различных триггеров на базе логических элементов, различающихся структурой цепей управления и режимами работы. Триггер состоит из цепей управления и запоминающих устройств и имеет один, два (или более) входа и два выхода. Каждый из входов имеет определенное функциональное назначение, которое отражается в обозначении данного входа (R, S, К, D и т. д.). Цепи управления, в которые поступают входные (информационные) сигналы, преобразуют их в сигналы для запоминания и считывания. Запоминающие устройства состоят из двух плеч, в каждом из которых одновременно хранятся сколь угодно долго два сигнала, один из которых соответствует логической 1, другой — логическому 0. Выход триггера Q, с которого в исходном состоянии снимается высокий потенциал, обычно называют прямым, другой — инверсным (обозначается Кроме симметричных триггеров в зависимости от выполняемых функций различают еще триггеры с раздельный запуском (RS- триггер), синхронный (RCS- триггер), со счетным запуском (Т-триггер), с элементами задержки или логическими переключающими схемами в цепях управления (D-триггер), универсальные JK -триггеры), на базе которых могут быть реализованы остальные типы триггеров. По способу записи информации все триггеры подразделяют на асинхронные, в которых информация записывается непосредственно при поступлении входного сигнала, и тактируемые (синхронные), записывающие входную информацию только при поступлении разрешающего тактового импульса. Названия триггеров составляют из типов входов. Синхронные триггеры бывают со статическими и динамическими входами. Динамическим называют такой вход, действие поданных уровней сигналов, на который прекращается после соответствующего переключения триггера. Рассмотрим примеры построения некоторых типов триггеров на базе логических элементов либо «ИЛИ — НЕ», либо «И — НЕ» . RC-триггер.

Таюлица истинности асинхронного RS триггера (С).

рис. 14-20. Асинхронный RS триггер на двух логических элементах ИЛИ-НЕ, а и его графические обозначения(б) Переключают триггер в другое состояние тподачей на один из входов сигнала логической 1, при подаче на вход R уровня 1, а на вход S уровня 0 на инверсном выходе устанавливается сигнал Q=0, который переводит триггер в состояние 1, соответствующее Q = 1. Аналогично происходит переключение триггера и при подаче уровня логической единицы на вход S. Для RS-триггера существует запретная комбинация входных сигналов. Триггер теряет свойства (его состояние становится неопределенным) при одновременной подаче на входы R и S уровня логической 1. Если отпирающие импульсы действуют одновременно, то триггер оказывается временно в симметричном состоянии, из которого он может выйти равновероятно в любое из двух устойчивых состояний. Таким образом, результат неоднозначный, что недопустимо. В схеме рис. 14-21 элементы «ИЛИ — НЕ» могут быть заменены элементами «И — НЕ». Свойства триггера при этом сохраняются, но управление им должно производиться уровнями логического 0. Такой триггер можно рассматривать как RS-триггер с инверсными входами. Более сложные триггеры D-, Т- и JK-типов выполняют на базе одного или двух RS-триггеров с использованием в цепях управления элементов задержки или логических переключающих схем. Наибольшее распространение получили триггеры с логическими переключающими схемами в цепях управления, поскольку интегральное исполнение элементов задержки затруднено.

Таблица истинности асинхронного RS триггера. рис. 14 -21 Асинхронный RS триггер на двух логических элементах И-НЕ (a) и его графическое изображение(б) RCS-триггер (синхронный) Если необходимо, чтобы триггер реагировал на изменение входного сигнала только в определённый интервал времени, то используют триггерные устройства с синхронизацией (рис.14-22). Это - триггеры RSC - типа. Они имеют дополнительный синхронизирующий вход С. Если С = 0, то при любых значениях R и S сигналы на входах RS-триггера логические "1" и состояние RS-триггера не меняется. Если C = 1,S=1,R = 0,to формируется нулевой сигнал на выходе Э1 и RS-триггер устанавливается в "1" (Q= 1, Если С = 1, S = 0, R = 1, то появляется "0" на выходе Э2 и RS-триггер устанавливается в "0"). Значение входных сигналов S = 1,R=1,C=1 приводит к неопределенному состоянию устройства. Следовательно, такое состояние схемы является запрещенным.

Таблица истинности синхронного RS триггера.

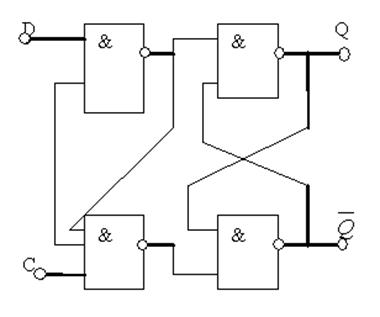

Рис.14-22 Синхронный RCS-триггер (a), графическое изображение(б) и таблица истинности(в) D-триггер. D-триггер построен на логических элементах «И-НЕ» и изображен на рис 14-23.

Рис 14-23. Логическая схема D-триггер D-триггер- это триггер, который повторяет на своем выходе состояние входа. Из рис 3-23 видно, что D-триггер можно образовать из RS-триггеров, если на их входы одновременно подавать инверсные сигналы. Информация в D-триггерах хранится за счет синхронизации и в этой связи D-триггеры имеют информационный вход D и вход синхронизации С. В описываемом триггере сигнал на входе передается на выход только по сигналу синхронизации и этот триггер называется триггером с запоминанием информации (триггер задержки). Условное графическое обозначение D-триггера показано на рис 14-24.

Рис 14-24. D-триггер в интегральном исполнении. Таблица истинности D-триггера.

Т-триггер. Т-триггер состоит из двух синхронных RS-триггеров M и N, которые имеют синхронизирующие входы С и счетный вход Т и логический элемент НЕ (рис 14-25).

Рис 14-25. Т- триггер с синхронизирующим «С» входом в интегральном исполнении Если JK-триггер. Это наиболее универсальный триггер, который строится на основе двухступенчатого RS-триггера и двух логических элементов И-НЕ (рис 14-26).

Рис 14-26. Схема JK-триггера в интегральном исполнении.

При комбинации сигналов если J=1 и к=0, то при Q=0 получают на S(триггер М) единицу. После подачи первого синхронизирующего импульса на С, триггер установится в состояние Q=1. При комбинации сигналов J=1 и k=0,то при Q=1 на S и R (триггера М) будут равны “0” и при подаче синхронизирующего импульса на С, триггер не будет изменять своего состояния. Таким же образом по отношению к состоянию Q=0 действует сигнал k=1 при j=0. При комбинации сигналов J=K=1, то получают S=1 (триггер М) и R=0 (триггер М) при Q=0 и S=0(триггер М) и R=0 (триггер М) при Q=1. Таким образом триггер переключается в противоположное состояние при соответствующем фронте сигнала на С. Условное графическое изображение JK-триггера показано на рис 14-27.

Рис 14-27. Условное графическое изображение JK-nhbuuthf/ Таблица истинности JK-триггера.

Таблица получения из JK-триггерa. RS, T, D-триггеров

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2017-01-26; просмотров: 822; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.216.146.152 (0.009 с.) |

).

). Буквы R и S означают: R - раздельный вход установки в состояние О, S — раздельный вход установки в состоянии 1.

Буквы R и S означают: R - раздельный вход установки в состояние О, S — раздельный вход установки в состоянии 1.

- логический уровень на этом выходе после подачи импульса синхронизации.

- логический уровень на этом выходе после подачи импульса синхронизации.

, то на выходных триггера М будут такие же сигналы, а на входе S триггера М появится 1, (на выходе R=0). При подаче сигнала «1» на Т автоматически отключает триггер N от M и в то же время обеспечивает запись в него сигналов наS=1, наR=1. При условии, что Т=0 обеспечивает отключение триггера М и запись сигналов с его выходов проходит в триггер N, который переводится в состояние Q = 0,

, то на выходных триггера М будут такие же сигналы, а на входе S триггера М появится 1, (на выходе R=0). При подаче сигнала «1» на Т автоматически отключает триггер N от M и в то же время обеспечивает запись в него сигналов наS=1, наR=1. При условии, что Т=0 обеспечивает отключение триггера М и запись сигналов с его выходов проходит в триггер N, который переводится в состояние Q = 0,

Q(t+1)

Q(t+1)

Q(t)

Q(t)

Q(t)

Q(t)