Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Дифференциальный вход с усилениемСодержание книги

Поиск на нашем сайте

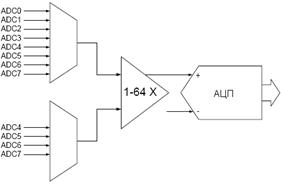

При выборе дифференциального входа с усилением в качестве неинвертирующего входа может быть выбран любой из выводов аналоговых входов, а в качестве инвертирующего входа - выводы аналоговых входов 4…7. При использовании усилительного каскада, дифференциальный аналоговый вход вначале подвергается выборке и усилению, а затем подается в АЦП. При работе с дифференциальным входом с усилением, АЦП необходимо перевести в знаковый режим. Доступны следующие коэффициенты усиления: 1, 2, 4, 8, 16, 32 и 64.

Рисунок 25.3. Измерение дифференциального сигнала с усилением Несимметричный вход При выполнении несимметричных измерений в качестве входа могут использоваться любые выводы аналоговых входов. Несимметричные измерения можно выполнять как в знаковом, так и в беззнаковом режимах. В знаковом режиме инвертирующий вход АЦП подключается к внутренней общей цепи.

Рисунок 25.4. Несимметричное измерение в знаковом режиме В беззнаковом режиме инвертирующий вход АЦП соединен с напряжением, которое равно половине опорного напряжения (VREF) за вычетом фиксированного смещения. Номинальное значение смещения равно: ∆V = VREF x 0.05. Поскольку АЦП является дифференциальным, его беззнаковый режим реализуется путем внутреннего деления опорного напряжения на два. В результате, входной диапазон на неинвертирующем несимметричном входе будет простираться от VREF до нуля. Вычет смещения необходим для обнаружения модулем АЦП пересечения нуля в беззнаковом режиме, а также для калибровки любого положительного смещения, когда уровень внутренней общей цепи МК больше уровня внешней общей цепи. Подробности см. на рисунке 25.11.

Рисунок 25.5. Несимметричное измерение в беззнаковом режиме Внутренние входы К входу АЦП можно подключить один из четырех внутренних аналоговых сигналов. · Выход датчика температуры · Напряжение бэндгап-элемента · Поделенное напряжение VCC · Выход ЦАП Оцифровка напряжения встроенного датчика температуры дает возможность учитывать в программе информацию о текущей температуре внутри микроконтроллера. На этапе производственных испытаний МК выполняется оцифровка напряжения внутреннего датчика температуры при фиксированной температуре. Результат оцифровки записывается в сигнатурный код производителя и может использоваться в дальнейшем для калибровки датчика температуры. Напряжение бэндгап-элемента - точное опорное напряжение, которое доступно внутри микроконтроллера и используется для формирования других внутренних опорных напряжений. Предусмотрена возможность оценки напряжения VCC по поделенной в 10 раз его версии. Таким образом, когда VCC = 1.8 В на вход АЦП подается 0.18 В, а когда VCC = 3.6 В, то к АЦП поступает 0.36 В. К входу АЦП также можно подключить выходное напряжение ЦАП. Это напряжение подается прямо с выхода ЦАП, а не с выходов схемы выборки-хранения, которые имеются у АЦП. Некоторые внутренние сигналы перед их оцифровкой требуют включения в работу. Подробности о том, как выполнить такое включение, см. в описании соответствующих модулей. При измерении внутренних сигналов в знаковом режиме, неинвертирующий вход подключается к внутренней общей цепи.

Рисунок 25.6. Измерение внутренних сигналов в знаковом режиме В беззнаковом режиме неинвертирующий вход подключается к фиксированному уровню напряжения, который равен половине опорного напряжения (VREF) минус фиксированное смещение, т.е. аналогично беззнаковому несимметричному измерению. Подробности см. на рисунке 25.11.

Рисунок 25.7. Измерение внутренних сигналов в беззнаковом режиме Каналы АЦП Чтобы упростить использование модуля АЦП, у него предусмотрено четыре отдельных регистра управления мультиплексорами, каждому из которых соответствует свой регистр результата. Регистровая пара мультиплексора/результата называется каналом АЦП (см. рисунок 25.1). Каждый канал АЦП раздельно настраивается на измерение различных входных источников, использует различные условия запуска преобразования, события и прерывания. Результат преобразования запоминается в разных регистрах результата. Вот один из вариантов использования каналов АЦП: одна пара регистров мультиплексора/результата настроена на выполнение несимметричных измерений, запускаемых сигналом события, другая пара регистров мультиплексора/результата отвечает за дифференциальное измерение, инициированное другим сигналом события и, наконец, две оставшихся пары регистров измеряют еще два входных источника под управлением программы. Все каналы АЦП для выполнения преобразования используют один и тот же АЦП, однако, благодаря его конвейерной архитектуре, новое преобразование можно запускать по каждому циклу синхронизации АЦП. Это означает, что одновременно и независимо, не требуя изменений настроек мультиплексора, могут прогрессировать несколько преобразований. Результат преобразований каждого канала сберегается в отдельном регистре. По мере выполнения очередных преобразований в этом канале, обновляться будет именно его регистр результата, не затрагивая прочие регистры результата. Благодаря такому механизму преобразований, снижается сложность программы, а различные программные модули получают возможность начать преобразования и считать их результат полностью независимого друг от друга. Выбор опорного напряжения В качестве опорного напряжения АЦП (VREF) можно выбрать следующие напряжения: · Точное внутреннее напряжение 1.00В. · Внутреннее напряжение VCC/1.6В. · Внешнее напряжение, поданное на вывод AREF порта А. · Внешнее напряжение, поданное на вывод AREF порта B.

Рисунок 25.8. Выбор опорного напряжения АЦП 25.6 Результат преобразования АЦП можно настроить на работу в знаковом или беззнаковом режиме. Данная настройка является глобальной и, таким образом, распространяется на весь модуль АЦП и на все его каналы. В знаковом режиме, возможно измерение как отрицательных, так и положительных напряжений на несимметричном или дифференциальном входе. При использовании 12-битной разрешающей способности, максимальным значением (TOP) знакового результата является 2048, а все значения результата лежат в пределах -2048…+2047 (0xF800…0x07FF). В беззнаковом режиме, максимальное значение равно 4095, а все значения результата принадлежат диапазону 0…4095 (0…0x0FFF). Если какой-либо из входов АЦП настроен на дифференциальное измерение, необходимо использовать знаковый режим. В беззнаковом режиме возможно измерение только внешних или внутренних несимметричных сигналов. Результат аналогово-цифрового преобразования (RES) записывается в один из регистров результата. Передаточная функция АЦП имеет следующий вид: RES = (VINP - VINN)·GAIN·TOP/VREF, VINP и VINN - напряжения на неинвертирующем и инвертирующих входах АЦП. GAIN всегда равно 1, если не используется дифференциальное измерение с усилением. Программно можно задать разрешающую способность результата 8 или 12 бит. Преобразование с более низкой разрешающей способностью выполняется быстрее. О том, как рассчитать задержку распространения см. в 25.9 "Синхронизация и временная диаграмма преобразования АЦП". Регистры результата являются 16-битными. 8-битный результат всегда представляется в 16-битном регистре результата с правым выравниванием. Правое выравнивание означает, что 8 младших бит результата помешаются в младший байт регистра результата. 12-битный результат может быть представлен как с левым, так и с правым выравниванием. Левое выравнивание означает, что 8 старших бит результата помещаются в старший байт регистра результата. Когда АЦП работает в знаковом режиме, старший бит результата является битом знака. В 12-битном режиме с правым выравниванием, бит знака (бит 11) копируется во все неиспользуемые старшие биты, т.е. биты 12…15. Это необходимо для того, чтобы хранящееся в регистре результата 16-битное значение автоматически воспринималось в программе, как 16-битное знаковое значение. Аналогичным образом, в 8-битном режиме бит знака (бит7) копируется во все биты старшего байта. На рисунках 25.9…25.11 представлены входные диапазоны и представление 12-битного результата с правым выравниванием для различных входов.

Рисунок 25.9. Знаковый дифференциальный вход с усилением: входной диапазон и представление результата

Рисунок 25.10. Знаковый несимметричный внешний или внутренний вход: входной диапазон и представление результата

Рисунок 25.11. Беззнаковый несимметричный внешний или внутренний вход: входной диапазон и представление результата Функция сравнения Модуль ADC поддерживает функцию 12-битного сравнения. Для хранения 12-битного значения, которое соответствует аналоговому пороговому напряжению, предусмотрен регистр сравнения модуля ADC. Каждый из каналов ADC можно настроить на автоматическое выполнение сравнения результата преобразования с заданным 12-битным значением и генерацию прерывания или события в случае, если результат преобразования больше или меньше порога. Все четыре канала ADC работают с одним и тем же регистром сравнения. 25.8 Запуск преобразования Перед тем как запустить преобразование, необходимо выбрать требуемые входные источники для одного или более каналов ADC. Запустить преобразование в канале ADC можно либо программной записью единицы в бит запуска преобразования канала ADC, либо событием системы событий. Допускается одновременная запись бит запуска преобразования нескольких каналов ADC или использование одного и того же события для одновременного запуска преобразований в нескольких каналах ADC. Используя эту возможность, можно добиться сканирования нескольких или всех каналов ADC под управлением одного события. 25.9 Синхронизация и временная диаграмма преобразования АЦП Модуль АЦП синхронизируется сигналом синхронизации УВВ. Частота сигнала синхронизации УВВ может быть поделена внутри модуля АЦП. Результирующий сигнал - сигнал синхронизации АЦП (ClkADC). Его частота должна лежать в допустимых для модуля АЦП пределах.

Рисунок 25.12. Предделитель АЦП Максимальная частота преобразований АЦП равна частоте его синхронизации (fADC). АЦП может инициировать новое преобразование по каждому циклу синхронизации АЦП. Частота преобразования = fADC Задержка распространения АЦП определяется по выражению: Задержка распространения = (1 + 0.5·RES + GAIN)/fADC, где RES - разрешающая способность АЦП (8 или 12 бит). Задержка распространения возрастает на один дополнительный цикл синхронизации АЦП после активизации усилительного каскада (GAIN). Несмотря на то, что задержка распространения составляет более одного цикла синхронизации АЦП, конвейерная архитектура исключает любые ограничения на соотношение частоты преобразования и задержки распространения. 25.9.1 Одиночное преобразование без усиления На рисунке 25.13 показана временная диаграммы работы АЦП при выполнении одиночного преобразования без усиления. Для фактического запуска преобразования АЦП необходимо, чтобы записанный бит запуска преобразования или событие запуска преобразования (START), удерживалось в активном состоянии минимум один цикл синхронизации УВВ перед началом цикла синхронизации АЦП (см. залитую серым цветом наклонную область на графике START). Выборка источника аналогового входа выполняется за первую половину первого цикла и, таким образом, время выборки всегда равно половине периода синхронизации АЦП. Снижение или увеличение частоты синхронизации АЦП оказывает прямое влияние на величину времени выборки. Старший бит результата преобразования оцифровывается первым, а на оцифровку остальных бит затрачивается 3 (8-битное преобразование) или 5 (12-битное преобразование) циклов синхронизации АЦП. На преобразование одного бита затрачивается половина периода синхронизации АЦП. По ходу последнего цикла выполняется подготовка результата преобразования, а затем устанавливается флаг прерывания. Результат доступен для считывания в регистре результата.

Рисунок 25.13. Временная диаграмма одиночного преобразования без усиления 25.9.2 Одиночное преобразование с усилением На рисунке 25.14 показана временная диаграмма работы АЦП при выполнении одиночного преобразования с усилением. Как было показано в 25.2 "Обзор" усилительный каскад расположен перед АЦП. Это означает, что вначале выполняются выборка и усиление источника аналогового входа в усилительном каскаде, а уже затем АЦП выполняет преобразование выборки усиленного аналогового напряжения. По сравнению с одиночным преобразованием без усиления здесь требуется один дополнительный цикл синхронизации АЦП (между START и выборкой АЦП) для выборки и усиления в усилительном каскаде. Время выборки в усилительном каскаде равно половине цикла синхронизации АЦП.

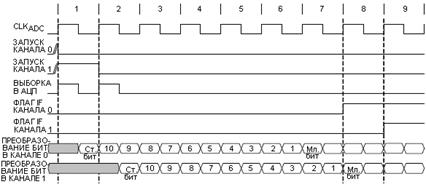

Рисунок 25.14. Временная диаграмма одиночного преобразования с усилением 25.9.3 Одиночные преобразования в двух каналах АЦП На рисунке 25.15 показана временная диаграмма работы АЦП при выполнении одиночных преобразований в двух каналах АЦП. Благодаря конвейерной архитектуре АЦП, второе преобразование можно запустить в следующем цикле синхронизации АЦП после запуска первого преобразования. В этом примере оба преобразования запускаются одновременно, но фактически канал 1 АЦП (CH1) не запускается, пока не завершится выборка и преобразование старшего бита в канале 0 (CH0).

Рисунок 25.15 25.9.4 Одиночные преобразования в двух каналах АЦП с усилением в канале 0 На рисунке 25.16 показана временная диаграмма преобразований в двух каналах АЦП и с усилением в канале 0. Поскольку усилительный каскад добавляет один цикл на выборку и усиление, выборка канала 1 также задерживается на один цикл синхронизации АЦП вплоть до завершения выборки и преобразования старшего бита в канале 0.

Рисунок 25.16. Временная диаграмма одиночных преобразований в двух каналах АЦП с усилением в канале 0 25.9.5 Одиночные преобразования в двух каналах АЦП с усилением в канале 1 Временная диаграмма преобразований в двух каналах АЦП и с усилением в канале 1 показана на рисунке 25.17.

Рисунок 25.17. Временная диаграмма преобразований в двух каналах АЦП

|

||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 837; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.223 (0.01 с.) |