Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

STATUS - регистр статуса модуля SPI

· Бит 7 - SPIF: флаг прерывания модуля SPI Данный флаг становится равным единице по завершении последовательной передачи данных из регистра данных и последовательного приема данных в этот же регистр. Флаг IF также устанавливается, если модуль SPI работает в ведущем режиме и на его, настроенный как вход, вывод SS подается низкий уровень. Флаг IF сбрасывается аппаратно при переходе на вектор прерываний. Альтернативно, флаг SPIF может быть сброшен первым чтением регистра STATUS с установленным флагом IF и при выполнении доступа к регистру данных. · Бит 6 - WRCOL: флаг обнаружения ошибочной записи Бит WRCOL становится равным единице, если во время передачи выполняется запись в регистр данных. Сброс бита WRCOL происходит при первом чтении регистра STATUS с установленным битом WRCOL и при осуществлении доступа к регистру данных. · Бит 5:0 - Res: резерв Данные биты являются резервными и всегда считываются с нулевыми значениями. Для совместимости с более новыми МК, выполняя запись в этот регистр, всегда записывайте нули в резервные биты. DATA - регистр данных SPI

Регистр данных используется для передачи и приема данных. Запись в регистр инициирует передачу данных методом последовательных сдвигов через выходную линию шины SPI. При чтении регистра возвращается значение из буферного регистра, в котором сберегается последний успешно принятый байт данных. Обзор регистров

Векторы прерываний модуля SPI Таблица 20.5. Вектор прерываний модуля SPI и значение смещения его адреса

Модуль USART Отличительные особенности · Полнодуплексная работа (отдельные регистры у приемника и передатчика)

· Асинхронная или синхронная работа · Синхронная передача, тактируемая ведущим или подчиненным устройством · Улучшенный генератор скорости · Поддержка посылок с 5, 6, 7, 8 или 9 битами данных и 1 или 2 стоп-битами · Генерация и проверка паритета (четность/нечетность) на аппаратном уровне · Обнаружение ошибок переполнения данных и ошибок в посылке · Фильтрация шума, в т.ч. обнаружение ложного старт-бита и цифровой фильтр низких частот · Отдельные прерывания по завершению передачи, по опустошению регистра данных передатчика и по завершению приема · Режим мультипроцессорной связи · Режим асинхронной связи с удвоенной скоростью · Режим ведущего SPI с синхронной передачей данных по трем линиям · Поддержка всех четырех режимов SPI (режим 0, 1, 2 и 3) · Настройка передачи первым младшего или старшего бита данных · Работа с очередями (двойная буферизация) · Высокоскоростная работа (fXCK.MAX = fPER/2) · Модуль IRCOM для IrDA-совместимой модуляции/демодуляции Обзор Модуль универсального синхронно-асинхронного последовательного приемника и передатчика (USART) - чрезвычайно гибкий модуль последовательной связи. Модуль USART поддерживает полнодуплексную синхронную или асинхронную передачу данных. USART может быть переведен в режим ведущего SPI-совместимого интерфейса. Передача выполняется посылками, формат которых задается пользователем. Это позволяет добиться совместимости с различными стандартами. Модуль USART буферизован в обоих направлениях, что позволяет добиться непрерывности передачи данных без каких-либо пауз между посылками. Предусмотрены отдельные векторы прерываний по завершению приема и по завершению передачи, что позволяет реализовать управление связью полностью по прерываниям. Ошибки в посылке и переполнение буфера обнаруживаются на аппаратном уровне, о чем сигнализируют отдельные флаги статуса. Также поддерживается генерация и проверка паритета (четность или нечетность). Функциональная схема модуля USART показана на рисунке 21.1. Его основными компонентами являются генератор синхронизации, передатчик и приемник (выделены пунктирной линией).

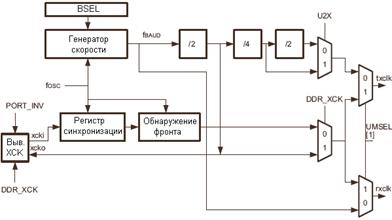

Логика генерации синхронизации содержит дробный генератор скорости, позволяющий генерировать множество скоростей. В неё также входит логика синхронизации, связанная с внешним входом синхронизации работающего в синхронном режиме подчиненного устройства. Передатчик состоит из одного буфера записи (DATA), сдвигового регистра, генератора паритета и логики управления, предназначенные для обработки посылок различного формата. Буфер записи позволяет непрерывно передавать данные без каких-либо задержек между посылками. Приемник состоит из двухуровневого буфера (DATA) и сдвигового регистра. Для гарантирования надежности синхронизации и подавления шума во время асинхронного приема данных предусмотрены блоки восстановления данных и синхронизации. Кроме того, в приемник входят блоки обнаружения ошибок в посылке, переполнения буфера и паритета. После перевода модуля USART в режим ведущего SPI-совместимого устройства, вся специфическая логика интерфейса USART отключается, а в работе остаются лишь буферы приема и передачи, сдвиговые регистры и генератор скорости. Управление выводами и генерация прерываний остаются идентичными в обоих режимах работы. Использование регистров тоже остается прежним в обоих режимах, но их функциональность отличается при определенных настройках. Совместно с одним из USART может работать модуль IRCOM, предназначенный для IrDA 1.4-совместимой модуляции и демодуляции импульсов на скорости до 115.2 кбит/сек. Более детально о его работе см. в разделе 22 "Модуль инфракрасной связи IRCOM". Генерация синхронизации Сигнал синхронизации, который задает скорость связи и используется для тактирования сдвигового регистра и выборки бит данных, генерируется внутренним дробным генератором скорости или поступает с вывода синхронизации передачи XCK. Поддерживаются пять режимов генерации синхронизации: асинхронные режимы с нормальной и удвоенной скоростью, ведущий и подчиненный синхронные режимы, а также ведущий SPI режим.

Рисунок 21.2. Функциональная схема логики генерации синхронизации

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 450; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.178.157 (0.011 с.) |