Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Восстановление синхронизацииСодержание книги

Поиск на нашем сайте

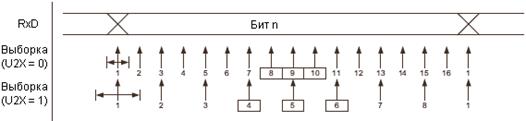

Логика восстановления синхронизации предназначена для синхронизации внутреннего источника синхронизации с входящими последовательными посылками. На рисунке 21.6 показан процесс выборки старт-бита входящей посылки. Частота выборок в 16 раз (8 раз) больше частоты генератора скорости в нормальном режиме работы (в режиме с удвоенной скоростью). Горизонтальные стрелки показывают диапазон отклонения синхронизации в процессе выборки. Обратите внимание, что в режиме с удвоенной скоростью отклонение более существенно. Выборки, обозначенные цифрой 0, выполняются, когда линия RxD находится в состоянии IDLE, т.е. когда по ней не выполняется передача данных.

Когда логика восстановления синхронизации обнаруживает на линии RxD переход из высокого (IDLE) в низкое состояние инициируется последовательность обнаружения старт-бита. На рисунке 21.6 выборка первого низкого уровня отмечена номером 1. Далее, по выборкам 8, 9 и 10 в нормальном режиме и выборкам 4, 5 и 6 (указанные выборки обведены прямоугольной рамкой) в режиме с удвоенной скоростью логика восстановления синхронизации принимает решение о действительности принятого старт-бита. Если две или более выборок равны нулю (принцип мажоритарного голосования), то принятый старт-бит считается действительным, логика восстановления синхронизации считается засинхронизированной и начинается процедура восстановления данных. Если же обнаруживается, что две или более выборок имеют высокий уровень, то старт-бит считается ложным, а приемник возвращается к поиску очередного перехода из высокого в низкое состояние. Процесс синхронизации повторно применяется к каждому старт-биту. Восстановление данных Блок восстановления данных выполняет 16 (8) выборок каждого бита данных в нормальном режиме (в режиме с удвоенной скоростью). Процесс выборки бит данных и бита паритета показан на рисунке 21.7.

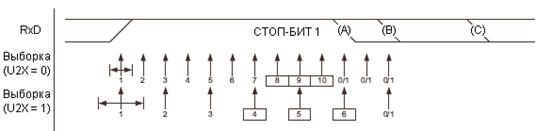

Так же как и при обнаружении старт-бита, для определения уровня принятого бита данных используется принцип мажоритарного голосования, который применяется к трем центральным выборкам (выделены прямоугольной рамкой). Механизм мажоритарного голосования действует как фильтр низких частот по отношению к принимаемому на выводе RxD сигналу. Аналогичным образом, процесс определения уровня применяется к каждому биту вплоть до завершения приема посылки, в т.ч. первый стоп-бит (остальные стоп-биты в расчет не берутся). Если обнаруживается, что стоп-бит равен нулю, устанавливается флаг ошибки в посылке (FERR). На рисунке 21.8 показаны выборка стоп-бита, а также ближайший момент, в который допустимо появление старт-бита следующей посылки.

Появление нового перехода из высокого состояния в низкое, указывающее на старт-бит новой посылки, считается допустимым после выполнения последней выборки первого стоп-бита, участвующей в мажоритарном голосовании. В режиме нормальной скорости, выборка первого низкого уровня в серии выборок стоп-бита может быть в точке (A), а в режиме двойной скорости - несколько позже: в точке (B). Точка (C) оказывает на полную длительность стоп-бита на номинальной скорости. Преждевременное обнаружение стоп-бита влияет на рабочий диапазон приемника.

|

||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 303; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.143.7.53 (0.006 с.) |