Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

CCxBUFL - младший регистр буфера захвата или сравнения xСодержание книги

Поиск на нашем сайте

268. Биты 7:0 - CCxBUF[7:0] В данных битах хранятся 8 младших бит 16-битного регистра буфера захвата или сравнения. Обзор регистров

Обзор векторов прерываний Таблица 14.8. Векторы прерываний таймера-счетчика и значения смещения их адресов

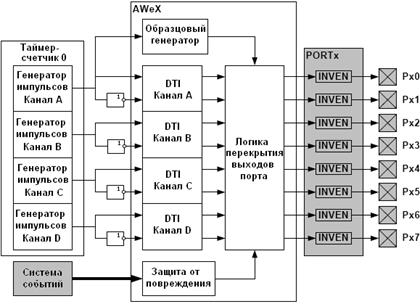

Прим.: 1. Имеется только у 16-битного-таймера счетчика с 4 каналами захвата/сравнения. Блок расширения возможностей генерации импульсов AWeX Отличительные особенности 2. 4 блока генерации паузы неперекрытия (на 8 выводах) 3. 8-битная разрешающая способность 4. Отдельная настройка паузы неперекрытия для верхнего и нижнего уровней 5. Двойная буферизация паузы неперекрытия 6. Остановка таймера во время паузы неперекрытия (опционально) 7. Управляемая по событиям защита от повреждения 8. Одноканальная работа с несколькими выходами (для управления BLDC-двигателем) 9. Образцовый генератор с двойной буферизацией 10. Возможность увеличения разрешающей способности генерации импульсов на 2 бита (в 4 раза) с помощью блока Hi-Res Обзор Блок AWeX предназначен для расширения возможностей таймера-счетчика, когда он работает в режимах генерации импульсов (WG). Блок AWeX позволяет легко и надежно реализовать расширенные функции управления электродвигателем (асинхронный, шаговый, коммутируемый реактивный (SR) и бесщеточный постоянного тока (BLDC)) или силовым преобразовательным каскадом.

Как показано на рисунке 15.1, при использовании любой из возможностей блока AWeX каждый выход генераторов импульсов таймера-счетчика 0 разделяется на два комплементарных сигнала. Данные пары сигналов поступают в блок генерации паузы неперекрытия (блок DTI), который генерирует неинвертированный сигнал нижнего уровня и инвертированный сигнал верхнего уровня, между импульсами которых вставлена пауза неперекрытия. Выходы DTI перекрывают нормальное состояние линий порта при условии соответствующей настройки перекрытия. Результирующий выходной сигнал при необходимости может быть проинвертирован в порте. Для этого необходимо установить бит инвертирования (INVEN) для соответствующей линии ввода-вывода (Pxn). Блок образцового генератора может использоваться для синхронизированной генерации сигнала по битовому шаблону (образцу). Дополнительно, выход генератора импульсов канала сравнения А может быть выведен на любую линию порта. После разрешения работы блока образцового генератора, активизируется обход блока DTI. Блок защиты от повреждения подключен к системе событий, которая предоставляет возможность любому событию запустить механизм защиты от повреждения, отключающий выходы AWeX. Перекрытие порта У всех таймеров-счетчиков предусмотрен блок логики перекрытия порта. На рисунке 15.2 функциональная схема этого блока. После установки бита разрешения паузы неперекрытия (DTIENx) блок расширения таймера-счетчика получает управление над парой выводов в соответствующем канале, а биты разрешения перекрытия выходов (OOE) получают управление над CCxEN. Обратите внимание, что таймер-счетчик 1 (TCx1) можно продолжать использовать, даже когда разрешена работа DTI в каналах A, B и D.

Рисунок 15.2. Расширения и логика перекрытия порта таймера-счетчика

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 319; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.007 с.) |