Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

CTRL - регистр управления PMIC-контроллеромСодержание книги

Поиск на нашем сайте

145. Бит 7 - RREN: разрешение динамической приоритезации Установка бита RREN приводит к разрешению динамической приоритезации низкоуровневых прерываний. Если данный бит равен нулю, используется статическая приоритезация, в соответствии с которой приоритет прерывания определяется по адресу вектора прерывания, причем чем меньше адрес, тем выше приоритет прерывания. 146. Бit 6 - IVSEL: настройка векторов прерываний По умолчанию, бит IVSEL равен нулю и векторы прерываний находятся в начале сектора прикладной программы flash-памяти. Если же в данный бит записать единицу, то векторы прерываний будут перенесены в начало загрузочного сектора Flash-памяти. Значения абсолютных адресов можно найти в документации на МК. Данный бит защищен механизмом защиты от изменения конфигурации (см. 3.12 "Защита от изменения конфигурации"). 147. Биты 5:3 - Res: резервные биты Данные биты не используются и зарезервированы для использования в будущем. Для совместимости с более новыми МК, выполняя запись в этот регистр, всегда записывайте нули в резервные биты. 148. Бит 2 - HILVLEN: разрешение прерываний высокого уровня Установка данного бита разрешает работу прерываний высокого уровня. Если же данный бит будет равен 0, то прерывания высокого уровня будут игнорироваться. 149. Бит 1 - MEDLVLEN: разрешение прерываний среднего уровня Установка данного бита разрешает работу прерываний среднего уровня. Если же данный бит будет равен 0, то прерывания среднего уровня будут игнорироваться. 150. Бит 0 - LOLVLEN: разрешение прерываний низкого уровня Установка данного бита разрешает работу прерываний низкого уровня. Если же данный бит будет равен 0, то прерывания низкого уровня будут игнорироваться. Обзор регистров

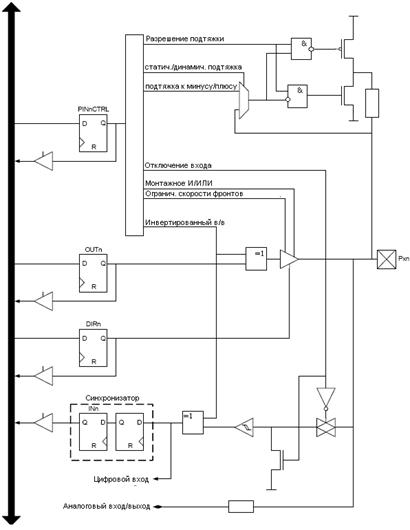

Порты ввода-вывода Отличительные особенности 151. Раздельная настройка функций входов и выходов на каждом выводе МК 152. Гибкая конфигурация выводов через специальный регистр конфигурации выводов 153. Синхронный и/или асинхронный контроль входов с возможностями генерации прерываний и событий 154. Возможность асинхронного возобновления работы МК 155. Гибкая конфигурация выходного драйвера и подтяжки логических уровней: 156. Двухтактный выход 157. Подтягивание к плюса или минусу питания 158. Выход "монтажное И" 159. Выход "монтажное ИЛИ" 160. Адаптивная подтяжка 161. Инвертированный ввод/вывод 162. Управление скоростью фронтов 163. Гибкое маскирование выводов 164. Возможность одновременной настройки нескольких выводов с одинаковыми конфигурационными параметрами 165. Поддержка операций типа "чтение-модификация-запись" 166. Регистры переключения/сброса/установки бит регистров OUT и DIR 167. Возможность вывода синхронизации на линии порта 168. Выход канала события 0 на 7-ой линии портов 169. Отображение регистров портов (виртуальные порты) с битно-адресуемом пространстве памяти ввода-вывода Обзор МК XMEGA содержат универсальные порты ввода-вывода общего назначения (ПВВ). Порт состоит из 8 линий с номерами 0…7. Каждая из этих линий может работать как вход или как выход, и поддерживает широкие возможности по настройке выходного драйвера и параметров подтяжки логических уровней. Порты также поддерживают такие дополнительные функции, как генерация прерываний, синхронный/асинхронный контроль входов и асинхронное возобновление активной работы МК. Все функции индивидуально настраиваются для каждой линии порта, однако некоторые из них имеют только одно предназначение. Все порты, при использовании их в качестве ПВВ общего назначения, полностью поддерживают операции типа "чтение-модификация-запись". Это означает, что изменение направления одной линии порта никак не повлияет на направление любой другой линии этого порта. Это же касается изменения конфигурации выходного драйвера, включения/отключения подтягивающих резисторов к плюсу или минусу питания на входах. Функциональная схема одной линии ввода-вывода показана на рисунке 13.1. На этом же рисунке можно найти названия регистров управления линиями в/в.

Рисунок 13.1. Функциональная схема линии ввода-вывода общего назначения

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-30; просмотров: 404; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.102 (0.124 с.) |