Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

СЧЕТЧИКИ Основные параметры и классификацияСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

СЧЕТЧИКИ Основные параметры и классификация Счетчиком называется функциональный узел ЭВМ, предназначенный для подсчета числа входных сигналов и хранения результата счета в двоичном коде. Счетчики выполняются на элементах памяти (триггерах), образующих двоичные разряды, и элементах комбинационной логики. Счетчики могут быть с естественным и произвольным порядком счета. При естественном порядке счета результат счета изменяется на единицу при поступлении на вход счетчика каждого сигнала (импульса). В счетчиках с произвольным порядком счета, называемых также пересчетными устройствами, при поступлении входных сигналов результат счета может изменяться произвольно в соответствии с заданным законом. Основными параметрами счетчиков являются модуль счета (коэффициент пересчета, емкость счетчика) Ксч и быстродействие. Модулем счета называют число состояний, которые он приобретает под действием входных сигналов. Если счетчик начал считать с начального состояния, то через каждые Кcч входных сигналов он снова возвращается в начальное состояние, а на его выходе появляется сигнал Ксч-ичного переноса. Быстродействие счетчика определяется разрешающей способностью и временем установки. Разрешающая способность t Р характеризуется периодом входных импульсов ТСЧ, при котором счетчик еще работает без сбоев, а время установки tУСТ — интервалом времени от момента поступления сигнала на вход счетчика до завершения перехода счетчика в новое состояние. По значению модуля счета счетчики делятся на двоичные (Ксч =2n, где n число разрядов), двоично-кодированные (имеют произвольный модуль счета, но все состояния кодируются двоичными кодами), счетчики с одинарным кодированием (состояние счетчика определяется местом расположения единственной единицы), счетчики с унитарным кодированием (состояние счетчика представлено числом единиц) и др. По направлению счета счетчики могут быть суммирующими (прямого счета), вычитающими (обратного счета) и реверсивными, т.е. способными работать как в режиме суммирования, так и в режиме вычитания. По структурной организации счетчики делятся на последовательные (асинхронные), параллельные (синхронные) и параллельно-последовательные. Помимо входа для приема подсчитываемых сигналов счетчик может иметь вход общего сброса R и входы данных Di для параллельной загрузки произвольного кода. В последнем случае для осуществления загрузки предусматривается еще один вход — вход разрешения параллельной загрузки PL (parallel 1оаd). Счетчики используются в ЭВМ для осуществления последовательного выполнения команд программы, подсчета числа циклов выполненных операций, образования адресов при обращении к запоминающим устройствам, в качестве делителей частоты в цифровых электронных часах и частотомерах и др. Последовательные счетчики В счетчиках, показанных на рис.12.1, используется непосредственная связь между выходами и входами триггеров. Поскольку каждый триггер (кроме первого) переключается выходным сигналом предыдущего, в таких счетчиках нет специальных схем формирования сигналов переноса или заема: их роль выполняют сигналы с выходов старшего разряда. Наращивание разрядности достигается путем последовательного подключения нужного количества триггеров. Однако несмотря на эти достоинства, а также простоту схемной реализации, область применения последовательных счетчиков с непосредственными связями ограничивается пределом их быстродействия. На рис. 12.2 приведены временные диаграммы трехразрядного суммирующего счетчика, выполненного по схеме рис. 12.1, а.

Параметр tТГ характеризует задержку переключения триггера при поступлении на его вход отрицательного перепада напряжения. Наличие этой задержки вызывает появление "ошибочных" результатов, не предусмотренных таблицей его функционирования (см. табл. 12.1). Так, например, после окончания действия второго входного импульса перед правильным состоянием Q2Q1Q0=010 на некоторое время возникает неправильное состояние Q2Q1Q0=000, соответствующее переходным процессам в триггерах нулевого и первого разрядов. Из-за переходных процессов при переключениях триггеров всех трех разрядов после окончания четвертого (а также восьмого) входного импульса установлению правильного состояния Q2Q1Q0=100 предшествуют два неправильных: 010 и 000. Следовательно индикацию результата счета в таком счетчике (а значит, и интервал между входными импульсами) следует осуществлять не ранее, чем через время t=3tТГ. При этом максимальная частота следования входных импульсов определяется формулой:

где tИ - длительность импульса.

С увеличением разрядности счетчика увеличивается время задержки переключения триггера n-го разряда относительно среза входных импульсов, поэтому для n-разрядного счетчика с последовательным переносом максимальная частота входных импульсов будет равна:

На диаграммах виден и режим деления частоты: каждый последующий триггер переключается вдвое реже, чем предыдущий. Поскольку предыдущий триггер выполняет роль генератора импульсов для последующего, то максимальная частота входных импульсов в режиме деления частоты ограничивается возможностями триггера младшего разряда и равна 1/tТГ. Задержки переключения триггеров последующих разрядов вызовут лишь появление фазовых сдвигов между входной и выходной последовательностями импульсов. Примером интегрального двоичного счетчика с непосредственными связями может служить микросхема К155ИЕ5 (рис. 12.3, а). Она представляет собой 4-разрядный двоичный счетчик, выполненный на двухступенчатых JK-триггерах с двумя счетными входами С1 и С2 и двумя входами сброса в нуль R1 и R2. Выход Q0 внутренне не соединен с последующими триггерами, что дает возможность использовать схему в качестве 3-разрядного или 4-разрядного двоичного счетчика. В первом случае счетные импульсы подают на вход С2, а во втором – на вход С1, предварительно объединив выход Q0 со входом C2. Входы сброса R1 и R2 обеспечивают сброс счетчика в нулевое состояние при R1=R2=1. При выполнении операции счета на одном из входов R1 или R2 (или на обоих) должен присутствовать потенциал низкого уровня.

Условное обозначение счетчика дано на рис. 12.3, б. Кольцевой счётчик В таком счётчике при поступлении тактовых импульсов С единственная 1 перемешается от разряда к разряду. Он выполнен на сдвиговом регистре, у которого сигнал обратной связи подается с прямого выхода триггера последнего разряда на входы первого (рис.13.17). Работа счётчика начинается с режима "Предустановка", в котором сигналом

Достоинством рассмотренного счётчика является простота его реализации, а недостатком – невозможность осушествления вывода информации в двоичном коде. Кроме того, в n-разрядном счётчике подобного типа из 2n возможных состояний 2n-n не используются и являются запрещенными. Если по какой-либо причине счётчик окажется в одном из этих состояний, то без постороннего вмешательства он не сможет перейти к выработке правильной последовательности.

Запрещенными состояниями счётчика являются такие, при которых в его разрядах число единиц оказывается более одной, либо во всех разрядах имеются нули. Для обнаружения запрещенных состояний счётчик снабжается дополнительной комбинационной схемой. Например, для трехразрядного кольцевого счётчика запрещенные состояния возникнут в случае, если единицы будут одновременно присутствовать на выходах первого и второго разрядов (Q0Q1=1), либо первого и третьего (Q0Q2=1), либо второго и третьего (Q1Q2=1), либо на выходах всех трех разрядов (Q0Q1Q2=1). Следовательно, сигнал обнаружения лишней 1 должен формироваться на основании булевого выражения

F1=Q0Q1+Q0Q2+Q1Q2+Q0Q1Q2=Q0Q1+Q0Q2+Q1Q2. (13.2) Для обнаружения нулевого состояния триггеров всех разрядов можно использовать функцию

Сигналы, сформированные на основании выражений (13.2) и (13.3), могут использоваться не только для обнаружения ошибки в работе счётчика, но и для его предустановки в исходное состояние.

Счётчик Джонсона Счётчик Джонсона отличается от рассмотренного кольцевого счётчика тем, что в нем сигнал обратной связи на входы триггера младшего разряда сдвигового регистра подается не с прямого, а с инверсного выхода триггера старшего разряда. Благодаря этому если в исходном состоянии триггеры всех разрядов регистра установлены в 0, то при поступлении импульсов синхронизации начнётся их постепенное переключение в 1. После того как все триггеры окажутся в единичном состоянии, начнется их поочередное (начиная с триггера младшего разряда) переключение в 0 и т.д. Следовательно, число рабочих состояний такого счётчика равно удвоенному числу его разрядов. Функционирование десятичного счётчика Джонсона осуществляется в соответствии с табл.13.4. Смена состояний такого счётчика происходит в соответствии с кодом Либау-Крейга. Для получения двоично-десятичного кода к выходам счётчика необходимо подключить комбинационную схему – преобразователь кодов.

Для десятичного счётчика Джонсона из 25=32 возможных состояний используется только 10, а остальные 22 состояния являются лишними. При попадании счётчика в эти состояния может быть нарушена его нормальная работа, определяемая табл.13.4. Поэтому необходимо предусмотреть дополнительные комбинационные схемы, определяющие сбои в работе счётчика и осуществляющие его установку в рабочее состояние. 14. Одновибраторы

14_2 Мультивибраторы

Дешифраторы Дешифратор или декодер (decoder) - это комбинационный операционный узел, преобразующий m-разрядный двоичный позиционный код в n=2m –разрядный унитарный код. Из всех n выходов дешифратора активный уровень появляется только на одном, номер которого определяется двоичным числом, установленном на адресных входах. Дешифраторы применяются в устройствах управления для дешифрации операций или микрокоманд в управляющие сигналы, в запоминающих устройствах для выбора ячейки памяти при записи или считывании информации, для преобразования двоично-десятичного кода в семисегментный, для реализации различных логических функций и др. Если при m входах дешифратор имеет n=2m выходов, то такой дешифратор называется полным. При 2m-1<n<2m дешифратор называется неполным, или частичным. Такой дешифратор использует лишь часть возможных наборов, имеет меньшее число выходов и внутренних схемных элементов. Условное обозначение дешифратора на 3 входа показано на рис. 14.1.

Входы дешифратора обычно называются адресными и нумеруются не порядковыми номерами, а в соответствии с весами двоичных разрядов, т.е. не 1,2,3,4,5..., а 1, 2, 4, 8,... Число входов и выходов дешифратора указывают таким бразом: 3-8 (читается «три в восемь»); 4-16, 4-10 (это неполный дешифратор). Функционирование полного дешифратора с m входами определяется табл. 14.1.

В соответствии с этой таблицей список функций, отрабатываемых каждым выходом дешифратора, будет иметь вид:

В зависимости от способа реализации уравнений (14.1) дешифраторы делятся на линейные (одноступенчатые) и матричные (многоступенчатые).

Линейные дешифраторы В линейных дешифраторах каждое уравнение системы (14.1) реализуется отдельным ЛЭ. В качестве примера рассмотрим линейный дешифратор 3-8, у которого функции выходов имеют вид:

Эти уравнения могут быть реализованы с помощью восьми трехвходовых элементов И, как показано на рис.14.2. У такого дешифратора активным уровнем является высокий уровень. Именно такой уровень будет на одном из выходов, определяемом значением числа

Достоинством линейного дешифратора является его высокое быстродействие, определяемое временем задержки tздр.р.ср. одного ЛЭ. Недостаток - увеличение числа входов каждого ЛЭ с ростом разрядности.

Работа стробируемых дешифраторов описывается логическими уравнениями, подобными уравнениям (14.1), но содержащими дополнительно сигнал разрешения Е: Для увеличения разрядности дешифраторов можно использовать их каскадное соединение. На рис. 14.4 показан дешифратор на 4 входа и 16 выходов, полученный каскадным соединением четырех стробируемых дешифраторов «2-4». Дешифрируемый двоичный код

В сериях ТТЛ и ТТЛШ дешифраторы обычно имеют инверсные выходы, поскольку их реализация осуществляется на элементах И-НЕ, являющихся наиболее технологичными в этих сериях. В КМДП-сериях, выполненных на инверторах, предпочтение имеют устройства, выполненные на элементах ИЛИ-НЕ, и дешифраторы чаще имеют прямые выходы.

Демультиплексоры Демультиплексором называют комбинационный узел ЭВМ, осуществляющий операцию передачи сигнала с одного информационного входа на один из m=2n выходов, номер которого определяется двоичным кодом на n адресных (управляющих) входах. Работа демультиплексора может быть задана либо таблицей истинности, либо логическими уравнениями:

в которых a1, a2,…, an – сигналы на адресных входах, а х – сигнал на информационном входе. Из сравнения уравнений (14.3) и (14.2) следует, что функцию демультиплексора может выполнять стробируемый дешифратор, если его вход разрешения использовать в качестве информационного. Поэтому как самостоятельные устройства демультиплексоры в интегральном исполнении не выпускаются, а все стробируемые дешифраторы, способные выполнять как функцию дешифрации двоичного кода, так и функцию демультиплексирования сигнала на тот или иной выход, обычно называют дешифраторами-демультиплексорами. На схемах в условном графическом обозначении (УГО) демультиплексор обозначается буквамиDMX в основном поле. В качестве демультиплексора можно использовать и нестробируемый дешифратор, приняв один из адресных входов за информационный (рис 14.6).

При этом на одной половине его выходов получается прямой входной сигнал x, а на второй - инверсный Помимо распределения входного сигнала по нескольким различным адресам демультиплексоры применяются для преобразования последовательного кода в параллельный. Мультиплексоры Мультиплексор - это комбинационный многовходовый функциональный узел с одним выходом. Входы мультиплексора подразделяются на информационные х1, х2,... хn и адресные, или управляющие а0, а1, а2,... ak-1. Обычно n= Сумматоры Сумматором называют операционный узел ЭВМ, выполняющий операцию сложения двух чисел, представленных в двоичном коде. Известно, что все многообразие математических операций (сложение, вычитание, деление, возведение в степень, вычисление тригонометрических функций и т.п.) можно получить с помощью операций сложения прямых и обратных кодов чисел, сдвинутых влево или вправо на то или иное число разрядов. Поэтому скорость выполнения вычислительных процессов в ЭВМ существенно зависит от быстродействия сумматоров. По принятой в ЭВМ системе счисления и кодирования сумматоры подразделяются на двоичные, десятичные, двоично-десятичные и др. По способу организации суммирования чисел сумматоры могут быть комбинационными и накапливающими. В комбинационных сумматорах результат суммирования не запоминается. В накапливающих сумматорах, имеющих память, после добавления к содержимому сумматора очередного слагаемого происходит запоминание полученного результата. По способу организации межразрядных переносов сумматоры делятся на параллельные, последовательные и c групповой структурой. В параллельных сумматорах суммирование одноименных разрядов чисел осуществляется одновременно (параллельно), а в последовательных — последовательно от младших к старшим. В сумматорах с групповой структурой суммируемые числа разбиваются на группы, построенные как параллельные сумматоры, а полученные в группах переносы складываются затем последовательно (параллельно-последовательные сумматоры) или параллельно. В последнем случае сумматоры называют параллельными с параллельно-параллельным переносом. По способу тактирования различают синхронные и асинхронные сумматоры. В синхронных сумматорах для выполнения процесса суммирования отводится постоянное время независимо от разрядности суммируемых чисел, а в асинхронных после завершения процесса суммирования вырабатывается специальный сигнал (признак). Поэтому у асинхронных сумматоров среднее время суммирования меньше, чем у синхронных.

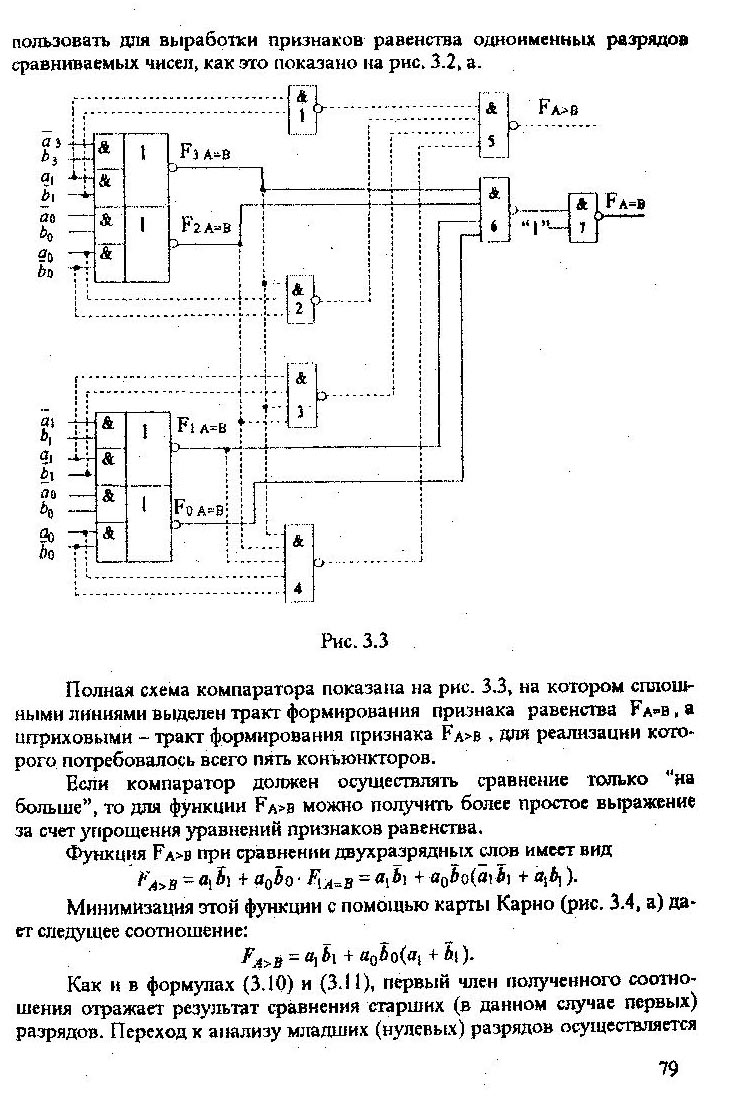

Схема сравнения на больше

Контроль по чётности

Запоминающие устройства (ЗУ) предназначены для хранения, записи и выдачи информации, необходимой для решения задач на ЭВМ. Записываемая, хранимая и считываемая информация представляется в виде слов или слогов в двоичном коде. Каждое слово (слог) располагается в ячейке памяти (ЯП), состоящей из элементов памяти (ЭП). Число ЭП в ЯП определяет разрядность ЯП и разрядность записываемого в неё слова. Конструктивно ЯП объединяются в устройство, называемое блоком памяти. В современных ЭВМ можно выделить устройства внутренней, внешней и буферной памяти. Устройства внутренней памяти непосредственно участвуют в процессе преобразования информации, обмениваясь данными с процессором ЭВМ и вычислительной системой. Внешняя память хранит большие массивы информации в течение длительного времени и обменивается данными с внутренней памятью. Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью. По функциональному назначению БИС ЗУ делят на постоянные (ПЗУ) и оперативные (ОЗУ). ПЗУ предназначены для хранения данных, однократно фиксируемых при изготовлении (неизменяемых программ, констант и т.п.). Основными требованиями, предъявляемыми к ПЗУ, являются неразрушающее считывание и энергонезависимость хранения информации. ОЗУ относятся к внутренней памяти, служат для хранения переменных данных и программ в процессе текущих вычислений. В обычных ОЗУ информация разрушается после отключения питания, хотя существуют БИС энергонезависимых ОЗУ. По технологии изготовления (типу элемента памяти) БИС ЗУ делятся на биполярные, использующие схемотехнику ТТЛ, ТТЛШ, ЭСЛ, И2Л, и униполярные на основе МДП - технологии, использующей структуры р-МДП, n-МДП, КМДП. Новейшими разработками являются ЗУ на основе арсенида галлия, у которых ЭП выполнены на основе полевых транзисторов с барьером Шотки. По способу хранения информации БИС ЗУ делятся на статические и динамические. В статических ЗУ применяются бистабильные триггерные элементы. Они управляются потенциальными сигналами и считывание информации происходит без ее разрушения. В динамических ЗУ для хранения информации используются запоминающие конденсаторы или междуэлектродные ёмкости транзисторов, в которых информация храниться в виде заряда. За счёт токов утечки заряд на конденсаторе с течением времени уменьшается, поэтому его необходимо периодически восстанавливать путём подзарядки. Этот процесс носит название регенерации. По способу размещения и поиска информации различают БИС ЗУ адресные и безадресные. В адресных ЗУ поиск информации производиться по номеру (адресу) ячеек памяти, в которых она размещается. Адресные ЗУ бывают с произвольным обращением (произвольной выборкой), когда допустим любой порядок выборки адресов, и с последовательным обращением (последовательной выборкой), когда выбор ЯП возможен только в порядке возрастания или убывания адресов. Среди безадресных ЗУ можно выделить ЗУ типа "очередь", стековые или магазинные и ассоциативные ЗУ. В ЗУ типа "очередь" считывание информации производится в том же порядке, в котором она была записана (FIFO - первый вошёл, первый вышел). В ЗУ типа стек (LIFO - последним зашёл, первым вышел) считывание информации производится в порядке, обратном тому, в котором она была записана. В ассоциативных ЗУ поиск информации осуществляется по значению признака поиска, харатеризующего информацию, т.е. по её содержанию.

Основные параметры ЗУ Основными классификационными параметрами ЗУ являются информационная ёмкость, тип логики и быстродействие. Ёмкость (М) ЗУ выражается в битах (байтах) и определяется как произведение количества имеющихся в ЗУ ячеек памяти (N) на их разрядность (n). При одинаковой ёмкости БИС ЗУ могут иметь различную организацию выборки. Например, при M=4096 ЗУ могут иметь следующие организации выборки: 4096x1 (4096 одноразрядных слов); 1024x4 (1024 четырёхразрядных слова); 512x8 (512 восьмиразрядных слов) и т.д. Под быстродействием ЗУ понимают время, затрачиваемое на одно обращение к памяти ЭВМ для записи или считывания информации. Обращение к памяти ЭВМ (время выборки tA) определяется временным интервалом от момента подачи на вход ЗУ заданного сигнала и получением на выходе данных при условии, что все остальные необходимые входные сигналы уже поданы. Время выборки можно определять относительно любого из необходимых для работы ЗУ сигналов. Система электрических параметров БИС ЗУ включает статические и динамические параметры. К статическим параметрам относятся входные и выходные токи и напряжения высокого и низкого уровней, выходной ток в третьем состоянии, токи потребления в режимах хранения, записи и считывания, напряжение питания. Динамические параметры характеризуют скорость реакции БИС на входные воздействия и устанавливают необходимые для правильного функционирования временные соотношения между входными и выходными сигналами, что в целом составляет временную диаграмму работы БИС ЗУ. Масочные ПЗУ Масочные ПЗУ строятся на основе диодов, биполярных и МДП-транзисторов.

Рис.16.9

В диодных ПЗУ диоды включаются в те пересечения ЗпМ, которые соответствуют записи 1, а в местах, где должен быть записан 0, они отсутствуют. Исключение диодов из соответствующих пересечений ЗпМ достигается тем, что на последнем этапе изготовления проводящая металлическая пленка, соединяющая катод диода с разрядной шиной, не изготавливается. Вид диодной ЗпМ показан на рис.16.9,а. Так как диодная матрица представляет собой элемент с гальваническими связями, то выходные сигналы имеют ту же форму и полярность, что и входные. Таким образом, если на ее входы (адресные шины) подаются напряжения постоянных уровней, то и на выходах (разрядных шинах) уровни будут также постоянными, что исключает необходимость применения дополнительных выходных регистров.

Программируемые ПЗУ Структура БИС ППЗУ подобна структуре БИС МПЗУ и отличается только видом ЭП. Элементами памяти ППЗУ являются диоды или многоэмиттерные транзисторы (МЭТ). Программирование ППЗУ осуществляется пережиганием перемычек (рис.16.11,а,г), либо электрическим пробоем р-n перехода (рис.16.11,6) или диодов Шотки (рис.16.11,в). В качестве плавких перемычек применяются тонкие пленки из нихрома или поликристаллического кремния. Ток пережигания составляет 50... 100 мА. При этом плотность тока в перемычке достигает 107 А/см2, что приводит к ее разрушению. Электрический пробой р-n перехода или диода Шотки осуществляется приложением к паре встречновключенных диодов повышенного напряжения (импульсного), являющегося для одного из них обратным.

Процесс программирования осуществляется с помощью специального устройства - программатора, и заключается в подаче электрических сигналов на соответствующие внешние выводы ППЗУ. Требуемые токи программирования обеспечиваются повышением приложенного к микросхеме ППЗУ напряжения до 12...20 В. Для рассеивания выделяемой при программировании мощности приходится увеличивать размеры ЭП, что приводит к снижению быстродействия из-за увеличения паразитных емкостей и уменьшению коэффициента интеграции. Коэффициент интеграции снижается также вследствие создания на кристалле БИС ППЗУ электронных схем формирования токов программирования, которые используются только один раз при программировании и в дальнейшей эксплуатации не требуются. На рис.16.12 показаны УГО электрически программируемого (прожигаемого) ПЗУ К155РЕЗ емкостью 256 бит с организацией 32x8, фрагмент (часть) схемы и временные диаграммы режима программирования. В выпускаемых заводом микросхемах все перемычки целые. При включении питания Uпl = 5 В (Un2 = 0 В) при заданном адресе А4... А0 и CS = 0 возбуждается один из выходов дешифратора, например первый, и коллекторный ток МЭТ через нижний эмиттер и резистор R2 втекает в базу транзистора VT2, вводя его в режим насыщения. На открытом коллекторном выходе VT2 образуется напряжение низкого уровня. Следовательно, неразрушенные перемычки соответствуют записи логического 0 во всех ЭП.

Затем на внешний резистор R=390 Ом подается напряжение Uп2 = 12,5 В (момент времени t2). При этом пробивается стабилитрон VD, открывается и входит в режим насыщения транзистор VT1. После этого на вход выбора кристалла подается сигнал C¯S = 0, вызывающий срабатывание дешифратора и появление напряжения высокого уровня на одном из его выходов, которое поступает на базу выбранного МЭТ (например МЭТ1). От источника Unl через МЭТ и насыщенный транзистор VT1 протекает большой ток, пережигающий перемычку. Выход из режима программирования осуществляется в обратной последовательности. В одном цикле допускается программирование только одного разряда. Репрограммируемые ПЗУ Структура БИС РПЗУ аналогична структуре МПЗУ, но в качестве ЭП используется МДП-структура, механизмом запоминания и хранения информации в которой является процесс накопления заряда. В зависимости от структуры МДП-транзистора различают два основных вида РПЗУ: РПЗУ, стираемые ультрафиолетовым облучением (РПЗУ УФ, EPROM), и электрически – стираемые РПЗУ (РПЗУ ЭС, EEPROM). Запись информации в обоих типах осуществляется электрическим способом. АЦП ПАРАЛЛЕЛЬНОГО ТИПА В таком АЦП весь диапазон входного напряжения разбивается на 2^n интервалов. Каждому интервалу соответствует опорное напряжение Uо(i), снимаемое с делителя напряжения, и свой аналоговый компаратор, сравнивающий Uвх с Uо(i).

Для любого входного напряжения в диапазоне (0.. ¦Uo¦)В найдется такой i-ый компаратор, входное напряжение на котором будет больше или равно опорному U(i). В этом случае на выходе этого компаратора напряжений и на выходах всех компараторов с номерами меньшими i появится "1", а на выходах остальных "0". Приоритетный шифратор сформирует двоичный код, равный наивысшему номеру входа на котором еще присутствует единица. Полученный код через управляемые инверторы/повторители, выполненные на элементах равнозначности, защелкивается в выходном регистре. Учитывая логику работы шифратора, заключающуюся в том, что если на его входах с 1-го по (n-1)-ый одни нули, то единица обязательно должна быть на нулевом входе, можно сэкономить на нулевом компараторе. В этом случае нулевой вход шифратора постоянно подключен к "1", и если входное напряжение находится в пределах 0 <= ¦Uвх¦ < ¦U(1)¦, то нулевой код на выходе генерируется автоматически. Элементы ИСКЛЮЧАЮЩЕЕ-ИЛИ-НЕ при значении Mi = 0 инвертируют выходной сигнал шифратора, а при Mi = 1 повторяют его. Зависимость выходного кода от режима дана ниже: M1 M0 Выходной код 1 1 прямой 0 0 обратный 0 1 дополнительный прямой 1 0 дополнительный обратный.Быстродействие достигается, как за счет паралл

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-14; просмотров: 3538; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.135.194.138 (0.021 с.) |

,

,

.

.

=0 первый триггер регистра устанавливается в 1, а остальные в 0. Затем при поступлении тактовых импульсов происходит сдвиг информации от разряда к разряду вправо, что и обеспечивает циркуляцию 1 в регистре. Счетная последовательность такого регистра приведена в табл. 13.3, из которой видно, что число рабочих состояний (модуль счета) такого счётчика равно числу его разрядов.

=0 первый триггер регистра устанавливается в 1, а остальные в 0. Затем при поступлении тактовых импульсов происходит сдвиг информации от разряда к разряду вправо, что и обеспечивает циркуляцию 1 в регистре. Счетная последовательность такого регистра приведена в табл. 13.3, из которой видно, что число рабочих состояний (модуль счета) такого счётчика равно числу его разрядов.

. (13.3)

. (13.3)

(14.1)

(14.1)

, в то время как на всех остальных выходах будут напряжения низкого уровня. Линейный дешифратор может быть реализован на ЛЭ ИЛИ-НЕ. Для этого следует преобразовать уравнения (14.1), воспользовавшись, например, правилами де Моргана. Для дешифратора 3-8 эти преобразования дадут:

, в то время как на всех остальных выходах будут напряжения низкого уровня. Линейный дешифратор может быть реализован на ЛЭ ИЛИ-НЕ. Для этого следует преобразовать уравнения (14.1), воспользовавшись, например, правилами де Моргана. Для дешифратора 3-8 эти преобразования дадут:

Дешифратор чаще всего подключается к выходным разрядам счетчика или регистра. При этом, как это видно из рис. 14.2, каждый разряд источника сигнала нагружается на n2=2m/2 входов ЛЭ дешифратора, что может существенно повлиять на помехоустойчивость. Поэтому входы дешифратора обычно делаются единичными с последующим размножением внутри микросхемы, как показано на рис. 14.3 для дешифратора 2-4. Значок ▷ внутри УГО означает, что используются инверторы с умощенным выходом. Если использовать не двухвходовые, а трехвходовые ЛЭ И, то третьи входы можно объединить и использовать в качестве входа разрешения. Такие дешифраторы называются стробируемыми. Выполненный таким образом стробирующий вход обладает тем достоинством, что не вносит дополнительной задержки в дешифратор, т.е. не влияет на его быстродействие. Недостаток - требуется увеличение числа входов ЛЭ на 1.

Дешифратор чаще всего подключается к выходным разрядам счетчика или регистра. При этом, как это видно из рис. 14.2, каждый разряд источника сигнала нагружается на n2=2m/2 входов ЛЭ дешифратора, что может существенно повлиять на помехоустойчивость. Поэтому входы дешифратора обычно делаются единичными с последующим размножением внутри микросхемы, как показано на рис. 14.3 для дешифратора 2-4. Значок ▷ внутри УГО означает, что используются инверторы с умощенным выходом. Если использовать не двухвходовые, а трехвходовые ЛЭ И, то третьи входы можно объединить и использовать в качестве входа разрешения. Такие дешифраторы называются стробируемыми. Выполненный таким образом стробирующий вход обладает тем достоинством, что не вносит дополнительной задержки в дешифратор, т.е. не влияет на его быстродействие. Недостаток - требуется увеличение числа входов ЛЭ на 1. возбуждает один из выходов дешифратора. Если А ≤ 3, то работает DC1 (у0 = 1, y1 = у2 = у3 = 0). При 3 ≤ А ≤ 7 работает DC2 (y1 = 1, у0 = у2 = у3 = 0). При 7 ≤ А ≤ 11 работает DC3 (у2 = 1, у0 = у1, = у3 = 0), а при А > 11 - дешифратор DC4 (y3 = 1, y0 = y1 = y2 = 0).

возбуждает один из выходов дешифратора. Если А ≤ 3, то работает DC1 (у0 = 1, y1 = у2 = у3 = 0). При 3 ≤ А ≤ 7 работает DC2 (y1 = 1, у0 = у2 = у3 = 0). При 7 ≤ А ≤ 11 работает DC3 (у2 = 1, у0 = у1, = у3 = 0), а при А > 11 - дешифратор DC4 (y3 = 1, y0 = y1 = y2 = 0). (14.2)

(14.2) (14.3)

(14.3)

.

. . Мультиплексор осуществляет функцию, обратную демультиплексору: на выход передается значение переменной того информационного входа, который определяется кодом на адресных входах.

. Мультиплексор осуществляет функцию, обратную демультиплексору: на выход передается значение переменной того информационного входа, который определяется кодом на адресных входах.

На рис.16.9,б показана ЗпМ, выполненная на биполярных многоэмиттерных транзисторах (МЭТ). При возбуждении одной из адресных шин на базе связанного с ней МЭТ возникает напряжение высокого уровня, в то время как на базах всех остальных транзисторов напряжение равно нулю. Информация логического 0 или логической 1 в любой разрядной шине зависит от того, есть ли связь разрядной шины с соответствующим эмиттером выбранного МЭТ или нет. Коллекторный ток выбранного МЭТ проходит только в те разрядные шины, которые связаны с эмиттерами этого транзистора, создавая положительные напряжения на этих разрядных шинах, в то время как на разрядных шинах, не связанных с его эмиттерами, напряжение равно нулю.

На рис.16.9,б показана ЗпМ, выполненная на биполярных многоэмиттерных транзисторах (МЭТ). При возбуждении одной из адресных шин на базе связанного с ней МЭТ возникает напряжение высокого уровня, в то время как на базах всех остальных транзисторов напряжение равно нулю. Информация логического 0 или логической 1 в любой разрядной шине зависит от того, есть ли связь разрядной шины с соответствующим эмиттером выбранного МЭТ или нет. Коллекторный ток выбранного МЭТ проходит только в те разрядные шины, которые связаны с эмиттерами этого транзистора, создавая положительные напряжения на этих разрядных шинах, в то время как на разрядных шинах, не связанных с его эмиттерами, напряжение равно нулю.

Режим программирования (запись в нужные ЭП логической 1) осуществляется следующим образом. На адресных входах микросхемы устанавливается требуемый адрес, после чего на шину Unl подается повышенное напряжение Uпl = 12,5 В (момент времени t1 на рис.16.12,в).

Режим программирования (запись в нужные ЭП логической 1) осуществляется следующим образом. На адресных входах микросхемы устанавливается требуемый адрес, после чего на шину Unl подается повышенное напряжение Uпl = 12,5 В (момент времени t1 на рис.16.12,в).