Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Полевые транзисторы (field effect transistors - FET)Содержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Существуют также полевые транзисторы с управляющим p-n переходом в затворе. Здесь применяется прием создания изоляции с помощью p-n перехода, смещенного обратным напряжением (повышающим потенциальный барьер). В этом случае диод p-n перехода включен в обратном направлении и не проводит ток.

Билет 5 Сигнальные процессоры и ПЛК См Билет 1 Цифровой сигнальный процессор (англ. Digital signal processor, DSP; сигнальный микропроцессор, СМП; процессор цифровых сигналов, ПЦС) — специализированныймикропроцессор, предназначенный для цифровой обработки сигналов (обычно в реальном масштабе времени). Особенности архитектуры: Архитектура сигнальных процессоров, по сравнению с микропроцессорами настольных компьютеров, имеет некоторые особенности: Гарвардская архитектура (разделение памяти команд и данных), как правило модифицированная; Большинство сигнальных процессоров имеют встроенную оперативную память, из которой может осуществляться выборка нескольких машинных слов одновременно. Нередко встроено сразу несколько видов оперативной памяти, например, в силу Гарвардской архитектуры бывает отдельная память для инструкций и отдельная — для данных. Некоторые сигнальные процессоры обладают одним или даже несколькими встроенными постоянными запоминающими устройствами с наиболее употребительными подпрограммами, таблицами и т. п. Аппаратное ускорение сложных вычислительных инструкций, то есть быстрое выполнение операций, характерных для цифровой обработки сигналов, например, операция «умножение с накоплением» (MAC) (Y:= X + A × B) обычно исполняется за один такт. «Бесплатные» по времени циклы с заранее известной длиной. Поддержка векторно-конвейерной обработки с помощью генераторов адресных последовательностей. Детерминированная работа с известными временами выполнения команд, что позволяет выполнять планирование работы в реальном времени. Сравнительно небольшая длина конвейера, так что незапланированные условные переходы могут занимать меньшее время, чем в универсальных процессорах. Экзотический набор регистров и инструкций, часто сложных для компиляторов. Некоторые архитектуры используют VLIW. По сравнению с микроконтроллерами, ограниченный набор периферийных устройств — впрочем, существуют «переходные» чипы, сочетающие в себе свойства DSP и широкую периферию микроконтроллеров. Программи́руемый логи́ческий контро́ллер (ПЛК) (англ. Programmable Logic Controller, PLC) или программируемый контроллер — электронная составляющая промышленного контроллера, специализированного (компьютеризированного) устройства, используемого дляавтоматизации технологических процессов. В качестве основного режима длительной работы ПЛК, зачастую в неблагоприятных условиях окружающей среды, выступает его автономное использование, без серьёзного обслуживания и практически без вмешательства человека. Иногда на ПЛК строятся системы числового программного управления станком (ЧПУ, англ. Computer numerical control, CNC). ПЛК являются устройствами реального времени. В системах управления технологическими объектами логические команды преобладают над числовыми операциями, что позволяет при сравнительной простоте микроконтроллера (шины шириной 8 или 16 бит), получить мощные системы действующие в режиме реального времени. В современных ПЛК числовые операции реализуются наравне с логическими. В то же время, в отличие от большинства процессоров компьютеров, в ПЛК обеспечивается доступ к отдельным битам памяти. Операционный усилитель

Операционный усилитель (ОУ, OpAmp) — усилитель постоянного тока с дифференциальным входом и, как правило, единственным выходом, имеющий высокий коэффициент усиления. ОУ почти всегда используются в схемах с глубокойотрицательной обратной связью, которая, благодаря высокому коэффициенту усиления ОУ, полностью определяет коэффициент передачи полученной схемы. В настоящее время ОУ получили широкое применение как в виде отдельных чипов, так и в виде функциональных блоков в составе более сложных интегральных схем. Такая популярность обусловлена тем, что ОУ является универсальным блоком с характеристиками, близкими к идеальным, на основе которого можно построить множество различных электронных узлов. Отрица́тельная обра́тная связь (ООС) — тип обратной связи, при которой выходной сигнал передается обратно на вход для погашения части входного сигнала, (то есть, изменяя входной сигнал таким образом, чтобы противодействовать изменению выходного сигнала). Говоря упрощённо, отрицательная обратная связь - это такое влияние выхода системы на вход ("обратное"), которое уменьшает действие входного сигнала на систему. Усилитель постоянного тока (УПТ) — электронный усилитель, рабочий диапазон частот которого включает нулевую частоту (постоянный ток). На верхнюю границу частотного диапазона усилителя никаких ограничений не накладывается, то есть она может находиться в области очень высоких частот. Таким образом, терминУПТ можно применять к любому усилителю, способному работать на постоянном токе. В подавляющем большинстве случаев УПТ является усилителем не тока, как следует из названия, а напряжения. Путаница обусловлена тем, что термин ток употребляется для описания электрических процессов вообще. В качестве усилителей постоянного тока в настоящее время используются операционные усилители (ОУ). Такой усилитель схематически изображен на рис.26, его название возникло еще во времена аналоговых вычислительных машин. В настоящее время микросхемы операционных усилителей – одни из самых распространенных аналоговых микросхем, существует много типов таких микросхем (хотя аналоговые вычислительные машины практически уже не используются). Справа на рис.26 показана схема рис.13 с применением операционного усилителя, в нем происходит усиление разницы между U1 и U2 ∙ Кос.

На рис.27 показана схема стабилизатора напряжения на Uвых = 5В с применением операционного усилителя К140УД1. Напряжение 220В из электросети переменного тока понижается трансформатором до примерно 12В, выпрямляется диодным мостом КЦ405В. На неинвертирующий вход ОУ 10 подается заданное значение, называемое опорным, которое получается с помощью делителя напряжения на стабилитроне КС147А и резисторе 150 ом. Стабилитрон представляет собой нелинейное сопротивление, которое обеспечивает постоянное падение напряжения при различных значениях тока через него. Текущее значение выходного напряжения подается на инвертирующий вход ОУ 9 через делитель на резисторах 150 ом и 2,4 Ком. Билет 6 1. Принцип действия КЭШа, многоуровневое кэширование, регистры процессора Кэш[1][2][3] или кеш[4][5][6] (англ. cache, от фр. cacher — «прятать»; произносится [kæʃ] — «кэш») — промежуточный буфер с быстрым доступом, содержащий информацию, которая может быть запрошена с наибольшей вероятностью. Доступ к данным в кэше идёт быстрее, чем выборка исходных данных из оперативной (ОЗУ) и быстрее внешней (жёсткий диск или твердотельный накопитель) памяти, за счёт чего уменьшается среднее время доступа и увеличивается общая производительность компьютерной системы. Функционирование

Кэш — это память с большей скоростью доступа, предназначенная для ускорения обращения к данным, содержащимся постоянно в памяти с меньшей скоростью доступа (далее «основная память»). Кэширование применяется ЦПУ, жёсткими дисками, браузерами, веб-серверами, службами DNS и WINS. Кэш состоит из набора записей. Каждая запись ассоциирована с элементом данных или блоком данных (небольшой части данных), которая является копией элемента данных в основной памяти. Каждая запись имеет идентификатор, определяющий соответствие между элементами данных в кэше и их копиями в основной памяти. Когда клиент кэша (ЦПУ, веб-браузер, операционная система) обращается к данным, прежде всего исследуется кэш. Если в кэше найдена запись с идентификатором, совпадающим с идентификатором затребованного элемента данных, то используются элементы данных в кэше. Такой случай называется попаданием кэша. Если в кэше не найдена запись, содержащая затребованный элемент данных, то он читается из основной памяти в кэш, и становится доступным для последующих обращений. Такой случай называется промахом кэша. Процент обращений к кэшу, когда в нём найден результат, называется уровнем попаданий или коэффициентом попаданий в кэш. Например, веб-браузер проверяет локальный кэш на диске на наличие локальной копии веб-страницы, соответствующей запрошенному URL. В этом примере URL — это идентификатор, а содержимое веб-страницы — это элементы данных. Если кэш ограничен в объёме, то при промахе может быть принято решение отбросить некоторую запись для освобождения пространства. Для выбора отбрасываемой записи используются разные алгоритмы вытеснения. При модификации элементов данных в кэше выполняется их обновление в основной памяти. Задержка во времени между модификацией данных в кэше и обновлением основной памяти управляется так называемой политикой записи. В кэше с немедленной записью каждое изменение вызывает синхронное обновление данных в основной памяти. В кэше с отложенной записью (или обратной записью) обновление происходит в случае вытеснения элемента данных, периодически или по запросу клиента. Для отслеживания модифицированных элементов данных записи кэша хранят признак модификации (изменённый или «грязный»). Промах в кэше с отложенной записью может потребовать два обращения к основной памяти: первое для записи заменяемых данных из кэша, второе для чтения необходимого элемента данных. В случае, если данные в основной памяти могут быть изменены независимо от кэша, то запись кэша может стать неактуальной. Протоколы взаимодействия между кэшами, которые сохраняют согласованность данных, называют протоколами когерентности кэша. Многоуровневое кэширование. Специфика конструирования современных процессорных ядер привела к тому, что систему кэширования в подавляющем большинстве CPU приходится делать многоуровневой. Кэш первого уровня (самый «близкий» к ядру) традиционно разделяется на две (как правило, равные) половины: кэш инструкций (L1I) и кэш данных (L1D). Это разделение предусматривается так называемой «гарвардской архитектурой» процессора, которая по состоянию на сегодня является самой популярной теоретической разработкой для построения современных CPU. В L1I, соответственно, аккумулируются только команды (с ним работает декодер, см. ниже), а в L1D — только данные (они впоследствии, как правило, попадают во внутренние регистры процессора). «Над L1» стоит кэш второго уровня — L2. Он, как правило, больше по объёму, и является уже «смешанным» — там располагаются и команды, и данные. L3 (кэш третьего уровня), как правило, полностью повторяет структуру L2, и в современных x86 CPU встречается редко. Чаще всего, L3 — это плод компромисса: за счёт использование более медленной и узкой шины, его можно сделать очень большим, но при этом скорость L3 всё равно остаётся более высокой, чем скорость памяти (хотя и не такой высокой, как у L2-кэша). Тем не менее, алгоритм работы с многоуровневым кэшем в общих чертах не отличается от алгоритма работы с одноуровневым, просто добавляются лишние итерации: сначала информация ищется в L1, если её там нет — в L2, потом — в L3, и уже потом, если ни на одном уровне кэша она не найдена — идёт обращение к основной памяти (ОЗУ). Уровни кэша. Кэш центрального процессора разделён на несколько уровней. В универсальном процессоре в настоящее время число уровней может достигать 3. Кэш-память уровня N+1 как правило больше по размеру и медленнее по скорости доступа и передаче данных, чем кэш-память уровня N. Самой быстрой памятью является кэш первого уровня — L1-cache. По сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков. В современных процессорах обычно кэш L1 разделен на два кэша, кэш команд (инструкций) и кэш данных (Гарвардская архитектура). Большинство процессоров без L1 кэша не могут функционировать. L1 кэш работает на частоте процессора, и, в общем случае, обращение к нему может производиться каждый такт. Зачастую является возможным выполнять несколько операций чтения/записи одновременно. Латентность доступа обычно равна 2−4 тактам ядра. Объём обычно невелик — не более 384 Кбайт. Вторым по быстродействию является L2-cache — кэш второго уровня, обычно он расположен на кристалле, как и L1. В старых процессорах — набор микросхем на системной плате. Объём L2 кэша от 128 Кбайт до 1−12 Мбайт. В современных многоядерных процессорах кэш второго уровня, находясь на том же кристалле, является памятью раздельного пользования — при общем объёме кэша в nM Мбайт на каждое ядро приходится по nM/nC Мбайта, где nC количество ядер процессора. Обычно латентность L2 кэша, расположенного на кристалле ядра, составляет от 8 до 20 тактов ядра. Кэш третьего уровня наименее быстродействующий, но он может быть очень внушительного размера — более 24 Мбайт. L3 кэш медленнее предыдущих кэшей, но всё равно значительно быстрее, чем оперативная память. В многопроцессорных системах находится в общем пользовании и предназначен для синхронизации данных различных L2. Иногда существует и 4 уровень кэша, обыкновенно он расположен в отдельной микросхеме. Применение кэша 4 уровня оправдано только для высоко производительных серверов имейнфреймов. Проблема синхронизации между различными кэшами (как одного, так и множества процессоров) решается когерентностью кэша. Существует три варианта обмена информацией между кэш-памятью различных уровней, или, как говорят, кэш-архитектуры: инклюзивная, эксклюзивная и неэксклюзивная. Инклюзивная архитектура предполагает дублирование информации кэша верхнего уровня в нижнем (предпочитает фирма Intel). Эксклюзивная кэш-память предполагает уникальность информации, находящейся в различных уровнях кэша (предпочитает фирма AMD). В неэксклюзивной кэши могут вести себя как угодно. Регистр процессора — блок ячеек памяти, образующий сверхбыструю оперативную память (СОЗУ) внутри процессора; используется самим процессором и большой частью недоступен программисту: например, при выборке из памяти очередной команды она помещается в регистр команд (англ.), к которому программист обратиться не может. Имеются также регистры, которые в принципе программно доступны, но обращение к ним осуществляется из программ операционной системы, например, управляющие регистры и теневые регистры дескрипторов сегментов. Этими регистрами пользуются в основном разработчики операционных систем. Существуют также так называемые регистры общего назначения (РОН), представляющие собой часть регистров процессора, использующихся без ограничения в арифметических операциях, но имеющие определенные ограничения, например в строковых. РОН, не характерные для эпохи мейнфреймов типа IBM/370[1] стали популярными в микропроцессорах архитектуры X86 — i8085, i8086 и последующих[2]. Специальные регистры[3] содержат данные, необходимые для работы процессора — смещения базовых таблиц, уровни доступа и т. д. Часть специальных регистров принадлежит устройству управления, которое управляет процессором путём генерации последовательности микрокоманд. Доступ к значениям, хранящимся в регистрах, как правило, в несколько раз быстрее, чем доступ к ячейкам оперативной памяти (даже если кеш-память содержит нужные данные), но объём оперативной памяти намного превосходит суммарный объём регистров (объём среднего модуля оперативной памяти сегодня составляет 1-4 Гб[4], суммарная «ёмкость» регистров общего назначения/данных для процессора Intel 80386 и более новых 32 битов * 8 = 256 бит). Регистром называется функциональный узел, осуществляющий приём, хранение и передачу информации. Регистры состоят из группы триггеров, обычно D. По типу приёма и выдачи информации различают 2 типа регистров:

|

||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 771; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.41 (0.012 с.) |

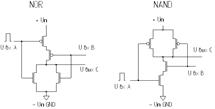

На рис. 23 слева показан схематично разрез такого транзистора наиболее распространенного в цифровых схемах (в том числе в компьютерах) типа – “металл-окисел-полупроводник” (МОП) или Metal-Oxide-Semiconductor (MOS). Правее показано его условное графическое обозначение. На подложке р-типа создается очень близко (на расстоянии десятков нанометров) две n-области, названные “истоком и стоком (sourse, drain)” с электронной проводимостью. К этим областям подведены металлические проводники (густая штриховка). Область между истоком и стоком покрыта тонким слоем изолятора, обычно окисью кремния (редкая штриховка), поверх которого нанесен проводящий затвор (gate). Если между затвором и подложкой постепенно увеличивать положительное напряжение, как показано на рис.23 слева внизу, то сначала из под затвора в подложке уйдут дырки. Но при дальнейшем росте положительного напряжения выше некоторого порогового значения из n-областей в подложку начнут поступать электроны, образовывая проводящий n-канал под затвором. Толщина этого канала, а, значит, и сопротивление между истоком и стоком зависит от величины положительного напряжения на затворе. В цифровых схемах транзисторы работают в ключевом режиме: либо это сопротивление очень мало (ключ замкнут), либо очень велико (ключ разомкнут). Рассмотренный транзистор имеет n-канал. В нем между стоком и истоком включается напряжение питания плюсом к стоку и минусом к истоку, как показано на его условном обозначении в центре вверху рис.23. Ниже этого показан схематически ключ, размыкающийся при понижении напряжения на затворе ниже порога и замыкающийся при повышении этого напряжения. Существуют также транзисторы с р-каналом, в которых использована подложка с n-проводимостью, а канал под затвором между двумя р-областями образуется при отрицательном напряжении на затворе, создавая замкнутый ключ. В цифровых интегральных схемах транзисторы с n-каналом и р-каналом соединяются последовательно, образуя дополняющие (комплементарные - complementary) пары, как показано в центре на рис.23. Сверху включен МОП-транзистор с р-каналом (он имеет на затворе маленький кружок – символ инверсии). При повышении входного напряжения Uвх нижний ключ замыкается (транзистор открывается), а верхний ключ размыкается (транзистор запирается). Наоборот, при понижении U вх нижний ключ размыкается, а верхний замыкается. В установившемся состоянии комплементарная пара не потребляет от источника питания Uп почти никакого тока, не создавая нагревания и не нагружая источник питания. Это очень важно для многих современных интегральных схем, содержащих миллионы транзисторов, как например, процессоры. Ток потребляется только при переключении для зарядки электрических емкостей проводников в изоляции, например затвор и подложка, разделенные слоем изолятора образуют конденсатор С (показан в центре рис.23). Рассмотренный полевой транзистор относится к транзисторам с изолированным затвором и индуцированным каналом. Выпускаются также полевые транзисторы со встроенным каналом. Во многом их поведение аналогично ранее сказанному, поэтому для простоты мы их не выделяем. На рис. 24 показаны логические ячейки на комплементарных МОП-транзисторах с двумя входами, они выполняют логические функции ИЛИ-НЕ (NOR) и И-НЕ (NAND). Логическая единица у них высокая, то есть “0”-низко (земля, ground - GRD), “1”-высоко, сигнал в виде положительного импульса показан на входе А. Если положить, что на обоих входах А и В низко у ячейки NOR (левой), то оба нижних МОП-транзистора с n-каналом закрыты, а верхние два последовательно соединенных транзистора с р-каналом открыты, поэтому на выходе С высоко (логичекая “1”). Если на вход А ячейки NOR подать высоко (логическая “1”), то левый нижний транзистор откроется, а самый верхний транзистор соответственно закроется и на выходе станет низко (логический “0”), То же самое будет, если подать “1” на вход В или сразу на оба входа А и В. Аналогично можно проанализировать правую ячейку NAND, результаты такого анализа показаны в таблице истинности 2. Таблица 2 Таблица истинности ячеек NOR и NAND.

На рис. 23 слева показан схематично разрез такого транзистора наиболее распространенного в цифровых схемах (в том числе в компьютерах) типа – “металл-окисел-полупроводник” (МОП) или Metal-Oxide-Semiconductor (MOS). Правее показано его условное графическое обозначение. На подложке р-типа создается очень близко (на расстоянии десятков нанометров) две n-области, названные “истоком и стоком (sourse, drain)” с электронной проводимостью. К этим областям подведены металлические проводники (густая штриховка). Область между истоком и стоком покрыта тонким слоем изолятора, обычно окисью кремния (редкая штриховка), поверх которого нанесен проводящий затвор (gate). Если между затвором и подложкой постепенно увеличивать положительное напряжение, как показано на рис.23 слева внизу, то сначала из под затвора в подложке уйдут дырки. Но при дальнейшем росте положительного напряжения выше некоторого порогового значения из n-областей в подложку начнут поступать электроны, образовывая проводящий n-канал под затвором. Толщина этого канала, а, значит, и сопротивление между истоком и стоком зависит от величины положительного напряжения на затворе. В цифровых схемах транзисторы работают в ключевом режиме: либо это сопротивление очень мало (ключ замкнут), либо очень велико (ключ разомкнут). Рассмотренный транзистор имеет n-канал. В нем между стоком и истоком включается напряжение питания плюсом к стоку и минусом к истоку, как показано на его условном обозначении в центре вверху рис.23. Ниже этого показан схематически ключ, размыкающийся при понижении напряжения на затворе ниже порога и замыкающийся при повышении этого напряжения. Существуют также транзисторы с р-каналом, в которых использована подложка с n-проводимостью, а канал под затвором между двумя р-областями образуется при отрицательном напряжении на затворе, создавая замкнутый ключ. В цифровых интегральных схемах транзисторы с n-каналом и р-каналом соединяются последовательно, образуя дополняющие (комплементарные - complementary) пары, как показано в центре на рис.23. Сверху включен МОП-транзистор с р-каналом (он имеет на затворе маленький кружок – символ инверсии). При повышении входного напряжения Uвх нижний ключ замыкается (транзистор открывается), а верхний ключ размыкается (транзистор запирается). Наоборот, при понижении U вх нижний ключ размыкается, а верхний замыкается. В установившемся состоянии комплементарная пара не потребляет от источника питания Uп почти никакого тока, не создавая нагревания и не нагружая источник питания. Это очень важно для многих современных интегральных схем, содержащих миллионы транзисторов, как например, процессоры. Ток потребляется только при переключении для зарядки электрических емкостей проводников в изоляции, например затвор и подложка, разделенные слоем изолятора образуют конденсатор С (показан в центре рис.23). Рассмотренный полевой транзистор относится к транзисторам с изолированным затвором и индуцированным каналом. Выпускаются также полевые транзисторы со встроенным каналом. Во многом их поведение аналогично ранее сказанному, поэтому для простоты мы их не выделяем. На рис. 24 показаны логические ячейки на комплементарных МОП-транзисторах с двумя входами, они выполняют логические функции ИЛИ-НЕ (NOR) и И-НЕ (NAND). Логическая единица у них высокая, то есть “0”-низко (земля, ground - GRD), “1”-высоко, сигнал в виде положительного импульса показан на входе А. Если положить, что на обоих входах А и В низко у ячейки NOR (левой), то оба нижних МОП-транзистора с n-каналом закрыты, а верхние два последовательно соединенных транзистора с р-каналом открыты, поэтому на выходе С высоко (логичекая “1”). Если на вход А ячейки NOR подать высоко (логическая “1”), то левый нижний транзистор откроется, а самый верхний транзистор соответственно закроется и на выходе станет низко (логический “0”), То же самое будет, если подать “1” на вход В или сразу на оба входа А и В. Аналогично можно проанализировать правую ячейку NAND, результаты такого анализа показаны в таблице истинности 2. Таблица 2 Таблица истинности ячеек NOR и NAND. Рисунок 24. Логические ячейки NOR и NAND на МДП-транзисторах.

Рисунок 24. Логические ячейки NOR и NAND на МДП-транзисторах. Схематический разрез такого транзистора показан на рис. 25 слева, для случая n-канала. Повышение напряжения на затворе вследствие высокого обратного сопротивления p-n перехода затвора практически не создает тока затвора. Оно отталкивает дырки в подложке между истоком и стоком, но привлекает электроны, создающие токопроводящий канал. Такой полевой транзистор аналогичен электронно-вакуумному триоду (рис.7) и схема его включения также аналогична, она приведена в центре рис.25. Справа на рис. 25 показан полевой транзистор с р-каналом, в нем полярности питания и смещения меняются на противоположные. Полевые транзисторы создают значительно меньший шум, чем биполярные, поэтому их применяют в первых (входных) каскадах усилителей, где сигнал мал, например, на выходе микрофона. Усилительные свойства полевых транзисторов задаются параметром “крутизна характеристики” мА/В – изменение тока исток-сток в миллиамперах на изменение напряжения исток-затвор в вольтах (это аналогично электронным лампам), например 8 ма/в для полевых транзисторов типа 2П 305. Полевые транзисторы всех типов имеют высокое входное сопротивление, значительно большее, чем биполярные транзисторы. По этой причине входные токи у них очень малы, что не нагружает источники сигнала. Это свойство позволяет работать с малыми токами и соответственно с малым потреблением энергии, что снижает нагревание и потребление энергии от источников питания. В больших интегральных цифровых схемах, таких как процессоры, это особенно ценно. Кроме того для цифровых схем создается дополнительная свобода проектирования, так как выход одного элемента можно подключать на входы многих других элементов (разветвление сигнала – fan out). Необходимо отметить, что кружок в условном графическом обозначении транзистора изображает оболочку (защитный корпус), как на рис. 12 и 25. В интегральных схемах имеется общая оболочка для многих транзисторов, поэтому для отдельных транзисторов кружки не ставятся, как, например, на рис. 24.

Схематический разрез такого транзистора показан на рис. 25 слева, для случая n-канала. Повышение напряжения на затворе вследствие высокого обратного сопротивления p-n перехода затвора практически не создает тока затвора. Оно отталкивает дырки в подложке между истоком и стоком, но привлекает электроны, создающие токопроводящий канал. Такой полевой транзистор аналогичен электронно-вакуумному триоду (рис.7) и схема его включения также аналогична, она приведена в центре рис.25. Справа на рис. 25 показан полевой транзистор с р-каналом, в нем полярности питания и смещения меняются на противоположные. Полевые транзисторы создают значительно меньший шум, чем биполярные, поэтому их применяют в первых (входных) каскадах усилителей, где сигнал мал, например, на выходе микрофона. Усилительные свойства полевых транзисторов задаются параметром “крутизна характеристики” мА/В – изменение тока исток-сток в миллиамперах на изменение напряжения исток-затвор в вольтах (это аналогично электронным лампам), например 8 ма/в для полевых транзисторов типа 2П 305. Полевые транзисторы всех типов имеют высокое входное сопротивление, значительно большее, чем биполярные транзисторы. По этой причине входные токи у них очень малы, что не нагружает источники сигнала. Это свойство позволяет работать с малыми токами и соответственно с малым потреблением энергии, что снижает нагревание и потребление энергии от источников питания. В больших интегральных цифровых схемах, таких как процессоры, это особенно ценно. Кроме того для цифровых схем создается дополнительная свобода проектирования, так как выход одного элемента можно подключать на входы многих других элементов (разветвление сигнала – fan out). Необходимо отметить, что кружок в условном графическом обозначении транзистора изображает оболочку (защитный корпус), как на рис. 12 и 25. В интегральных схемах имеется общая оболочка для многих транзисторов, поэтому для отдельных транзисторов кружки не ставятся, как, например, на рис. 24.

Рисунок 26. Схема операционного усилителя

Рисунок 26. Схема операционного усилителя Усиленная разница входных напряжений усилителя с его выхода 5 поступает на базу мощного регулирующего транзистора КТ 807Б, он аналогичен переменному резистору R2 на рис.6 (он может рассматриваться как исполнительный элемент). Его функцией можно считать срезание лишнего напряжения, поступающего на коллектор, до значения 5В. На КТ 807Б теряется энергия, соизмеримая с полезной энергией на нагрузке Rнагр. По этой причине к.п.д. данного стабилизатора напряжения примерно 50%, а транзистор КТ 807Б сильно греется, его нужно специально охлаждать, например, с помощью радиатора. Рассмотренный стабилизатор применяется при небольших мощностях нагрузки (до 10 Вт).

Усиленная разница входных напряжений усилителя с его выхода 5 поступает на базу мощного регулирующего транзистора КТ 807Б, он аналогичен переменному резистору R2 на рис.6 (он может рассматриваться как исполнительный элемент). Его функцией можно считать срезание лишнего напряжения, поступающего на коллектор, до значения 5В. На КТ 807Б теряется энергия, соизмеримая с полезной энергией на нагрузке Rнагр. По этой причине к.п.д. данного стабилизатора напряжения примерно 50%, а транзистор КТ 807Б сильно греется, его нужно специально охлаждать, например, с помощью радиатора. Рассмотренный стабилизатор применяется при небольших мощностях нагрузки (до 10 Вт). Диаграмма кэша памяти ЦПУ

Диаграмма кэша памяти ЦПУ