Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Искрение под щетками создает электромагнитные помехи и также ускоряет износ,Содержание книги

Поиск на нашем сайте

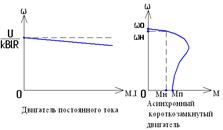

3. в процессе эксплуатации приходится чистить коллектор от частиц материала щеток (например, промывать ваткой, смоченной в бензине), а также заменять изношенные щетки. Тем не менее, эта старейшая электромашина пока еще широко применяется и работает также на переменном токе, например в электроинструменте (дрели, дисковые пилы и т.д.). К ее достоинствам относится возможность достаточно просто изменять частоту вращения вала ω в зависимости от подаваемого напряжения U или индукции в зазоре B, которую можно изменять, изменяя ток возбуждения электромагнитов статора. Это вытекает из (1), из (2) следует, что можно изменять момент на валу М с помощью изменения тока I или индукции B. Это позволяет успешно их применять там, где нужен плавный запуск и регулирование частоты вращения (например, транспорт: трамвай, метро, лифт), где нужна большая частота вращения (электроинструмент: дрели, дисковые пилы и т.д.). Поскольку инструмент с такими двигателями очень распространен и работает на переменном токе, то название “двигатель постоянного тока” вызывает немало вопросов. В английской терминологии такой двигатель имеет название “brush motor – щеточный двигатель”, соответственно в русской терминологии имеется еще название “коллекторный двигатель”. При сравнении свойств двигателей очень важной является «механическая характеристика» ω(М) - зависимость частоты вращения от момента на валу, создаваемого нагрузкой при постоянном напряжении на входе U, рис. 48. В идеальном случае, выражение (1), ω не зависит от М и определяется только напряжением на входе U=Е (противо э.д.с.). Однако в реальном случае по мере роста момента М будет расти ток I по (2), что приведет к росту потерь напряжения на сопротивлении r (7) и соответственно падению Е и падению ω из (1). Рисунок 48. Механическая характеристика электродвигателей

Билет 8 1. Предвыборка данных, принцип повышения скорости передачи информации для памяти DDR2, DDR3

В любой более-менее сложной программе присутствуют команды условного перехода: «Если некое условие истинно — перейти к исполнению одного участка кода, если нет — другого». До тех пор, пока не станет известно, какой участок кода после условного перехода окажется «актуальным» — его невозможно начать декодировать и исполнять (см. внеочередное исполнение). Для того чтобы как-то примирить концепцию внеочередного исполнения с командами условного перехода, предназначается специальный блок: блок предсказания ветвлений. Он пытается предсказать, на какой участок кода укажет команда условного перехода, ещё до того, как она будет исполнена. Процессором производятся вполне реальные действия: предсказанный участок кода загружается в кэш (если он там отсутствует), и даже начинается декодирование и выполнение его команд. Причём среди выполняемых команд также могут содержаться инструкции условного перехода, и их результаты тоже предсказываются, что порождает целую цепочку из пока не проверенных предсказаний! Разумеется, если блок предсказания ветвлений ошибся, вся проделанная в соответствии с его предсказаниями работа просто аннулируется. Алгоритмы, по которым работает блок предсказания ветвлений, преимущественно просты. Чаще всего команда условного перехода встречается в циклах: некий счётчик принимает значение X, и после каждого прохождения цикла значение счётчика уменьшается на единицу. Соответственно, до тех пор, пока значение счётчика больше нуля — осуществляется переход на начало цикла, а после того, как он становится равным нулю — исполнение продолжается дальше. Блок предсказания ветвлений просто анализирует результат выполнения команды условного перехода, и считает, что если N раз подряд результатом стал переход на определённый адрес — то и в N+1 случае будет осуществлён переход туда же. Однако, несмотря на весь примитивизм, данная схема работает просто замечательно: например, в случае, если счётчик принимает значение 100, а «порог срабатывания» предсказателя ветвлений (N) равен двум переходам подряд на один и тот же адрес — легко заметить, что 97 переходов из 98 будут предсказаны правильно! Разумеется, несмотря на достаточно высокую эффективность простых алгоритмов, механизмы предсказания ветвлений в современных CPU всё равно постоянно совершенствуются и усложняются — но тут уже речь идёт о борьбе за единицы процентов: например, за то, чтобы повысить эффективность работы блока предсказания ветвлений с 95 процентов до 97, или даже с 97% до 99...

Блок предвыборки данных (Prefetch) очень похож по принципу своего действия на блок предсказания ветвлений — с той только разницей, что в данном случае речь идёт не о коде, а о данных. Общий принцип действия такой же: если встроенная схема анализа доступа к данным в ОЗУ решает, что к некоему участку памяти, ещё не загруженному в кэш, скоро будет осуществлён доступ — она даёт команду на загрузку данного участка памяти в кэш ещё до того, как он понадобится исполняемой программе. Результативно работающий блок предвыборки позволяет существенно сократить время доступа к нужным данным, и, соответственно, повысить скорость исполнения программы. К слову: грамотный Prefetch очень хорошо компенсирует высокую латентность подсистемы памяти, подгружая нужные данные в кэш, и тем самым, нивелируя задержки при доступе к ним, если бы они находились не в кэше, а в основном ОЗУ. Однако, разумеется, в случае ошибки блока предвыборки данных, неизбежны негативные последствия: загружая де-факто «ненужные» данные в кэш, Prefetch вытесняет из него другие (быть может, как раз нужные). Кроме того, за счёт «предвосхищения» операции считывания, создаётся дополнительная нагрузка на контроллер памяти (де-факто, в случае ошибки — совершенно бесполезная). Алгоритмы Prefetch, как и алгоритмы блока предсказания ветвлений, тоже не блещут интеллектуальностью: как правило, данный блок стремится отследить, не считывается ли информация из памяти с определённым «шагом» (по адресам), и на основании этого анализа пытается предсказать, с какого адреса будут считываться данные в процессе дальнейшей работы программы. Впрочем, как и в случае с блоком предсказания ветвлений, простота алгоритма вовсе не означает низкую эффективность: в среднем, блок предвыборки данных чаще «попадает», чем ошибается (и это, как и в предыдущем случае, прежде всего связано с тем, что «массированное» чтение данных из памяти, как правило происходит в процессе исполнения различных циклов). SDRAM (англ. Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом) — тип запоминающего устройства, использующегося в компьютере в качестве ОЗУ. В отличие от других типов DRAM, использовавших асинхронный обмен данными, ответ на поступивший в устройство управляющий сигнал возвращается не сразу, а лишь при получении следующего тактового сигнала. Тактовые сигналы позволяют организовать работу SDRAM в виде конечного автомата, исполняющего входящие команды. При этом входящие команды могут поступать в виде непрерывного потока, не дожидаясь, пока будет завершено выполнение предыдущих инструкций (конвейерная обработка): сразу после команды записи может поступить следующая команда, не ожидая, когда данные окажутся записаны. Поступление команды чтения приведёт к тому, что на выходе данные появятся спустя некоторое количество тактов — это время называется задержкой (англ. SDRAM latency) и является одной из важных характеристик данного типа устройств. DDR SDRAM (от англ. Double Data Rate Synchronous Dynamic Random Access Memory — синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных) — тип компьютерной памяти, используемой в вычислительной технике в качестве оперативной и видеопамяти. Пришла на смену памяти типа SDRAM. При использовании DDR SDRAM достигается удвоенная скорость работы, нежели в SDRAM, за счёт считывания команд и данных не только по фронту, как в SDRAM, но и по спаду тактового сигнала. За счёт этого удваивается скорость передачи данных без увеличения частоты тактового сигнала шины памяти. Таким образом, при работе DDR на частоте 100 МГц мы получим эффективную частоту 200 МГц (при сравнении с аналогом SDR SDRAM). В спецификации JEDEC есть замечание, что использовать термин «МГц» в DDR некорректно, правильно указывать скорость «миллионов передач в секунду через один вывод данных». Специфическим режимом работы модулей памяти является двухканальный режим. Описание Микросхемы памяти DDR SDRAM выпускаются в корпусах TSOP и (освоено позднее) корпусах типа BGA (FBGA), производятся по нормам 0,13 и 0,09-микронного техпроцесса: Напряжение питания микросхем: 2,6 В +/- 0,1 В

|

||||

|

Последнее изменение этой страницы: 2016-08-15; просмотров: 296; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.16.130.96 (0.008 с.) |