Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Лабораторная работа №2. СчетчикиСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Цель работы: изучить временные диаграммы работы счетчиков, построенных по различным схемам. Порядок выполнения работы 1 Изучите до начала выполнения лабораторной работы методики синтеза счетчиков. 2 Соберите схему проверки стандартного счетчика, тип которого в зависимости от установленного варианта задания приведен в таблице 8.3. Таблица 8.3 – Варианты заданий

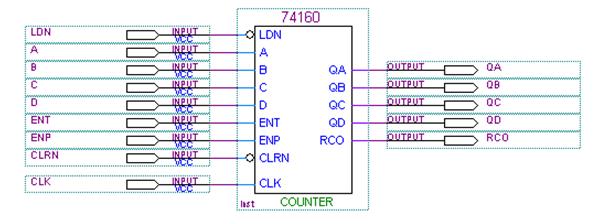

3 Создайте схему для исследования заданного счетчика в САПР На рисунке 8.5 в качестве примера приведена схема для исследования счетчика 74160.

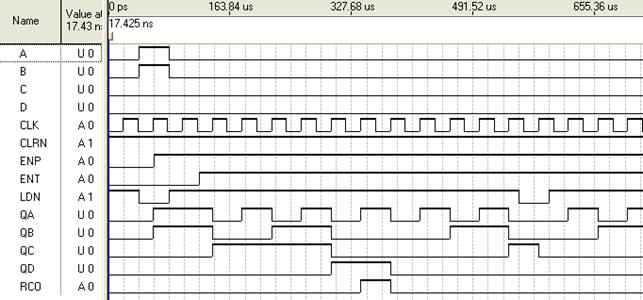

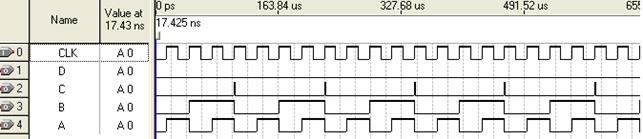

Рисунок 8.5 – Схема исследования счетчика 74160 4 Исследуйте временные диаграммы работы счетчика при произвольных фазовых соотношениях входных сигналов. На рисунке 8.6 в качестве примера приведены временные диаграммы работы построенного счетчика.

Рисунок 8.6 – Временные диаграммы работы счетчика, построенного на базовой микросхеме 74160 5 Исследуйте и приведите в отчете назначение всех входов и выходов базовой микросхемы счетчика. 6 Синтезируйте схему четырехразрядного счетчика с учетом требований, приведенных в таблице 8.4. Таблица 8.4 – Варианты заданий

Продолжение таблицы 8.4

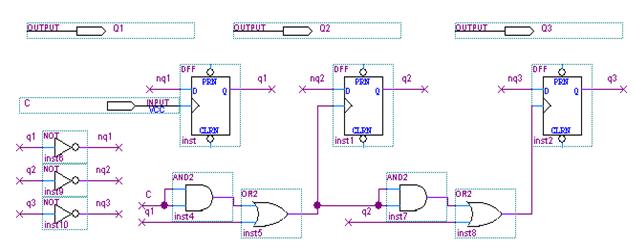

7 Создайте схему проверки синтезированного счетчика. На рисунке 8.7 в качестве примера приведена схема проверки асинхронного вычитающего трехразрядного счетчика со сквозным переносом на триггере dff.

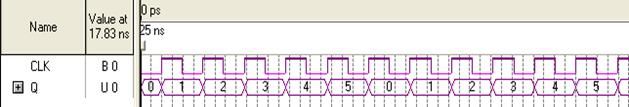

Рисунок 8.7 – Схема проверки асинхронного вычитающего счетчика со сквозным переносом на триггере dff 8 Исследуйте временные диаграммы работы построенного счетчика при произвольных фазовых соотношениях входных сигналов. На рисунке 8.8 в качестве примера приведены временные диаграммы работы вычитающего трехразрядного счетчика со сквозным переносом на триггере dff.

Рисунок 8.8 – Временные диаграммы асинхронного вычитающего счетчика со сквозным переносом на триггере dff 8.3.2 Контрольные вопросы 1 Дайте определение счетчика. 2 Назовите основные специфические параметры счетчиков. 3 Классификация счетчиков, принципы их построения. 4 Приведите схему и дайте краткую характеристику (укажите преимущества, недостатки и особенности работы) следующих типов счетчиков: a) суммирующие; b) вычитающие; c) реверсивные; d) асинхронные с последовательным переносом; e) асинхронные со сквозным переносом; f) синхронные со сквозным переносом; g) синхронные с параллельным переносом; h) синхронные с параллельным переносом на D-триггерах; i) синхронные с параллельным переносом на JK-триггерах. Лабораторная работа №3. Делители с произвольным постоянным коэффициентом деления Цель работы: изучить временные диаграммы работы делителей с произвольным постоянным коэффициентом деления (ДПКД), построенных по различным схемам. Порядок выполнения работы 1 Изучите до начала выполнения лабораторной работы методики синтеза делителей. 2 Синтезируйте схему исследования делителя в соответствии с установленным вариантом задания по таблице 8.5. Таблица 8.5 – Варианты заданий

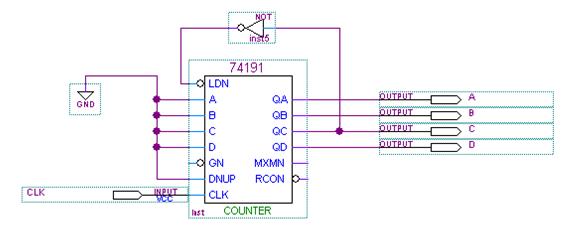

3 Создайте схему для исследования делителя в САПР Quartus II. На рисунке 8.9 в качестве примера приведена схема для исследования делителя, выполненного на базовой микросхеме 74191 с коэффициентом деления 4.

Рисунок 8.9 – Схема исследования делителя, выполненного на базовой микросхеме 74191 4 Исследуйте временные диаграммы работы делителя при произвольных фазовых соотношениях входных сигналов. На рисунке 8.10 в качестве примера приведены временные диаграммы работы построенного делителя.

Рисунок 8.10 – Временные диаграммы работы делителя выполненного на базовой микросхеме 74191 5 Исследуйте и приведите в отчете назначение всех входов и выходов базовой микросхемы делителя. 6 Синтезируйте схему ДПКД по 4-му методу построения делителей (синтез счетчиков с использованием теории цифровых автоматов) в соответствии с требованиями, приведенными в таблице 8.6. Таблица 8.6 – Варианты заданий

В таблицах 8.7-8.11 приведены результаты разработки делителя на 6 на базе триггера jkff (в таблице 8.7 приведена расширенная таблица истинности работы делителя, в таблицах 8.8–8.11 даны карты Карно для нахождения сигналов на управляющих входах). Таблица 8.7 – Таблица истинности работы делителя

Таблица 8.8 – Карта Карно для J3 Таблица 8.9 – Карта Карно для K3

J3=Q2Q1 K3=Q1 Таблица 8.10 – Карта Карно для J2 Таблица 8.11 – Карта Карно K2

J2=~Q3Q1 K2=Q1 7 Создайте схему проверки синтезированного ДПКД. На рисунке 8.11 в качестве примера приведена схема проверки делителя на 6.

Рисунок 8.11 – Схема проверки делителя на 6 8 Исследуйте временные диаграммы работы построенного делителя при произвольных фазовых соотношениях входных сигналов. На рисунке 8.12 в качестве примера приведены временные диаграммы работы построенного делителя на 6.

Рисунок 8.12 – Временные диаграммы работы делителя на 6 8.4.2 Контрольные вопросы 1 Дайте определение делителя. 2 Поясните методики синтеза ДПКД. 3 ДПКД на базе метода исключения лишних состояний. Укажите преимущества и недостатки. 4 ДПКД на базе метода искусственного принудительного насчета импульсов. Укажите преимущества и недостатки. 5 ДПКД на основе вычитающих счетчиков. Укажите преимущества и недостатки. 6 ДПКД на основе теории цифровых автоматов. Укажите преимущества и недостатки.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-06-26; просмотров: 1264; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.144.16.152 (0.007 с.) |