Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Лабораторная работа №4. РегистрыСодержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Цель работы: изучить временные диаграммы работы регистров, построенных по различным схемам. Порядок выполнения работы 1 Изучите до начала выполнения лабораторной работы методики синтеза регистров. 2 Соберите схему проверки стандартного регистра, тип которого в зависимости от установленного варианта задания приведен в таблице 8.12. Таблица 8.12 – Варианты заданий

3 Создайте схему для исследования указанного по варианту регистра в САПР Quartus II. На рисунке 8.13 в качестве примера приведена схема для исследования регистра 74174b.

Рисунок 8.13 – Схема исследования регистра 74174b 4 Исследуйте временные диаграммы работы регистра при произвольных фазовых соотношениях входных сигналов. На рисунке 8.14 в качестве примера приведены временные диаграммы работы построенного регистра.

Рисунок 8.14 – Временные диаграммы работы регистра построенного на базовой микросхеме 74174b 5 Исследуйте и приведите в отчете назначение всех входов и выходов базовой микросхемы регистра. 6 Синтезируйте схему четырехразрядного регистра с учетом требований, приведенных в таблице 8.13. Таблица 8.13 – Варианты заданий

7 Создайте схему проверки синтезированного регистра. На рисунке 8.15 в качестве примера приведена схема проверки трехразрядного параллельно-последовательного регистра построенного на триггерах jkff.

Рисунок 8.15 – Схема проверки трехразрядного параллельно-последовательного регистра построенного на триггерах jkff

8 Исследуйте временные диаграммы работы построенного регистра при произвольных фазовых соотношениях входных сигналов. На рисунке 8.16 в качестве примера приведены временные диаграммы работы трехразрядного параллельно-последовательного регистра построенного на триггерах jkff.

Рисунок 8.16 – Временные диаграммы трехразрядного параллельно-последовательного регистра построенного на триггерах jkff 8.5.2 Контрольные вопросы 1 Дайте определение регистра. 2 Принципы построения регистров. 3 Классификация регистров. 4 Основные параметры регистров. 5 Приведите схему и диаграммы работы, а также дайте краткую характеристику (укажите преимущества, недостатки, особенности работы) регистров следующих типов: a) параллельные регистры на основе RS- триггеров; b) параллельные регистры на основе D- триггеров. Какие D- триггеры (динамические или статические) рекомендуется использовать и почему? c) последовательные регистры на основе JK- триггеров. Укажите требования к временным параметрам; d) последовательные регистры на основе D- триггеров. Укажите требования к временным параметрам; e) последовательно-параллельные регистры на основе JK- триггеров; f) последовательно-параллельные регистры на основе D- триггеров; g) параллельно-последовательные регистры на основе JK- триггеров; h) параллельно-последовательные регистры на основе D- триггеров. 6 Универсальный регистр. Лабораторная работа №5. Комбинированные устройства Цель работы: разработать устройство, состоящее из нескольких компонентов и проверить его работоспособность. Порядок выполнения работы 1 Изучите до начала выполнения лабораторной работы методики построения цифровых автоматов, комбинационных и последовательных устройств. 2 Изучите методику построения и использования компонентов в САПР Quartus II. Разрабатываемое устройство будет состоять из трех компонентов: конечного автомата, последовательного и комбинационного устройства. 3 Соберите схему первого компонента устройства – комбинационной схемы, в соответствии с вариантом задания, приведенным в таблице 8.14. Таблица 8.14– Варианты заданий

Разработанный компонент должен иметь 4 входа и один выход. Выходная функция должна реализовывать функцию от четырех аргументов в соответствии с вариантом. 4 Исследуйте и приведите в отчете временные диаграммы работы компонента при произвольных фазовых соотношениях входных сигналов. 5 Создайте условное графическое обозначение созданного компонента для применения его в проекте, для чего выполните команду: Create/Update/Create Symbol Files for Current File. 6 Соберите схему второго компонента устройства – конечного автомата Таблица 8.15 – Варианты заданий

Автомат должен определять искомую последовательность и выдавать логическую «1» в случае ее обнаружения. Рассмотрим пример создания в графическом редакторе конечного автомата, который выделяет последовательность 110: Для создания цифрового автомата в САПР Quartus II с применением графического редактора следует выполнить следующие операции: – создайте новый проект; – откройте новый файл State Machine File (вкладка Design Files); – введите в таблицы входных и выходных контактов необходимые сигналы и их имена (см. рисунок 8.17);

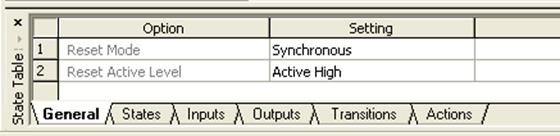

Рисунок 8.17 – Таблицы входных и выходных контактов – определите во вкладке General окна State Table вид синхронизации сигнала установки (res) и его активный уровень (см. рисунок 8.18);

Рисунок 8.18 – Таблица параметров сигнала синхронизации – укажите состояния цифрового автомата и дуги переходов между ними; – укажите на дугах переходов выражения, определяющие условия переходов между состояниями цифрового автомата (см. рисунок 8.19);

Рисунок 8.19 – Диаграмма состояний цифрового автомата – определите во вкладках Outputs и Actions окна State Table алгоритм формирования выходного сигнала (см. рисунок 8.20);

Рисунок 8.20 – Таблицы параметров выходного сигнала – укажите в окне Generate Others Files тип файла для автоматического создания условного графического обозначения цифрового автомата. Для выбора окна щелкните правой кнопкой “мыши” в любом месте графического редактора. Щелкните левой кнопкой “мыши” на кнопке “OK” (см. рисунок 8.21);

Рисунок 8.21 – Окно выбора автоматического создания УГО – укажите язык VHDL для описания цифрового автомата (см. рисунок 8.22);

Рисунок 8.22 – Таблица выбора языка описания – выполните автоматическую компиляцию описания цифрового автомата на языке VHDL; – проверьте и откорректируйте, при необходимости, описание цифрового автомата; – выполните компиляцию проекта; – проверьте работоспособность цифрового автомата по результатам анализа временных диаграмм (см. рисунок 8.23).

Рисунок 8.23 – Временные диаграммы работы цифрового автомата

Для создания цифрового автомата в САПР Quartus II с применением мастера создания цифровых автоматов следует выполнить следующие операции: – создайте новый проект; – откройте новый файл State Machine File (вкладка Design Files); – запустите State Machine Wizard; – выберите в диалоговом окне «State Machine Wizard» опцию «Create a new state machine design»; (см. рисунок 8.24)

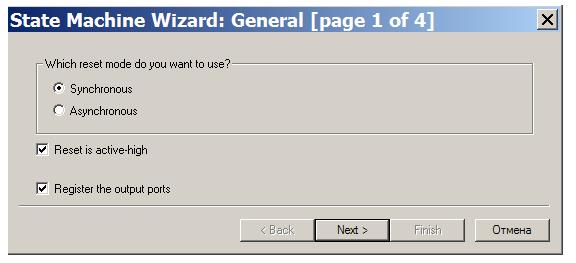

Рисунок 8.24 – Таблица выбора создания нового автомата – выберите на первой странице тип автомата (Synchronous или Asynchronous), активный уровень сигнала Reset и тип выходного контакта (Register) (см. рисунок 8.25);

Рисунок 8.25 – Таблица выбора параметров автомата – укажите в таблице имена состояний цифрового автомата и входных контактов, а также условия переходов между состояниями цифрового автомата (см. рисунок 8.26);

Рисунок 8.26 – Таблица выбора сигналов и состояний цифрового автомата – определите алгоритм формирования выходного сигнала(см. рисунок 8.27);

Рисунок 8.27 – Таблица выбора алгоритм формирования выходного сигнала

– проконтролируйте правильность ввода имен состояний, а также входных и выходных контактов (см. рисунок 8.28);

Рисунок 8.28 – Таблица контроля состояний, входных и выходных – проконтролируйте диаграмму состояний цифрового автомата (см. рисунок 8.29);

Рисунок 8.29 – Диаграмма состояний цифрового автомата – укажите тип файла для автоматического создания условного графического обозначения цифрового автомата и язык VHDL для его описания; – выполните автоматическую компиляцию описания цифрового автомата на языке VHDL; – проверьте и откорректируйте, при необходимости, описание цифрового автомата; – выполните компиляцию проекта; – проверьте работоспособность цифрового автомата по результатам анализа временных диаграмм. 6 Исследуйте и приведите в отчете временные диаграммы работы разработанного автомата при произвольных фазовых соотношениях входных сигналов. 7 Соберите схему счетчика в соответствии с вариантом задания, приведенным в таблице 8.16.

Таблица 8.16– Варианты заданий

Разрабатываемый счетчик должен содержать один счетный вход и один выход. Выход счетчика должен сигнализировать о достижении требуемого коэффициента пересчета выдачей сигнала с уровнем логической единицы.

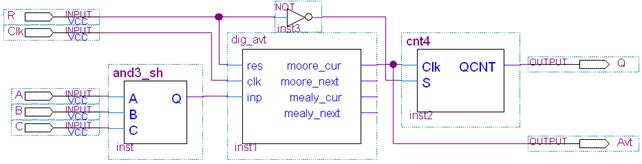

8 Исследуйте и приведите в отчете временные диаграммы работы разработанного счетчика и проверьте правильность его функционирования. 9 Соберите схему из трех созданных компонентов, соединенных в следующей последовательности: комбинационное устройство, конечный автомат, последовательное устройство (см. рисунок 8.30).

Рисунок 8.30 – Схема комбинированного устройства 10 Исследуйте и приведите в отчете временные диаграммы работы разработанного устройства и проверьте правильность его функционирования (см. рисунок 8.31).

Рисунок 8.31 – Временные диаграммы работы комбинированного устройства 8.6.2 Контрольные вопросы 1 Дайте определение автомата. 2 Какие виды автоматов вы знаете? 3 Дайте определение комбинационного устройства. Приведите примеры. 4 Какое устройство называется последовательным? Примеры. 5 Какими способами можно создать условное графическое обозначение компонента в САПР Quartus II?

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-06-26; просмотров: 868; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.146.107.49 (0.008 с.) |