Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

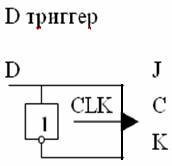

Получение D- триггера из Т- триггера.Содержание книги

Похожие статьи вашей тематики

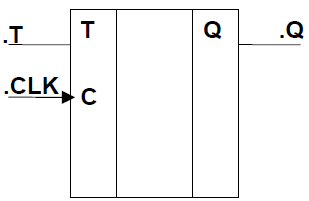

Поиск на нашем сайте Реализация на AHDL: TITLE "dtrig"; SUBDESIGN dtrig ( d,clk:input; q:output; ) variable DT:DFF; BEGIN DT.D=d; DT.CLK=clk; q= DT.Q; END; T-триггер. Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Реализация Т-триггера на базе D-триггера. Описание на языке проектирования AHDL (пакет MaxPlusII). Логика работы: По переднему фронту сигнала CLK меняет свое значение на противоположное, в случае, если на входе единица. Ниче не делает, если на входе ноль.

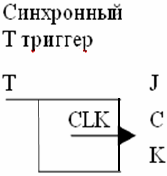

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2. Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком до 2. Асинхронный Т-триггер не имеет входа синхронизации С. Получение Т- триггера из D - триггера. Следовательно для получения Т – триггера на основе D – триггера достаточно соединить вход D с инверсным выходом, а вход синхронизации использовать как вход Т – триггера. Реализация на AHDL: TITLE "dtrig"; SUBDESIGN dtrig ( T_IN, CLK_IN: INPUT; Q: OUTPUT; ) VARIABLE q: TFF; BEGIN q.T = T_IN; q.CLK = CLK_IN; Q = q.Q; END;

JK-триггер. Таблица истинности. Логика работы (эпюры напряжений). Реализация RS, D, T триггеров на JK-триггере. Описание на языке проектирования AHDL (пакет Max Plus II). JK-триггер работает так же как RS-триггер, за одним исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации. Реализация различных триггеров на основе JK:

Реализация на AHDL: TITLE "dtrig"; SUBDESIGN dtrig ( J_IN, K_IN, CLK_IN:INPUT; Q:OUTPUT; ) VARIABLE JK:JKFF; BEGIN JK.J =J_IN; JK.K =K_IN; JK.CLK =CLK_IN; Q =JK.Q; END;

Асинхронный RS-триггер, реализованный через входа асинхронной установки и сброса (.prn,.clrn). Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Описание на языке проектирования AHDL (пакет Max Plus II).

|

||

|

Последнее изменение этой страницы: 2019-12-15; просмотров: 897; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.119 (0.008 с.) |