Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Классификация цифровых устройств.Содержание книги

Поиск на нашем сайте 1. По разрядости обрабатываемых данных. • Последовательные: входные и выходные данные поступают последовательно бит за битом. Для таких устройств характерны низкая скорость (данные идут с разделением по времени). С другой стороны, мало выводов.

Рисунок 37. Последовательное устройство. • Параллельные: данные одновременно поступают на все входы и считываются с выходов. Количество входов и выходов может быть разным. Быстродейственны, но имеют много выходов.

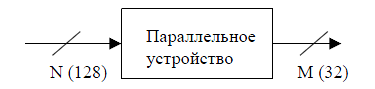

Рисунок 38. Параллельное устройство. • Последовательно-параллельное: данные поступают последовательно на вход, а выходят параллельно (или наоборот). Примеры: COM-порт, клавиатура. 2. По принципу действия.

1) Комбинационные (Состояние выходных сигналов однозначно определяется текущим состоянием входных сигналов)

2) Последовательностные (автоматы с памятью) (Состояние выходных сигналов зависит не только от текущего состояния входного сигнала, но и от всех предыдущих входных сигналов)

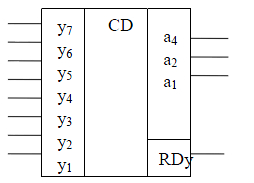

Типовые комбинационные логические устройства: шифратор без приоритета/ с приоритетом – назначение, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Шифратор (coder) – преобразует входной унарный вход в выходной двоичный. Обозначается как CD (ИВ). Рисунок 45. Условное обозначение шифратора.

RDy – выход, показывающий состояние готовности шифратора. Если N – количество входов, а m – количество выходов, и N = 2 m, то шифратор полный.

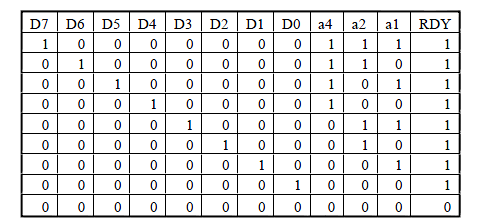

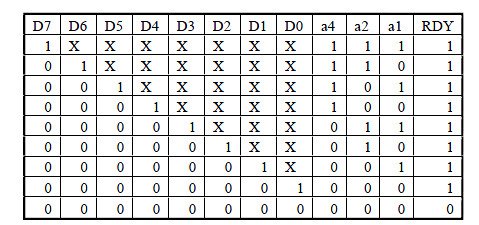

Рисунок 46. Таблица истинности шифратора. Если какому-либо входу задан приоритет, то шифратор приоритетный. Зададим приоритет входу D7. Таблица истинности такого шифратора выглядит следующим образом:

Рисунок 47. Таблица истинности приоритетного шифратора. Реализация на AHDL: TITLE "shifrator"; SUBDESIGN shifrator ( y0,y1,y2,y3,y4,y5,y6,y7:input; rdy, a1,a2,a4,a33: output; ) variable a5:tri;

BEGIN a5.oe=!rdy; a5.in=rdy; a33=a5.out;

table y0,y1,y2,y3,y4,y5,y6,y7 => rdy, a4,a2,a1; 0, 0, 0, 0, 0, 0, 0, 0 => 1, 0, 0, 0; 0, 0, 0, 0, 0, 0, 0, 1 => 0, 1, 1, 1; 0, 0, 0, 0, 0, 0, 1, 0 => 0, 1, 1, 0; 0, 0, 0, 0, 0, 1, 0, 0 => 0, 1, 0, 1; 0, 0, 0, 0, 1, 0, 0, 0 => 0, 1, 0, 0; 0, 0, 0, 1, 0, 0, 0, 0 => 0, 0, 1, 1; 0, 0, 1, 0, 0, 0, 0, 0 => 0, 0, 1, 0; 0, 1, 0, 0, 0, 0, 0, 0 => 0, 0, 0, 1; 0, 0, 0, 0, 0, 0, 0, 0 => 0, 0, 0, 0;

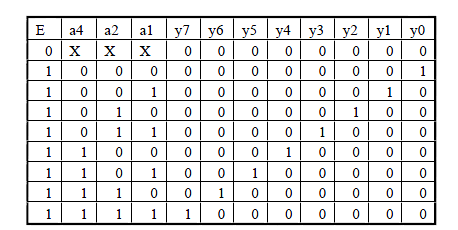

end table; END; Типовые комбинационные логические устройства: дешифраторы – назначение, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Дешифратор (decoder) – преобразует двоичный код в унарный. Из всех выходов дешифратора активный уровень имеется только на одном. Обозначается как DC (ИД). Если N – количество выходов, а m – количество входов, и N = 2 m, то дешифратор полный. Рисунок 41. Условное изображение дешифратора. Дешифраторы часто имеют разрешающий (управляющий, стробирующий) вход Е. При Е=1 дешифратор работает как обычно, при Е=0 на все выходы устанавливаются неактивные уровни независимо от сигналов на входе. Рисунок 42. Таблица истинности дешифратора. Наблюдается эффект бегущей единички, как видно из таблицы истинности. Это свойство используется в гирляндах. Описание на языке AHDL:

Часто в микросхемах дешифраторов делают несколько разрешающих входов, а разрешающей комбинаций является их конъюнкция.

Реализация на AHDL: TITLE "Laba2"; SUBDESIGN Laba2 ( y0,y1,y2,y3,y4,y5,y6,y7,y8,y9,y10,y11,y12,y13,y14,y15: output; cs1, cs2, a1,a2,a8,a4: input;

) BEGIN

y0 =!((!cs1 &!cs2) &!a8 &!a4 &!a2 &!a1); y1 =!((!cs1 &!cs2) &!a8 &!a4 &!a2 & a1); y2 =!((!cs1 &!cs2) &!a8 &!a4 & a2 &!a1); y3 =!((!cs1 &!cs2) &!a8 &!a4 & a2 & a1); y4 =!((!cs1 &!cs2) &!a8 & a4 &!a2 &!a1); y5 =!((!cs1 &!cs2) &!a8 & a4 &!a2 & a1); y6 =!((!cs1 &!cs2) &!a8 & a4 & a2 &!a1); y7 =!((!cs1 &!cs2) &!a8 & a4 & a2 & a1); y8 =!((!cs1 &!cs2) & a8 &!a4 &!a2 &!a1); y9 =!((!cs1 &!cs2) & a8 &!a4 &!a2 & a1); y10=!((!cs1 &!cs2) & a8 &!a4 & a2 &!a1); y11=!((!cs1 &!cs2) & a8 &!a4 & a2 & a1); y12=!((!cs1 &!cs2) & a8 & a4 &!a2 &!a1); y13=!((!cs1 &!cs2) & a8 & a4 &!a2 & a1); y14=!((!cs1 &!cs2) & a8 & a4 & a2 &!a1); y15=!((!cs1 &!cs2) & a8 & a4 & a2 & a1);

END;

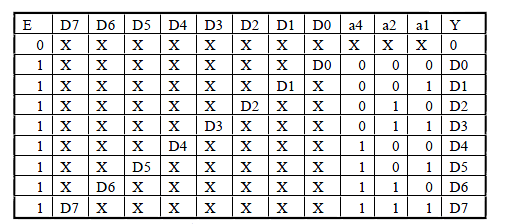

Типовые комбинационные логические устройства: мультиплексоры,– назначение, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Мультиплексор – осуществляет коммутацию одного из нескольких входов данных к выходу. Номер выбранного входа соответствует коду, поданному на адресные входы мультиплексора. Обозначается как MX (КП). Рисунок 43. Условное изображение мультиплексора.

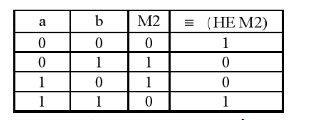

Рисунок 44. Таблица истинности мультиплексора. Вход Е – разрешающий, при Е=1 мультиплексор работает, при Е=0 мультиплексор закрыт. Типовые комбинационные логические устройства: цифровые компараторы – назначение, структура построения, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Цифровой компаратор – устройство сравнения двух двоичных чисел. Рисунок 39. Компаратор (а) и его структурная схема (б). Описание на языке AHDL:

Рисунок 40. Таблица истинности функции НЕ М2. Количество выводов равно количеству уравнений. Компаратор обозначается как SP.

|

||

|

Последнее изменение этой страницы: 2019-12-15; просмотров: 612; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.119 (0.008 с.) |