Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Аналоговый и цифровой сигнал. Сравнительный анализ. Достоинства и недостатки.Содержание книги

Похожие статьи вашей тематики

Поиск на нашем сайте

Аналоговый и цифровой сигнал. Сравнительный анализ. Достоинства и недостатки. Сигнал — это любая физическая величина изменяющаяся во времени. Аналоговый сигнал – сигнал, который может любые значения в определённых пределах Цифровой сигнал – сигнал, который может принимать только два значения (1,0) Операции над электрическими сигналами: • обработка (преобразование) сигнала; • передача сигнала; • хранение сигнала. Искажение сигнала. • Шум — это внутренние хаотические слабые сигналы любого электронного устройства (микрофона, транзистора, резистора и т. д.). • Наводки и помехи — это сигналы, приходящие на электронную систему извне и искажающие полезный сигнал

Недостатки аналога: • сигналы чувствительны к действию всевозможных паразитных сигналов (шумов, наводок, помех) • при обработке сигналов (при усилении, фильтрации), из-за несовершенства и не идеальности электронных устройств, искажается форма сигнала. • при передаче на большие расстояния и при хранении сигнал ослабляется. • шумы, помехи и наводки принципиально не поддаются точному расчету, поэтому точно описать поведение любых аналоговых устройств невозможно. • при изготовлении аналоговых устройств всегда присутствует технологическая операция – настройка устройства. У цифровых устройств – проверка работоспособности. • со временем из-за старения, изменяются параметры электронных компонентов, входящих в состав аналоговых устройств и, соответственно, изменяются характеристики самих аналоговых устройств. Преимущества цифровых устройств и сигналов: • небольшие отклонения от разрешенных значений не искажают цифровой сигнал, так как существуют зоны допустимых отклонений. • По сравнению с аналоговыми сигналами цифровые сигналы допускают гораздо более сложную и многоступенчатую обработку; более длительное хранение без потерь; более качественную передачу, • поведение цифровых устройств всегда можно абсолютно точно рассчитать и предсказать. • цифровые устройства гораздо меньше подвержены старению, так как небольшое изменение их параметров никак не отражается на их функционировании. • цифровые устройства проще проектировать и отлаживать.

Недостатки цифровых сигналов • Для надежного распознавания текущего состояния в каждом из своих разрешенных уровней цифровой сигнал должен оставаться хотя бы в течение какого-то минимального временного интервала. • аналоговый сигнал может принимать любое свое значение бесконечно малое Время => аналоговый сигнал определен в непрерывном времени (то есть в любой момент времени), а цифровой — в дискретном времени (то есть только в выделенные моменты времени). – Поэтому максимально достижимое быстродействие аналоговых устройств всегда принципиально больше, чем цифровых устройств. – Аналоговые устройства могут работать с более быстро меняющимися сигналами, чем цифровые. – Скорость обработки и передачи информации аналоговым устройством всегда может быть сделана выше, чем скорость ее обработки и передачи цифровым устройством. • цифровой сигнал передает информацию только двумя уровнями и изменением одного своего уровня на другой, • аналоговый передает информацию еще и каждым текущим значением своего уровня, то есть он более емкий с точки зрения передачи информации. – Соответственно, для передачи того объема полезной информации, который содержится в одном аналоговом сигнале, чаще всего приходится использовать несколько цифровых сигналов (обычно от 4 до 16). • в природе все сигналы аналоговые, то есть для преобразования их в цифровые сигналы и для обрато требуется применение специальных преобразователей (АЦП и ЦАП), что приводит к увеличению стоимости цифровых устройств.

Элементы цифрового сигнала. • Положительный сигнал (сигнал положительной полярности) — это сигнал, активный уровень которого — логическая единица. 0 — это отсутствие сигнала, 1 — сигнал пришел. • Отрицательный сигнал (сигнал отрицательной полярности) — это сигнал, активный уровень которого — логический нуль. 1 — это отсутствие сигнала, 0 — сигнал пришел. • Активный уровень сигнала — это уровень, соответствующий приходу сигнала, то есть выполнению этим сигналом соответствующей ему функции. • Пассивный уровень сигнала — это уровень, в котором сигнал не выполняет никакой функции. • Положительный фронт сигнала — это переход сигнала из нуля в единицу.

• Отрицательный фронт сигнала (спад) — это переход сигнала из единицы в нуль. • Передний фронт сигнала — это переход сигнала из пассивного уровня в активный уровень. • Задний фронт сигнала — это переход сигнала из активного уровня в пассивный уровень. • Тактовый сигнал (или строб) — управляющий сигнал, который определяет момент выполнения элементом или узлом его функции. • Шина — группа сигналов (и соответствующих физических линий передачи этих сигналов), объединенных по какому-то принципу. Например, шиной называют сигналы, соответствующие всем разрядам какого-то двоичного кода. • Инверсный выход — это выход, выдающий сигнал инверсной полярности по сравнению с входным сигналом. • Прямой выход — это выход, выдающий сигнал такой же полярности, какую имеет входной сигнал.

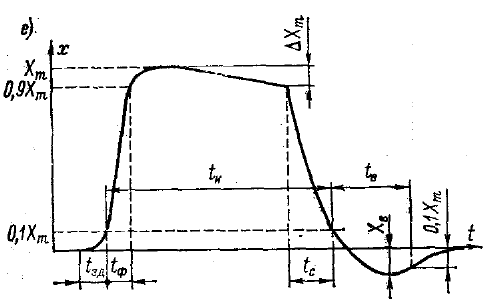

Реальная форма сигнала

Xm-максимальная амплитуда импульса. Xв – амплитуда восстановления. Дельта Хm – разность высоты импульса в конце и начале спада. tФ – активная длительность нарастания импульса tс – активная длительность спада импульса.

tв - время восстановления tэд - время задержки импульса tи – активная длительность прямоугольного импульса

Основные типы схем. По степени детализации изображения устройств различают три вида схем: • Принципиальная схема. – это наиболее подробная схема. – показывает все использованные в устройстве элементы и все связи между ними. – если схема строится на основе микросхем, то показывают номера выводов этих микросхем. – схема должна позволять полностью воспроизвести устройство. – Обозначения, используемые на принципиальной схеме жестко стандартизованы, отклонения от стандартов не рекомендуются. • Структурная схема. – это наименее подробная схема. – предназначена для отображения общей структуры устройства, основных блоков, узлов, частей и главных связей между ними. – Из данной схемы должно быть понятно, зачем нужно данное устройство, что оно делает в основных режимах работы, и как взаимодействуют его части. – Обозначения структурной схемы могут быть довольно произвольными, хотя некоторые общепринятые правила все-таки лучше выполнять. • Функциональная схема. – представляет собой гибрид структурной и принципиальной схем. – наиболее простые блоки, узлы, части устройства отображаются на ней, как на структурной схеме, а остальные — как на принципиальной схеме. – Функциональная схема позволяет понять всю логику работы устройства, все его отличия от других подобных устройств, но не позволяет без дополнительных работ воспроизвести это устройство. – обозначения, используемые на данных схемах, в части, показанной как структура, не стандартизованы, а в части, показанной, как принципиальная схема, стандартизованы. 5,6,7. Способы представления логических функций (словесное описание, таблица истинности, алгебраическая форма записи (дизъюнктивная форма записи)). Способы представления: 1) Словесное описание. 2) Табличное задание 3) Аналитический способ записи 4) Графическое задание

Примеры: Рассмотрим на примере двухвходовой функции ИЛИ. 1) Словесное описание. Существует функция f(x,y), зависящая от двух аргументов. Функция принимает значение 1, в случае равенства единице любого из двух аргументов (или обоих), и принимающая значение 0 в случае одновременного равенства нулю двух аргументов.

2) Таблица истинности. Описанное выше словесное описание можно свести в таблицу истинности.

3) Аналитический. Функция имеет следующий вид: f = x#y.

4) Графический способ.

Доопределение функции. Если функция

ДНФ – это такая нормальная форма, которая имеет вид дизъюнкций конъюнкций литералов. По – русски:

Любые логические функции выражаются через элементарные функции булева базиса.

СДНФ - это такая ДНФ, которая удовлетворяет трём условиям: § в ней нет одинаковых элементарных конъюнкций § в каждой конъюнкции нет одинаковых пропозициональных букв § каждая элементарная конъюнкция содержит каждую пропозициональную букву из входящих в данную ДНФ пропозициональных букв, причем в одинаковом порядке. По – русски:

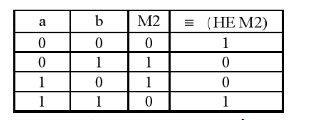

Любая сложная функция представляется в виде (на примере двухвходовой функции M2) (!A&B)# (A&!B)

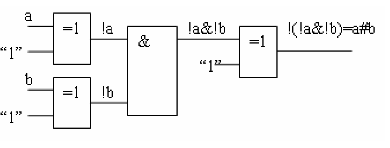

СКНФ -||-, только наоборот. По – русски: Любая сложная функция представляется в виде (на примере двухвходовой функции M2) (A#B)& (!A#!B) 8. Логические константы и переменные. Элементы булевой алгебры. Булев базис. Взаимное преобразование логических функций(правило Де Моргана), логические элементы. Логические константы. Логическое выражение может быть либо истиной, либо ложью. Истине соответствует константа True, значению "ложь" - константа False. Логические переменные. Это переменные, принимающие только 2 значения – 1, или 0. Элементы булевой алгебры. Булева алгебра – формальный аппарат описания логической стороны процессов, происходящих в цифровых устройствах. Оперирует с логическими переменными. Операции над этими переменными называются логическими операциями. Простейшие логические операции: НЕ Обозначение: Свойства: !!a=а И Обозначение: Y = a ^ b Y = ab Y = a ⋅ b Y = a & b Свойства: a & 0 = 0 a & 1 = a a & a = a a &!a = 0 Применение: ИЛИ Обозначение: Y = aVb Y = a + b Y = a#b Свойства: a # 0 = a a # 1 = 1 a # a = 1 a #!a = 1 Применение: М2(исключающее ИЛИ) Y = a ⊕ b Y = a $ b Свойства: а⊕0=а (а⊕b) ⊕b = а Применение: И-НЕ ИЛИ – НЕ Правило Де Моргана. !(!a &!b) = a # b!(!a #!b) = a & b

Логические элементы — устройства, предназначенные для обработки информации в цифровой форме.

ФПБ является базис И-НЕ.

Для проверки этого утверждения получим, используя только функцию И-НЕ, все функции Булева базиса. 1) ИЛИ При соединении входов функции 2И-НЕ получаем просто НЕ (очевидно). Берется 2 элемента 2И-НЕ с соединенными входами, их выходы прикрепляются к еще одному 2И-НЕ. Получаем на выходе третьего элемента!(!A&!B), что, согласно правилу ДеМоргана = A#B, читд. 1) И На входы 2И-НЕ подаем сигналы. На выходе имеем!(A&B). Подаем его на еще 1 элемент с соединенными входами(то есть, инвертируем) 2) НЕ -||- ФПБ является базис ИЛИ-НЕ. 1) ИЛИ 2) И 3) НЕ Все функции получаются точно такой же комбинацией логических элементов, согласно правилу Де Моргана.

Базис Жегалкина. Базис Жегалкина состоит из следующих логических элементов: 1) И 2) M2(Исключающее ИЛИ) 3) Константы «1» Докажем, что он является ФПБ.

1) НЕ Приведем таблицу истинности ф-и М2

Очевидно, что при подаче на один из входов постоянной единицы, на выходе М2 присутствует сигнал, подаваемый на второй из входов, но с обратным знаком. То есть, М2 работает как инвертор.

2) ИЛИ

Берем два инвертора на основе M2, полученных выше, пихаем их выходы на вход функции И, после чего ставим еще один такой инвертор. В результате получаем!(!A&!B), по ДеМоргану = A#В, читд.

3) И Уже есть в базисе.

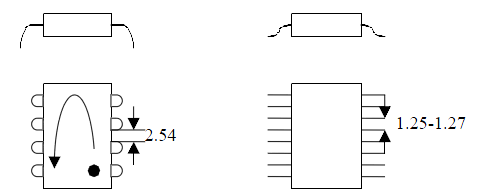

Пример обозначения микросхемы в отечественной системе обозначений. Рисунок 31. Пример обозначения микросхемы в отечественной системе обозначений. 1. Первая буква обозначает область применения: • Бытовой диапазон температур 0-700С, или коммерческий (обозначается буквой K). • Расширенный (industrial) -400С - +850С. • Автомобильный -400С - +1250С (у нас в стране этот диапазон не используется). • Военный -550С - +1250С (в обозначении таких микросхем буква отсутствует). 2. Тип корпуса микросхемы, может отсутствовать. Для каждого диапазона температур используется свой корпус. Типы корпусов. 1) Корпус типа DIP, пластмассовый (для коммерческого диапазона температур). На расширенном диапазоне температур используется керамический корпус. Выводы расположены с двух сторон, перпендикулярно корпусу. На корпусе присутствует ключ около вывода, с которого начинается нумерация выводов, нумерация идет против часовой стрелки. Количество выводов: 4, 8, 14, 16, 24, 28, 40. Расстояние между выводами 2.54 мм (100 милов) у зарубежных микросхем, 2.5 мм у российских.

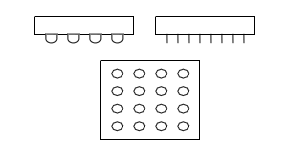

Рисунок 32. Корпуса типа DIP (слева) и SOIC (справа). 2) На автомобильном и военном диапазоне температур используется металлокерамический корпус типа SOIC. Расстояние между выводами 1.27 мм (100 милов) у зарубежных микросхем, 1.25 мм у российских. Выводы в позолоченном исполнении. Количество выводов: 8, 16, 14, 24, 28. 3) PLCC корпус. Выводы загнуты под корпус, можно помещать в колодку. Количество выводов: 32, 48, 52, 68, 84.

Рисунок 33. Корпуса PLCC (слева) и TQFP, PQFP (справа). 4) BGA, PGA корпуса: выводы под корпусом.

Рисунок 34. Корпуса BGA и PGA. 3. Номер серии микросхемы – от трех до четырех цифр. Технология, по которой изготовлена микросхема.

4. Функция микросхемы – 2 буквы.

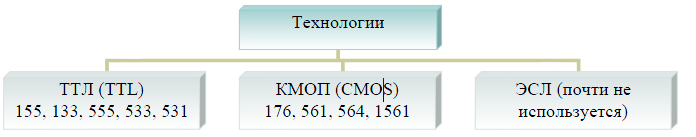

ЛА – И-НЕ ЛН – НЕ ЛИ – И ЛЛ – ИЛИ ЛЕ – ИЛИ-НЕ ЛП – М2 5. Номер микросхемы – от одной до трех цифр. Уточнение типа микросхемы внутри функциональной группы. ЛА3 – 2И-НЕ Пример обозначения микросхемы в зарубежной системе обозначений. Рисунок 35. Система обозначений фирмы Texas Instruments. 1. SN– идентификатор фирмы. 2. Температурный диапазон. 74 – коммерческий, 54 – военный. 3. Код серии. • Отсутствует – стандартная ТТЛ серия • LS (Low Power Shottky) – маломощная серия ТТЛШ • НС (High Speed CMOS) – высокоскоростная КМОП серия • HCT (High Speed CMOS with TTL inputs) – высокоскоростная серия КМОП, совместимая по входу с ТТЛ. • AC (Advanced CMOS) – улучшенная КМОП • ACT (Advanced CMOS with TTL inputs) – улучшенная КМОП, совместимая по входу с ТТЛ. Технологии ТТЛ (TTL) 155, 133, 555, 533, 531 КМОП (CMOS) 176, 561, 564, 1561 ЭСЛ (почти не используется) 4. Идентификатор специального типа (может отсутствовать). 5. Тип микросхемы. 6. Код типа корпуса: N – пластмассовый DIP корпус, J – керамический, T – плоский металлический. Характеристика технологий:

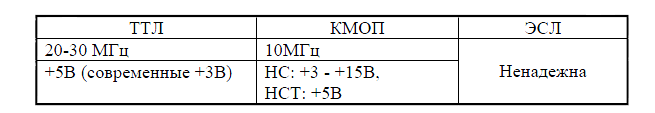

Потенциально ТТЛ технология быстрее, в отличие от КМОП, потребление питания не зависит от тактовой частоты. Обычно микросхемы разных серий легко сопрягаются между собой, то есть сигналы с выходов микросхемы одной серии можно подавать на входы другой. Однако бывают исключения при сопряжении КМОП и ТТЛ серий.

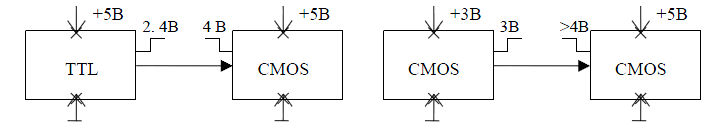

Рисунок 36. Сопряжение микросхем разных серий. В таком случае используется серия микросхем HCT. У нее занижен порог срабатывания, предназначена для стыковки ТТЛ и КМОП серий. 13. Типовые комбинационные логические устройства: шифратор без приоритета/ с приоритетом – назначение, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Шифратор (coder) – преобразует входной унарный вход в выходной двоичный. Обозначается как CD (ИВ). Рисунок 45. Условное обозначение шифратора.

RDy – выход, показывающий состояние готовности шифратора. Если N – количество входов, а m – количество выходов, и N = 2 m, то шифратор полный.

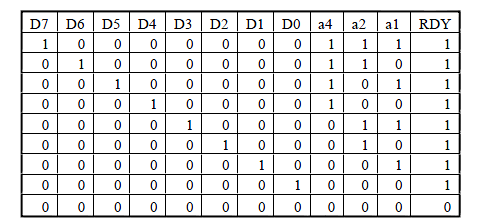

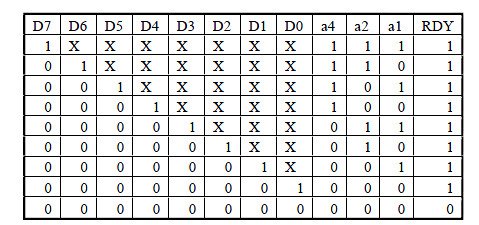

Рисунок 46. Таблица истинности шифратора. Если какому-либо входу задан приоритет, то шифратор приоритетный. Зададим приоритет входу D7. Таблица истинности такого шифратора выглядит следующим образом:

Рисунок 47. Таблица истинности приоритетного шифратора. Реализация на AHDL: TITLE "shifrator"; SUBDESIGN shifrator ( y0,y1,y2,y3,y4,y5,y6,y7:input; rdy, a1,a2,a4,a33: output; ) variable a5:tri;

BEGIN a5.oe=!rdy; a5.in=rdy; a33=a5.out;

table y0,y1,y2,y3,y4,y5,y6,y7 => rdy, a4,a2,a1; 0, 0, 0, 0, 0, 0, 0, 0 => 1, 0, 0, 0; 0, 0, 0, 0, 0, 0, 0, 1 => 0, 1, 1, 1; 0, 0, 0, 0, 0, 0, 1, 0 => 0, 1, 1, 0; 0, 0, 0, 0, 0, 1, 0, 0 => 0, 1, 0, 1; 0, 0, 0, 0, 1, 0, 0, 0 => 0, 1, 0, 0; 0, 0, 0, 1, 0, 0, 0, 0 => 0, 0, 1, 1; 0, 0, 1, 0, 0, 0, 0, 0 => 0, 0, 1, 0; 0, 1, 0, 0, 0, 0, 0, 0 => 0, 0, 0, 1; 0, 0, 0, 0, 0, 0, 0, 0 => 0, 0, 0, 0;

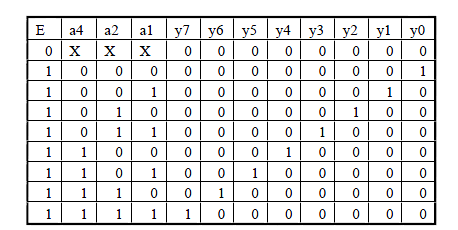

end table; END; Max Plus II). Примеры применения. Дешифратор (decoder) – преобразует двоичный код в унарный. Из всех выходов дешифратора активный уровень имеется только на одном. Обозначается как DC (ИД). Если N – количество выходов, а m – количество входов, и N = 2 m, то дешифратор полный. Рисунок 41. Условное изображение дешифратора. Дешифраторы часто имеют разрешающий (управляющий, стробирующий) вход Е. При Е=1 дешифратор работает как обычно, при Е=0 на все выходы устанавливаются неактивные уровни независимо от сигналов на входе. Рисунок 42. Таблица истинности дешифратора. Наблюдается эффект бегущей единички, как видно из таблицы истинности. Это свойство используется в гирляндах. Описание на языке AHDL:

Часто в микросхемах дешифраторов делают несколько разрешающих входов, а разрешающей комбинаций является их конъюнкция.

Реализация на AHDL: TITLE "Laba2"; SUBDESIGN Laba2 ( y0,y1,y2,y3,y4,y5,y6,y7,y8,y9,y10,y11,y12,y13,y14,y15: output; cs1, cs2, a1,a2,a8,a4: input;

) BEGIN

y0 =!((!cs1 &!cs2) &!a8 &!a4 &!a2 &!a1); y1 =!((!cs1 &!cs2) &!a8 &!a4 &!a2 & a1); y2 =!((!cs1 &!cs2) &!a8 &!a4 & a2 &!a1); y3 =!((!cs1 &!cs2) &!a8 &!a4 & a2 & a1); y4 =!((!cs1 &!cs2) &!a8 & a4 &!a2 &!a1); y5 =!((!cs1 &!cs2) &!a8 & a4 &!a2 & a1); y6 =!((!cs1 &!cs2) &!a8 & a4 & a2 &!a1); y7 =!((!cs1 &!cs2) &!a8 & a4 & a2 & a1); y8 =!((!cs1 &!cs2) & a8 &!a4 &!a2 &!a1); y9 =!((!cs1 &!cs2) & a8 &!a4 &!a2 & a1); y10=!((!cs1 &!cs2) & a8 &!a4 & a2 &!a1); y11=!((!cs1 &!cs2) & a8 &!a4 & a2 & a1); y12=!((!cs1 &!cs2) & a8 & a4 &!a2 &!a1); y13=!((!cs1 &!cs2) & a8 & a4 &!a2 & a1); y14=!((!cs1 &!cs2) & a8 & a4 & a2 &!a1); y15=!((!cs1 &!cs2) & a8 & a4 & a2 & a1);

END;

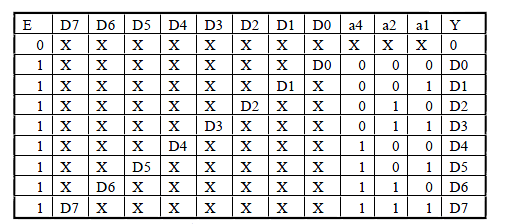

Типовые комбинационные логические устройства: мультиплексоры,– назначение, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Мультиплексор – осуществляет коммутацию одного из нескольких входов данных к выходу. Номер выбранного входа соответствует коду, поданному на адресные входы мультиплексора. Обозначается как MX (КП). Рисунок 43. Условное изображение мультиплексора.

Рисунок 44. Таблица истинности мультиплексора. Вход Е – разрешающий, при Е=1 мультиплексор работает, при Е=0 мультиплексор закрыт. Типовые комбинационные логические устройства: цифровые компараторы – назначение, структура построения, основные свойства, характеристики, описание на языке проектирования AHDL (пакет Max Plus II). Примеры применения. Цифровой компаратор – устройство сравнения двух двоичных чисел. Рисунок 39. Компаратор (а) и его структурная схема (б). Описание на языке AHDL:

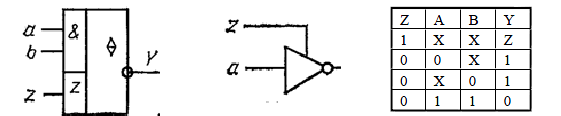

Рисунок 40. Таблица истинности функции НЕ М2. Количество выводов равно количеству уравнений. Компаратор обозначается как SP. Выход с третьим состоянием. Рисунок 53. Элемент с третьим состоянием. Добавляется третий транзистор. Когда на вход Z подается низкий уровень, транзистор VT3 заперт и не влияет на работу схемы элемента, выполняющего функцию И-НЕ. Если на входе Z высокий уровень, то транзистор VT3 открывается, а транзисторы VT1 и VT2 закрыты и уровень напряжения на выходе уже не определен. Такое третье состояние обозначается Z-состоянием.

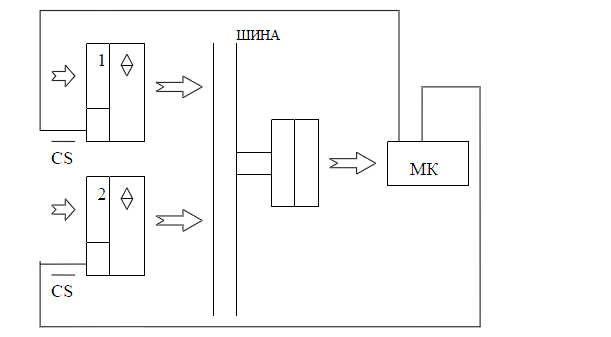

Рисунок 54. Обозначение элементов с третьим состоянием и их таблица истинности.

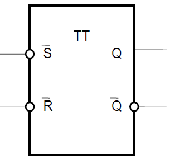

Рисунок 55. Двунаправленная передача данных. Для взаимного обмена данными различные устройства подключаются к связывающему их проводу – шине. По этой шине происходит обмен. Микроконтроллер МК управляет элементами 1 и 2. TRI -элементы в AHDL. a, b, c: input; variable Y_TRI: TRI; Y: node; Y=a&b; Y_TRI.IN=Y; Y_TRI.OE=c; 21. Триггеры. Назначение и классификация. Триггер – устройство, имеющее два устойчивых состояния, и переходящее из одного состояния в другое по внешнему сигналу. 1 и 0 – устойчивые состояния триггера. 0 – сброшенное состояние. 1 – установленное состояние. 0 ->1 – установка. 1 ->0 – сброс. Имеет два выхода - прямой Q и инверсный Q, причем! Q = Q. Типы триггеров. 1. По типу используемых входов. R – вход сброса (reset) S – вход установки (set) J – вход установки универсального триггера K – вход сброса универсального триггера T – счетный вход D – информационный вход C – синхровход триггера RS,JK,T,D – 4 основных типа Т,D – 2 основных типа, исп. в программируемой. логике V – дополнительный вход разрешения работы. 2. По моменту реакции на входной сигнал. -Асинхронные: изменяют состояние на выходе в момент изменения сигнала на входе. -Синхронные: изменяют состояние в строго определенные моменты времени, эти моменты определяются специальным синхросигналом С. 3. По типу активного логического сигнала на входах триггера. -Статические: реагируют на уровень сигнала. -Динамические: реагируют на переход сигнала (вход синхронизации С реагирует на передний фронт сигнала).

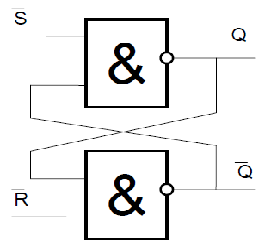

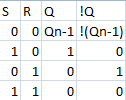

Асинхронный RS-триггер на элементах И-НЕ. Таблица истинности. Логика работы(эпюры напряжений). Варианты использования. Описание на языке проектирования AHDL (пакет Max Plus II). Условное обозначение:

Функциональная схема:

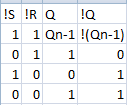

Таблица переходов:

RS-триггер используется для создания сигнала с положительным и отрицательным фронтами. Также RS-триггеры часто используются для исключения явления дребезга контактов. И, ясное дело, как элемент памяти. Реализация на AHDL: TITLE "RSasinh"; SUBDESIGN RSasinh ( s,r:input; q,q_:output; ) variable RST:SRFF; BEGIN q=!(!s&q_); q_=!(!r&q);

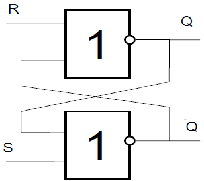

END; Асинхронный RS-триггер на элементах ИЛИ-НЕ. Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Описание на языке проектирования AHDL (пакет Max Plus II).

Условное обозначение:

Функциональная схема:

Таблица переходов:

Применение то же.

Реализация на AHDL: TITLE "RSasinh"; SUBDESIGN RSasinh ( s,r:input; q,q_:output; )

BEGIN q=!(r#q_); q_=!(s#q);

END;

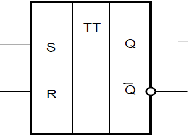

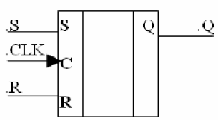

Синхронный RS-триггер. Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Описание на языке проектирования AHDL (пакет Max PlusII). Условное обозначение:

Таблица переходов:

Реализация на AHDL: TITLE "triggeryeaz"; SUBDESIGN triggeryeaz ( s,r,clk: INPUT;

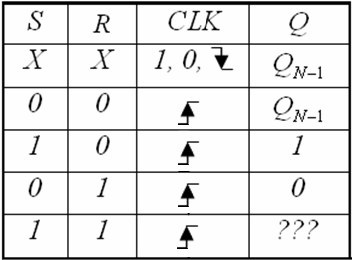

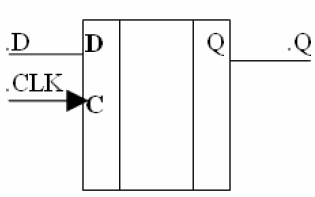

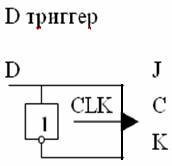

q1,q2: OUTPUT; ) VARIABLE RST:SRFF; BEGIN RST.S=s; RST.R=r; RST.CLK=clk; q1=RST.Q; q2=!RST.Q; END; Триггеры с динамическими и статическими входами. D-триггер. Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Реализация D-триггера на базе T-триггера. Описание на языке проектирования AHDL (пакет MaxPlus II). Также называется «триггер – защелка.»

Логика работы: При Сlk = 0 состояние триггера не меняется, а при Сlk = 1 состояние триггера совпадает со значением информации на входе D.

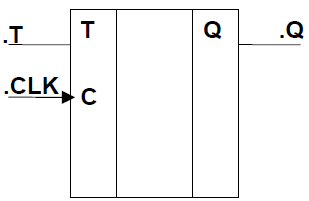

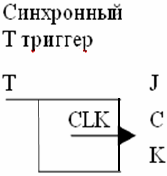

Основной триггер, применяющийся в микросхемах программируемой логики. Элемент задержки на 1 такт сигнала CLK. Нормирование сигналов по длительности. Так как информация на выходе остаётся неизменной до прихода очередного импульса синхронизации, D-триггер называют также триггером с запоминанием информации или триггером-защёлкой. Сохранение информации в D-триггерах происходит после спада импульса синхронизации. Реализация на AHDL: TITLE "dtrig"; SUBDESIGN dtrig ( d,clk:input; q:output; ) variable DT:DFF; BEGIN DT.D=d; DT.CLK=clk; q= DT.Q; END; T-триггер. Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Реализация Т-триггера на базе D-триггера. Описание на языке проектирования AHDL (пакет MaxPlusII). Логика работы: По переднему фронту сигнала CLK меняет свое значение на противоположное, в случае, если на входе единица. Ниче не делает, если на входе ноль.

Т-триггер часто применяют для понижения частоты в 2 раза, при этом на Т вход подают единицу, а на С — сигнал с частотой, которая будет поделена на 2. Т-триггер часто называют счётным триггером, так как он является простейшим счётчиком до 2. Асинхронный Т-триггер не имеет входа синхронизации С. JK-триггер. Таблица истинности. Логика работы (эпюры напряжений). Реализация RS, D, T триггеров на JK-триггере. Описание на языке проектирования AHDL (пакет Max Plus II). JK-триггер работает так же как RS-триггер, за одним исключением: при подаче логической единицы на оба входа J и K состояние выхода триггера изменяется на противоположное. Вход J аналогичен входу S у RS-триггера. Вход K аналогичен входу R у RS-триггера. При подаче единицы на вход J и нуля на вход K выходное состояние триггера становится равным логической единице. А при подаче единицы на вход K и нуля на вход J выходное состояние триггера становится равным логическому нулю. JK-триггер в отличие от RS-триггера не имеет запрещённых состояний на основных входах. На практике применяются только синхронные JK-триггеры, то есть состояния основных входов J и K учитываются только в момент тактирования, например по положительному фронту импульса на входе синхронизации. Реализация различных триггеров на основе JK:

Реализация на AHDL: TITLE "dtrig"; SUBDESIGN dtrig ( J_IN, K_IN, CLK_IN:INPUT; Q:OUTPUT; ) VARIABLE JK:JKFF; BEGIN JK.J =J_IN; JK.K =K_IN; JK.CLK =CLK_IN; Q =JK.Q; END;

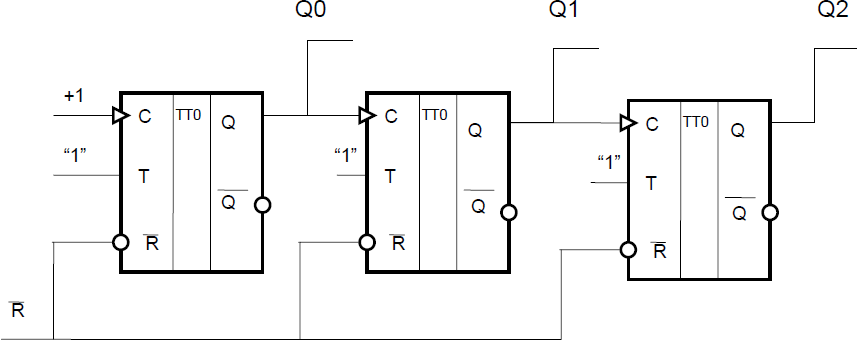

Асинхронный RS-триггер, реализованный через входа асинхронной установки и сброса (.prn,.clrn). Таблица истинности. Логика работы (эпюры напряжений). Варианты использования. Описание на языке проектирования AHDL (пакет Max Plus II). Счетчики. Общие сведения. Счетчики могут быть: Асинхронные счетчики на уменьшение с непосредственной связью. Структурная схема, эпюры напряжений. Достоинства и недостатки. Способы описания алгоритма функционирования счетчиков на языке проектирования AHDL.

Легко заметить, что единственное отличие между счетчиком на увеличение и на уменьшение – это использование инверсного выхода, вместо прямого.

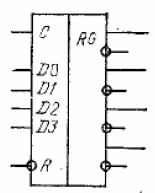

Функциональные узлы последовательностных логических устройств: параллельные регистры и регистровая память– назначение, основные типы. Структурные схемы, эпюры напряжений. Способы описания алгоритма функционирования на языке проектирования AHDL (пакет Max Plus II). Регистром называется последовательное или параллельное соединение триггеров. Параллельный регистр. Структурная схема:

Условное обозначение:

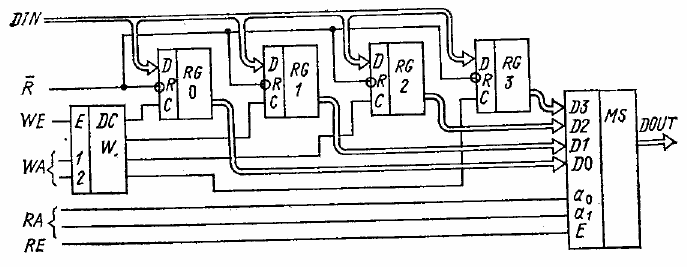

Схема регистровой памяти:

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно.

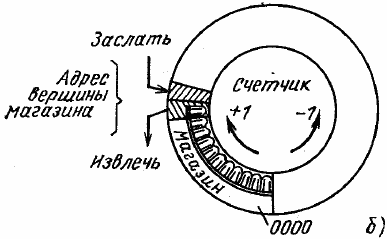

Память типа LIFO. Назначение, принцип работы, структурная схема. Варианты применения. LIFO — акроним Last In, First Out («последним пришёл — первым ушёл», англ.), абстрактное понятие в способах организации и манипулирования данными относительно времени и приоритетов. В структурированном линейном списке, организованном по принципу LIFO, элементы могут добавляться и выбираться только с одного конца, называемого «вершиной списка».[1] Структура LIFO может быть проиллюстрирована на примере стопки тарелок: чтобы взять вторую сверху, нужно снять верхнюю, а чтобы снять последнюю, нужно снять все лежащие выше. Часть регистров занята очередью, остальные—свободный резерв на случай ее увеличения. Адрес записи при постановке в очередь задается счетчиком хвоста очереди СТХВ. Сигнал Поставить в очередь, поступая на вход WE разрешения записи, записывает поступившие по входной шине DI данные в тот регистр памяти, номер которого хранится в СТХВ. По срезу сигнала Поставить в очередь выходной код счетчика хвоста увеличивается на 1, подготавливая адрес записи для очередного сигнала Поставить в очередь. При поступлении сигнала Извлечь из очереди на выходной шине DO появляется слово, хранящееся в том регистре памяти, номер которого задан кодом счетчика головы очереди СТГОЛ. По срезу сигнала выходной код счетчика увеличится на 1, подготовив для выдачи следующее слово, ставшее теперь первым в очереди. Переполнение счетчика хвоста очереди осложнений не вызовет, поскольку после максимально возможного кода счетчика ВСЕ ЕДИНИЦЫ в нем автоматически появится код ВСЕ НУЛИ. Очередь в своем кольце просто переползет хвостом через нулевую отметку счетчика. Так же со временем переползет и голова. В процессе нормальной работы очередь двигается в кольце значений адресов по часовой стрелке, хвостом вперед, удлиняясь или укорачиваясь в соответствии с флюктуациями активности передатчика. Перед началом работы оба счетчика сбрасываются в нуль. Схема буфера FIFO должна сигнализировать о двух особых ситуациях. Первая — буфер полон, тогда в него нельзя больше записывать, и нужно приостановить передатчик. Вторая — буфер пуст, тогда из него нельзя брать данные, и нужно приостановить приемник. Функциональная схема:

Диаграмма использования адресов:

Память типа FIFO. Назначение, принцип работы, структурная схема. Варианты применения. FIFO — акроним First In, First Out («первым пришёл — первым ушёл», англ.), абстрактное понятие в способах организации и манипулирования данными относительно времени и приоритетов. Это выражение описывает принцип технической обработки очереди или обслуживания конфликтных требований путём упорядочения процесса по принципу: «первым пришёл — первым обслужен» (ПППО). Тот, кто приходит первым, тот и обслуживается первым, пришедший следующим ждёт, пока обслуживание первого не будет закончено, и т.д Для организации обычной очередности служит буфер типа очередь, или буфер FIFO. Необходимость в таком буфере возника

|

|||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2019-12-15; просмотров: 801; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.225.209.237 (0.02 с.) |