Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Описание лабораторного стенда на базеСодержание книги

Поиск на нашем сайте

Отладочной платы XC2-XL.

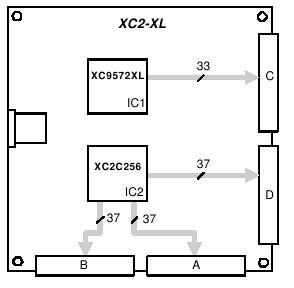

Стенд спроектирован студентами МЭИ Войтеком Д. и Розыевым А. на базе отладочной платы XC2-XL фирмы DIGILENT и изготовлен в ЗАО ТЕХНОР. Плата XC2-XL включает в себя две микросхемы ПЛИС типа CPLD: Xilinx CoolRunner-2 XC2C256 CPLD и Xilinx XC9572XL CPLD. Для программирования ПЛИС используется интерфейс JTAG. Контроллер JTAG и контроллер программирования флэш-ПЗУ располагаются на микросхеме ПЛИС и обеспечивают простую технологию ее перепрограммирования. Состав стенда: 1) Отладочная плата XC2-XL 2) Xilinx CoolRunner2 XC2C256 CPLD в корпусе типа TQ144; 3) Xilinx XC9572XL CPLD в корпусе VQ44 (не используется в лаб. работах); 4) тактовый генератор 1.8432 МГц 5) Модуль индикации и кнопок 6) 8 светодиодов 7) 8 фиксируемых переключателей 8) 4 нажимные кнопки 9) Корпус 10) Кабель JTAG для подключения к ПК по интерфейсу LPT 11) Автономное питание 3 В (две батарейка типа AA 1.5 В) 12) Блок питания от 5 до 9 В (нужен дополнительно, если не используются батарейки) Структурная схема отладочной платы представлена на рис. 3.

Рис. 3. Структурная схема отладочной платы XC2-XL

Модуль индикации и кнопок, разработанный студентами МЭИ, подключен к разьему B, который в свою очередь подключен к ПЛИС XC2C256 (см. рис. 4).

Рис.4. Схема соединения ПЛИС XC2C256 и XC9572XL с разьемами. (при программировании платы микросхему XC9572XL обходим -bypass) Ниже таблица соответствия номеров светодиодов и кнопок,установленных на лицевой панели стенда с именам контактов корпуса микросхемы ПЛИС XC2C256-TQ144 (Cool-Runner 2):

Для включения светодиода нужно подать высокий потенциал на соединенный с ним контакт микросхемы ПЛИС. При замыкании контакта кнопки на контакт подается высокий потенциал. Источник тактового сигнала подключен к контакту P38 ПЛИС. Формат файла ограничений. ucf такой же, как для ПЛИС типа FPGA NET "имя_сигнала" LOC = "имя_контакта";

например NET "clk" LOC = "p38"; --такт clk на тактовый генератор NET "left" LOC = "p138";-- вход left на кнопку NET "q<0>" LOC = "p126"; --выход q<0> на светодиод NET "q<1>" LOC = "p129";

Краткое описание архитектуры ПЛИС типа CPLD. CPLD (Complex Programmable Logic Devices) - это сложные программируемые логические устройства (ПЛИС).Их архитектура произошла от PLD типа PAL и PLМ (ПМЛ и ПЛМ). В CPLD для хранения конфигурации ПЛИС используется энергонезависимая память типа Флеш (Flash и EEPROM). Микросхемы этого типа могут быть использованы для создания нестандартных АЛУ, дешифраторов, мультиплексоров и т.д., т.е. для создания таких устройств, где используются логические функции большого числа переменных и небольшое количество триггеров. Внутреннюю структуру ПЛИС типа CPLD поясним на примере ПЛИС семейства XC9500. Каждая микросхема семейства XC9500 представляет собой подсистему, состоящую из множества функциональных блоков (ФБ) и блоков ввода-вывода (БВВ), соединённых переключающей матрицей (ПМ) (Рис. 5). БВВ обеспечивает буферизацию всех входов и выходов микросхемы. Каждый ФБ содержит 18 макроячеек со структурой ПЛА и позволяет получить 18 логических функций от 36 переменных. ПМ обеспечивает подачу любых выходных сигналов ФБ и входных сигналов на входы ФБ. От 12 до 18 выходных сигналов каждого ФБ (в зависимости от количества выводов в корпусе) и соответствующие сигналы разрешения выхода поступают непосредственно на блоки ввода-вывода.

Рис. 5. Архитектура семейства XC9500 Функциональный блок (ФБ) состоит из 18 независимых макроячеек, каждая из которых обеспечивает выполнение комбинаторной и/или регистровой функции. Кроме этого, на ФБ приходят сигналы разрешения выхода, установки/сброса и глобальной синхронизации. Каждый ФБ формирует 18 выходных сигналов, которые поступают на ПМ, а также передаются в БВВ. Логика внутри ФБ представляет собой матрицу логических произведений (термов). Каждый функциональный блок имеет внутренние цепи обратной связи, что позволяет любому количеству выходных сигналов ФБ поступать в свою собственную программируемую матрицу элементов И, не выходя за пределы ФБ. Любая макроячейка в микросхеме семейства XC9500 может выполнять как комбинаторную, так и регистровую функции. Каждая макроячейка имеет пять основных и четыре дополнительных входа, поступающих на распределитель термов. Распределитель термов управляет назначением пяти прямых термов к каждой макроячейке. Переключающая матрица осуществляет коммутацию сигналов, поступающих с выходов ФБ и из БВВ на входы ФБ внутри микросхемы. Блок ввода-вывода выполняет функцию интерфейса между логическими сигналами и контактами микросхемы. Каждый БВВ содержит буферы ввода и вывода, а также мультиплексор сигналов разрешения выхода и схему программирования пользовательского "общего" вывода. Необходимо отметить, что CPLD часто способны обеспечить 100%-тное использование логических ресурсов, благодаря разветвлённой схеме внутренних соединений и возможности комбинировать ресурсы логических генераторов. Семейство CoolRunner отличается от семейства XC9500 пониженным энергопотреблением (статический ток не превышает 100 мкА). Функциональные блоки ПЛИС CoolRunner содержат матрицу PLA(ПЛМ), в отличие от PAL-матрицы в XC9500. Различие между ними заключается в том, что PLA-матрица состоит из элементов И, за которыми располагается матрица элементов ИЛИ. Применение матрицы PLA позволяет оптимизировать использование ресурсов микросхемы при реализации сложных проектов. Более подробно с архитектурой CPLD можно ознакомиться по источникам приведенным в конце данного пособия, а также на сайтах www.plis.ru и www.xilinx.ru в разделе документации. Контрольные вопросы Помимо вопросов,перечисленных в описании лаб.работы номер 2 для FPGА при защите добавляются вопросы,специфические для ПЛИС и САПР CPLD.

1.Сравните быстродействие вашего проекта при реализации на ПЛИС типа FPGA и CPLD 2.Сравните сложность схем вашего проекта при реализации на FPGA и CPLD 3.Сравните затраты мощности, потребляемой от источника питания вашего проекта при реализации на FPGA и CPLD. 4. Почему в отчете синтезатора САПР при реализации проектов на CPLD нет оценок задержек и быстродействия и как их узнать? 5.Насколько сложную функцию может реализовать макроячейка CPLD? 6.В блоках ввода-вывода ПЛИС типа FPGA и CPLD есть триггера двойной скорости передачи данных – что дает их использование и как они построены? 7. В каком типе ПЛИС конфигурация не теряется при отключении питания?

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-17; просмотров: 458; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 18.117.91.116 (0.008 с.) |