Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Графические и текстовые формы отчетовСодержание книги

Поиск на нашем сайте

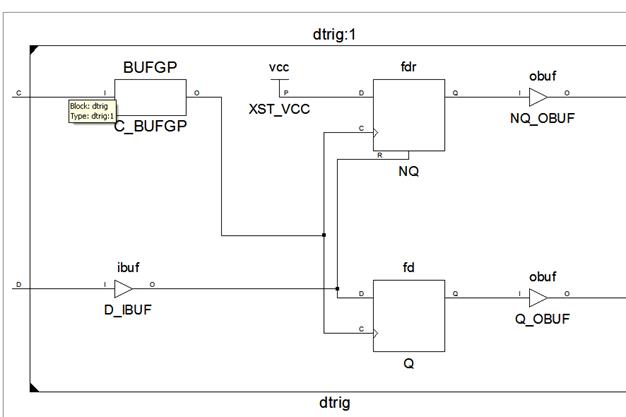

Ниже на рисунке представлено изображение принципиальной электрической схемы проекта(technological view) при синтезе схемы в логическом базисе ПЛИС типа FPGA Spartan 3.

Ниже на рисунке представлено изображение принципиальной электрической схемы проекта(technological view) при синтезе схемы в логическом базисе ПЛИС типа CPLD типа Cool Runner 2

Ниже представлен фрагмент текстового отчета синтезатора о результатах выполнения синтеза проекта на микросхеме ПЛИС типа FPGA СПАРТАН 3.

Final Results RTL Top Level Output File Name: dtrig.ngr Top Level Output File Name: dtrig Output Format: NGC Optimization Goal: Speed Keep Hierarchy: No Design Statistics # IOs: 4 Cell Usage: # BELS: 1 # VCC: 1 # FlipFlops/Latches: 2 # FD: 1 # FDR: 1 # Clock Buffers: 1 # BUFGP: 1 # IO Buffers: 3 # IBUF: 1 # OBUF: 2

Device utilization summary: Selected Device: 3s200ft256-5 Number of Slices: 0 out of 1920 0% Number of IOs: 4 Number of bonded IOBs: 4 out of 173 2% IOB Flip Flops: 2 Number of GCLKs: 1 out of 8 12%

TIMING REPORT NOTE: THESE TIMING NUMBERS ARE ONLY A SYNTHESIS ESTIMATE. FOR ACCURATE TIMING INFORMATION PLEASE REFER TO THE TRACE REPORT GENERATED AFTER PLACE-and-ROUTE. Clock Information: -----------------------------------+------------------------+-------+ Clock Signal | Clock buffer(FF name) | Load | C | BUFGP | 2 | -----------------------------------+------------------------+-------+ No asynchronous control signals found in this design

Timing Summary: Speed Grade: -5 Minimum period: No path found Minimum input arrival time before clock: 2.352ns Maximum output required time after clock: 6.216ns Maximum combinational path delay: No path found

Фрагмент процесса определения оценок затрачиваемой мощности при проектировании на ПЛИС типа FPGA Spartan 3. Для получения оценок динамической мощности А)надо во временных ограничениях проекта (timing constraints) указать период синхросигнал С. По данным синтезатора задержка выхода схемы триггера менее 10 нс. Примем период равным 20 нс.

Б)далее раскрыть (щелкнув правой кнопкой мыши) пункт имплементации Place&Route, выбрать Generate text power report.Фрагмент отчета ниже. Power Supply Summary --------------------------------------------------------- | | Total | Dynamic | Static Power | --------------------------------------------------------- | Supply Power (mW) | 41.90 | 0.91 | 40.99 |

Ниже представлен фрагмент текстового отчета синтезатора о результатах выполнения синтеза проекта на микросхеме ПЛИС CoolRunner2. Final Results RTL Top Level Output File Name: dtrig.ngr Top Level Output File Name: dtrig Output Format: NGC Optimization Goal: Speed Keep Hierarchy: Yes Target Technology: CoolRunner2 CPLDs Macro Preserve: YES XOR Preserve: YES Clock Enable: YES wysiwyg: NO

Design Statistics # IOs: 4 Cell Usage: # BELS: 1 # INV: 1 # FlipFlops/Latches: 2 # FD: 2 # IO Buffers: 4 # IBUF: 2 # OBUF: 2.

Фрагмент процесса определения оценок затрачиваемой мощности при проектировании на ПЛИС типа Cool Runner 2.

Надо задать временные ограничении.Потом выбрать в меню доступных процессов Optional Implementation Tools. В этом пункте выбрать Analize Power Distribution, а далее Generate Text Power Report. Фрагмент отчета при незадании временных ограничений (т.е. только статический ток в проекте)

|

|||||

|

Последнее изменение этой страницы: 2016-12-17; просмотров: 373; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.44.46 (0.006 с.) |