Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Общее представление о плис Spartan-3 с архитектурой FPGAСодержание книги

Поиск на нашем сайте

ВВЕДЕНИЕ Эта часть лабораторного практикума по дисциплине «Современные методы проектирования цифровых систем» базируется на одноименном курсе лекций [1] и ранее изученных студентами дисциплинах: «Моделирование», «Схемотехника ЭВМ», «Теория автоматов», «Запоминающие устройства ЭВМ». Практикум ставит целью начальное ознакомление с системой автоматизации проектирования (САПР) программируемых логических интегральных схем (ПЛИС) фирмы XILINX (смотрите список литературы [1-3] и список интернет- ресурсов в приложении В[1-16]).Изучение проводится на примерах простых проектов. Подобные проекты студенты уже выполняли на младших курсах, но на другой элементной базе и без использования САПР. Под проектом некоторого устройства ниже понимается совокупность модулей (файлов), которые содержат информацию, необходимую для выполнения его автоматизированной разработки на базе САПР ПЛИС фирмы XILINX. В качестве аппаратной базы практикума кафедры ВМСС МЭИ используется ПЭВМ с ОС WINDOW и отладочная плата, содержащая ПЛИС. В данном пособии как пример рассматривается ПЛИС[4-5] с архитектурой FPGA Spartan-3 (или Spartan-3Е) и ПЛИС с архитектурой CPLD (CoolRunner2) и версия САПР фирмы XILINX типа ISE[] (см.сайт www.xilinx.com и литературу [1-3]). Для описания проектов должен быть использован один из языков описания аппаратуры (HDL ─ Hardware Description Language), а именно язык VHDL (Very High Speed Integrated Circuit Hardware Description Language)[6-9].Однако студенты могут использовать и другие языки-VERILOG,SYSTEM VERILOG,C++ и др. Известно большое число подобных практикумов за рубежом. В приведенной библиографии имеются ссылки на практикумы фирмы XILINX (www.xilinx.com) и Университета Сан-Хосе (www.engr.sjsu.edu/crabill/). Основные отличия данного практикума: наличие большого числа вариантов заданий (зарубежные практикумы не предполагают стремления студентов к списыванию); использование языка VHDL, а не VERILOG; использование наработок курсового проекта по проектированию запоминающего устройства (ЗУ), выполненного студентами на младшем курсе. Первое лабораторное задание ─начальное знакомство с САПР ПЛИС ISE фирмы XILINX (свободно распространяется версия ISE WebPack) на примере общего для всех студентов проекта D-триггера (краткие выдержки из документации фирмы XILINX по ISE вынесены в приложение А). Второе задание ─ разработка и реализация на ПЛИС типа FPGA индивидуального для каждого студента проекта простого узла типа счетчик, коммутатор и т.п. В продолжение этой работы на следующем занятии эта же схема реализуется на ПЛИС типа CPLD. Третье задание ─ проектирование и реализация в виде конечного автомата устройства управления ЗУ на ПЛИС(на третьем курсе это УУ реализовалось как схема в базисе микросхем СИС типа кр1533,1554 и т.п.). Однако сильные студенты могут работать по индивидуальным планам, выполнить нестандартные задания и использовать более современные САПР и ПЛИС. Например выполнять лабораторные работы по программе университета Сан-Хосе (www.engr.sjsu.edu/crabill/) или на платах типа ARTYX или ZEDBOARD,имеющихся на кафедре. ЛАБОРАТОРНАЯ РАБОТА № 1 Введение в САПР ISE фирмы XILINX Цель работы

Цель работы состоит в ознакомлении с основными подсистемами и этапами автоматизированного проектирования программируемых логических интегральных схем (ПЛИС) фирмы XILINX на примере проекта простого узла типа D-триггер(см.литературу[4─7] и приложение В [4─5]). Приобретаемые навыки ─ умение выполнять простейшие проектные процедуры в САПР ISE, понимать отчеты и сообщения САПР. Для изучения используется инструментальный комплект Spartan-3 Starter Kit фирмы XILINX, включающий, в том числе, отладочную плату XILINX Spartan-3 Starter Board, свободно распространяемую версию системы проектирования ISE WebPack (см. [1-3], сайт www.xilinx.com, приложения А Б, Г), в которую входит подсистема моделирования ISE Simulator(ISIM). Можно установить дополнительно более мощную систему моделирования ModelSim (см. приложение В и сайт фирмы www.modeltech.com). Все студенты выполняют одно и то же задание. Работа рассчитана на 4 часа.

Домашняя подготовка

Ознакомиться с описанием лабораторной работы. Вспомнить соответствующие разделы конспекта лекций и рекомендуемую литературу по схемотехнике [4-5], по языку VHDL [6─9], а также изучить: · приложения А и Б данного пособия; · начальное руководство Quick Start в разделе Help системы ISE или его перевод на кафедре ВМСС или материалы по ISE в [1─2]; · документацию на ПЛИС Spartan-3 и отладочную плату с этой микросхемой (или ПЛИС Spartan-3Е и плату СПАРТАН 3Е). Ответить на контрольные вопросы (см. список в конце описания данной работы). Составить план работы, содержащий последовательность действий, необходимых для выполнения лабораторного задания.

Лабораторное задание

Перед началом работы проводится коллоквиум. При выполнении работы необходимо пользоваться инструкцией по САПР ISE, приведенной в приложении А, либо в [1],либо в интернет по адресу в приложении В[1]. Т.е запустить САПР, создать проект и включить в него файлы описаний триггера на VHDL,провести функциональное (поведенческое) моделирование работы триггера, провести синтез схемы. Просмотреть полученные в результате этого этапа - функциональную и принципиальную схемы, получить оценки потребляемой мощности, задать конструкторские ограничения, провести реализацию схемы на микросхеме ПЛИС, выполнить посттрассировочное(временное) моделирование и сравнить временные диаграммы поведенческой и посттрассировочной моделей, подготовить файл программирования ПЛИС и загрузить его в отладочную плату, проверить работу триггера на плате. Результатом работы является демонстрация функционирования триггера на отладочной плате с ПЛИС Spartan-3. По итогам работы составляется отчет, который должен содержать результаты домашней подготовки, описание на языке VHDL проекта и тестирующей программы, протокол работы с САПР, временные диаграммы поведенческого и посттрассировочного моделирования, отчеты САПР с оценками затрат оборудования ПЛИС Spartan-3 на реализацию схемы D-триггера, показатели быстродействия схемы, данные о статической и динамической составляющих мощности, потребляемой от источника питания, выводы и заключение по лабораторной работе, включающие найденные ошибки, результаты сравнения ожидаемых результатов с полученными фактическими. Пример отчета смотрите в файлах документации по практикуму. Завершается выполнение работы защитой. ЛАБОРАТОРНАЯ РАБОТА № 2 Цель работы

Цель работы состоит в изучении основных элементов ПЛИС типа FPGA Spartan-3, методов построения синтезабельных описаний простых цифровых узлов на языке VHDL, методов их тестирования и в более глубоком изучении САПР ПЛИС ISE [1-3] (см. приложение Б) на примере индивидуального проекта типового узла ЭВМ. Приобретаемые навыки ─ умение реализовать простейшие узлы цифровой аппаратуры на ПЛИС. Во всех индивидуальных заданиях предполагается построение описания простого узла на языке VHDL; его функциональная верификация моделированием; создание файла проектных ограничений, автоматизированный логический синтез и конструкторское проектирование в базисе ПЛИС, временное моделирование (с учетом задержек в элементах и проводниках); загрузка проекта в ПЛИС, расположенную на отладочной плате; статическая проверка функционирования узла по свечению светодиодов платы. Дополнительно к основному заданию для оценки «отлично» рекомендуется освоить схемный редактор ECS и ввести в САПР ISE структурное описание проектируемого узла, используя библиотеку графических примитивов ISE [1-2]. Если пользоваться только одними встроенными в отладочную плату средствами индикации, то полная (статическая и динамическая) верификация проекта на плате не всегда может быть выполнена. На большой частоте тактового генератора платы- 50 МГц (подробнее см. краткое описание отладочной платы в приложении В [5]) мелькание сигналов незаметно. Возможно использование в качестве тактового генератора одной из нажимных кнопок платы, при условии включения в версию проекта для стадии отладки на плате схемы устранения дребезга контактов. Либо можно включать в проект схему понижения частоты тактовых сигналов. Примеры описания счетчика, используемого для понижения частоты, и RS-триггера или счетчика для гашения дребезга контактов см. ниже. Работа рассчитана на 4 часа. Задания выбираются из табл. 1 по номеру студента в группе. Для упрощения проверки описания проектируемого узла предлагается обозначать входы и выходы схем так, как указано в задании. Таблица 1 Варианты заданий

Домашняя подготовка

Ознакомиться с описанием данной лабораторной работы. Изучить соответствующие разделы конспекта лекций и рекомендуемую литературу по ПЛИС, отладочной плате и САПР [1─5], по языку VHDL [6─9]. См. также список интернет- ресурсов в приложении В. Ответить на контрольные вопросы (см. список в конце описания работы). Разработать функциональное описание узла и тестирующей программы на языке VHDL, самопроверяющийся тест, предполагаемую схему узла в базисе ПЛИС с архитектурой FPGA (функциональное описание ПЛИС Spartan-3 см. приложение В[4,5]),С помощью САПР оценить быстродействие требуемые на реализацию схемы узла ресурсы и потребляемую мощность от источника питания. ПЛИС, предложить статический тест проверки работоспособности схемы узла на отладочной плате. Если необходимо для проведения верификации проекта на отладочной плате, разработать узел подавления дребезга контактов и включить его в версию проекта, загружаемую в плату. Учесть возможные при проектировании ограничения на нежелательность наличия в проекте управляемых тактовых сигналов (см. UCF-файлы)

Лабораторное задание

Перед началом работы проводится коллоквиум. При выполнении работы необходимо пользоваться рекомендациями, приведенными в приложениях А, Б. Результатом работы является демонстрация временных диаграм моделирования и функционирования спроектированного узла на отладочной плате. По итогам работы составляется отчет, который включает: результаты домашней подготовки ─ описание проекта и тестирующей программы на языке VHDL; протокол работы с САПР; временные диаграммы моделирования (поведенческого ─ Behavioral Simulation) и пост-трассировочного (Post Place & Routing), отчет программы оценки потребляемой проектом мощности. комментарий, поясняющий их отличие; фрагменты отчета САПР (Synthesis Report) с оценками затрат оборудования ПЛИС (количество LUT, количество триггеров и т.п.) и быстродействия (Timing Report) полученной схемы узла (требуемое время предустановки – setup данных по отношению к тактовому сигналу, время задержки- offset после такта и т.п.); функциональную схему узла (как ее рисует синтезатор ─ RTL-View) и принципиальную электрическую(технологическую) схему- technological view; отчет –оценка, сделанная САПР по потребляемой мощности, выводы по проделанной работе, включающие найденные ошибки, результаты сравнения ожидаемых результатов с фактическими. Завершается выполнение работы защитой. ВАРИАНТЫ работы в классе кафедры 1) Полученные дома в ходе подготовки к работе VHDL-файлы вы переписываете в классе кафедры ПК в каталог с вашим именем в каталоге вашей группы E/Laby/Poliakov и создаете проект(см приложение). Работать с флешки не стоит- замедление на порядок). Потом BIT-файл проекта через кабель, подключенный к ЛРТ порту ПК загружается в плату с ПЛИС СПАРТАН-3. 2) Если у вас ноутбук, там обычно ЛПТ порта нет и можно работать с платой через переходник или USB порт. Но кабель USB имеется только для плат СПАРТАН- 3Е.(это кабель такой же, как кабель подключения ПК к принтеру). Напоминаем, что цоклевка контактов ПЛИС Спартан 3Е отличается от Спартан 3-см.описание лаб.1. Подробное описание плат см. на сайте фирмы Digilent.

Примеры описаний узлов, которые можно использовать для исключения влияния дребезга контактов кнопок платы

Эти узлы рекомендуется оформлять как отдельные модули и включать наряду с проектируемым узлом в модуль проекта высшего уровня - он нужен только на стадии отладки проекта на плате!,а при моделировании и синтезе можно обойтись без него!. Вариант 1. RS- триггер (можно взять тактируемый или не тактируемый). На вход S подать сигнал от одной нажимной кнопки, на вход R ─ сигнал от другой нажимной кнопки. Сигнал на выходе Q будет равным «1» в течение периода времени от нажатия кнопки S и до нажатия кнопки сброса R. Выход Q поступает как тактовый сигнал в проверяемый узел. ВОПРОСЫ из области проектирования синхронных схем 1 Что такое полностью синхронная схема? 2 Перечислите преимущества и недостатки синхронных схем перед асинхронными 3 Какие требования к сети разводки синхросигналов в микросхеме 4 Что такое балансировка конвейера и латентность? 5 Чем определяется предел быстродействия конвейерной схемы 6 В каких случаях дублирование регистров лучше чем установка буферных элементов? 7 Какая примерно нагружечная способность элементов 1533 серии и 1554? 8 Что такое управляемые синхросигналы в схеме и их + и –

ВОПРОСЫ из области автоматизированного синтеза и опций управления синтезаторов 1 Какие критерии проектирования схемы вы можете задавать синтезатору? 2 Чем отличается схема показанная в RTL-view от схемы Technological view? 3 Чем отличаются временные диаграммы поведенческого и посттрассировочнового моделирования? 4 Что дает посттрассировочное моделирование при нарушении времен предустановки-удержания в схеме? 5 Почему отличаются времена задержек в проводниках в отчетах синтезатора и в отчетах трассировщика(в постсинтезном моделировании? 6 Влияют ли задержки, указанные в исходном описании схемы на VHDL на задержки схемы, построенной синтезатором? 7 Как получить отчет о потребляемой мощности спроектированной схемы?

ВОПРОСЫ из области языков описания аппаратуры,автоматизированного синтеза и моделирования 1. Чем отличается поведенческое и структурное описание [7-9] проекта на языке VHDL? 2. Что надо сделать, чтобы построить самопроверяющуюся тестирующую программу? См. пример теста для D-триггера в лаб.1. 3. Зачем подключают пакет STD_LOGIC_1164? Какие значения могут принимать сигналы пакета? 4. Что такое синтезабельное подмножество VHDL? 5. В чем основное отличие синтезабельных описаний схем с памятью и комбинационных схем? 6. Чем отличаются такие элементы ПЛИС FPGA,как LUT, SLICE, CLB? 7. Есть ли в составе внутренних элементов ПЛИС Спартан- 3 тристабильные буферы? 8. Как описывать тристабильные буферы на VHDL? 9. Какие действия в САПР ISE необходимы для синтеза спроектированного узла? 10. Как вывести на экран ПЭВМ временную диаграмму всех (включая внутренние) сигналов моделируемой схемы? 11. Как убрать дребезг контактов отладочной платы при проверке схем? 12. При каких ошибках описания при синтезе появляются триггеры защёлки? 13. Как узнать быстродействие и задержки в схеме на ПЛИС по отчетам САПР? 14. Постройте таблицу истинности функции «И» в 4х значном алфавите 0,1,X,Z (подмножество 9-значного алфавита STD_LOGIC_1164). 15. В алфавите std_logic реализована функция разрешения rezolved.,позволяющая реализовать общую шину. Как реализовать функцию МОНТАЖНОЕ «И»? 16. Чем отличаются ПЛИС типа CPLD от типа FPGA? 17. Когда у Вас в проекте много триггеров, какой тип ПЛИС- CPLD или FPGA предпочтительнее выбрать? 18. Чем отличается VHDL описание D-триггера с асинхронным сбросом и D-триггера с синхронным сбросом? 19. Какой пакет надо подключать, чтобы использовать операцию сложения (+) над векторами типа std_logic_vector?. 20. Чем отличаются в пакете std_logic_1164 типы std_logic и std_ulogic? 21.Какие данные можно увидеть в отчете САПР ISE SYNTHESYS REPORT? 22.Какие порядки задержек логических элементов ПЛИС и трассировочных элементов(сравните на примере вашего проекта) 23. Какие задержки входных и выходных буферов ПЛИС? 24.Можно ли проследить пути с максимальными задержками вашего проекта по отчетам САПР? 25 Какой оператор надо включить в текст конструкторских ограничений при разводе тактового сигнала не через тактовый буфер? 26. Перечислите параллельные операторы VHDL 27.Чем отличается семантика оператора присваивания в переменную от присваивания в сигнал? 28. Перечислите последовательные операторы VHDL 29.Чем отличается семантика оператора присваивания в переменную от присваивания в сигнал 30. Что надо учитывать при наличии операторов присваивания в один и тот же сигнал в разных процессах?. 31. Как вы представляете реализацию RS триггера защелки описанного в примере антидребезговой схемы в базисе ПЛИС?

Элементы языка описания аппаратуры VHDL-------------------------------- 32.Отличаются ли в языке VHDL имена (идентификаторы), набранные большими буквами от имен, набранных малыми? 33.Чем VHDL операторы присваивания в сигнал (signal)<= отличаются от операторов присваивания в переменные(variable):=? 34.Чем инерциальная задержка сигнала отличается от транспортной и какими средствами VHDL они отображаются? 35.Приведите основные отличия языка VHDL от языка программирования типа PASCAL. 36. Перечислите параллельные операторы VHDL. 37. Зачем нужно описание компонент в структурных моделях. 38. Чем отличаются поведенческие и структурные VHDL описания? 39.Как строится типичная тестирующая программа (test bench)? 40 В каком алфавите выполнено описание Д-триггера и зачем используется функция to_X01 в правой части оператора присваивания в сигнал? 41. Что правильнее - использовать в описании условия срабатывания триггера if (clk='1' and clk'event) then или if rising_edge(clk) then?

ВОПРОСЫ ДЛЯ тех, кто защищает работу гораздо позднее сроков – например в декабре 1) Опишите функциональную и структурную модель дешифратора 2 х4 2) Опишите функциональную и структурную модель мультиплексора 2 х 1 3)Опишите функциональную и структурную модель RS-триггера-защелки 4)Опишите функциональную модель Д- триггера с установочным входом 5)Опишите функциональную модель J-K триггера 6) Опишите функциональную модель буферного элемента с тристибильным выходом типа АП3

ЛАБОРАТОРНАЯ РАБОТА №2 Вариант выполнения на ПЛИС типа СPLD

Отладочной платы XC2-XL.

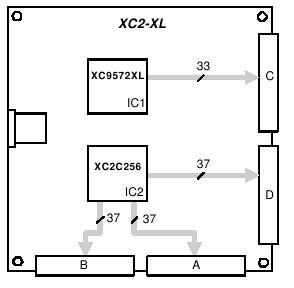

Стенд спроектирован студентами МЭИ Войтеком Д. и Розыевым А. на базе отладочной платы XC2-XL фирмы DIGILENT и изготовлен в ЗАО ТЕХНОР. Плата XC2-XL включает в себя две микросхемы ПЛИС типа CPLD: Xilinx CoolRunner-2 XC2C256 CPLD и Xilinx XC9572XL CPLD. Для программирования ПЛИС используется интерфейс JTAG. Контроллер JTAG и контроллер программирования флэш-ПЗУ располагаются на микросхеме ПЛИС и обеспечивают простую технологию ее перепрограммирования. Состав стенда: 1) Отладочная плата XC2-XL 2) Xilinx CoolRunner2 XC2C256 CPLD в корпусе типа TQ144; 3) Xilinx XC9572XL CPLD в корпусе VQ44 (не используется в лаб. работах); 4) тактовый генератор 1.8432 МГц 5) Модуль индикации и кнопок 6) 8 светодиодов 7) 8 фиксируемых переключателей 8) 4 нажимные кнопки 9) Корпус 10) Кабель JTAG для подключения к ПК по интерфейсу LPT 11) Автономное питание 3 В (две батарейка типа AA 1.5 В) 12) Блок питания от 5 до 9 В (нужен дополнительно, если не используются батарейки) Структурная схема отладочной платы представлена на рис. 3.

Рис. 3. Структурная схема отладочной платы XC2-XL

Модуль индикации и кнопок, разработанный студентами МЭИ, подключен к разьему B, который в свою очередь подключен к ПЛИС XC2C256 (см. рис. 4).

Рис.4. Схема соединения ПЛИС XC2C256 и XC9572XL с разьемами. (при программировании платы микросхему XC9572XL обходим -bypass) Ниже таблица соответствия номеров светодиодов и кнопок,установленных на лицевой панели стенда с именам контактов корпуса микросхемы ПЛИС XC2C256-TQ144 (Cool-Runner 2):

Для включения светодиода нужно подать высокий потенциал на соединенный с ним контакт микросхемы ПЛИС. При замыкании контакта кнопки на контакт подается высокий потенциал. Источник тактового сигнала подключен к контакту P38 ПЛИС. Формат файла ограничений. ucf такой же, как для ПЛИС типа FPGA NET "имя_сигнала" LOC = "имя_контакта";

например NET "clk" LOC = "p38"; --такт clk на тактовый генератор NET "left" LOC = "p138";-- вход left на кнопку NET "q<0>" LOC = "p126"; --выход q<0> на светодиод NET "q<1>" LOC = "p129";

Краткое описание архитектуры ПЛИС типа CPLD. CPLD (Complex Programmable Logic Devices) - это сложные программируемые логические устройства (ПЛИС).Их архитектура произошла от PLD типа PAL и PLМ (ПМЛ и ПЛМ). В CPLD для хранения конфигурации ПЛИС используется энергонезависимая память типа Флеш (Flash и EEPROM). Микросхемы этого типа могут быть использованы для создания нестандартных АЛУ, дешифраторов, мультиплексоров и т.д., т.е. для создания таких устройств, где используются логические функции большого числа переменных и небольшое количество триггеров. Внутреннюю структуру ПЛИС типа CPLD поясним на примере ПЛИС семейства XC9500. Каждая микросхема семейства XC9500 представляет собой подсистему, состоящую из множества функциональных блоков (ФБ) и блоков ввода-вывода (БВВ), соединённых переключающей матрицей (ПМ) (Рис. 5). БВВ обеспечивает буферизацию всех входов и выходов микросхемы. Каждый ФБ содержит 18 макроячеек со структурой ПЛА и позволяет получить 18 логических функций от 36 переменных. ПМ обеспечивает подачу любых выходных сигналов ФБ и входных сигналов на входы ФБ. От 12 до 18 выходных сигналов каждого ФБ (в зависимости от количества выводов в корпусе) и соответствующие сигналы разрешения выхода поступают непосредственно на блоки ввода-вывода.

Рис. 5. Архитектура семейства XC9500 Функциональный блок (ФБ) состоит из 18 независимых макроячеек, каждая из которых обеспечивает выполнение комбинаторной и/или регистровой функции. Кроме этого, на ФБ приходят сигналы разрешения выхода, установки/сброса и глобальной синхронизации. Каждый ФБ формирует 18 выходных сигналов, которые поступают на ПМ, а также передаются в БВВ. Логика внутри ФБ представляет собой матрицу логических произведений (термов). Каждый функциональный блок имеет внутренние цепи обратной связи, что позволяет любому количеству выходных сигналов ФБ поступать в свою собственную программируемую матрицу элементов И, не выходя за пределы ФБ. Любая макроячейка в микросхеме семейства XC9500 может выполнять как комбинаторную, так и регистровую функции. Каждая макроячейка имеет пять основных и четыре дополнительных входа, поступающих на распределитель термов. Распределитель термов управляет назначением пяти прямых термов к каждой макроячейке. Переключающая матрица осуществляет коммутацию сигналов, поступающих с выходов ФБ и из БВВ на входы ФБ внутри микросхемы. Блок ввода-вывода выполняет функцию интерфейса между логическими сигналами и контактами микросхемы. Каждый БВВ содержит буферы ввода и вывода, а также мультиплексор сигналов разрешения выхода и схему программирования пользовательского "общего" вывода. Необходимо отметить, что CPLD часто способны обеспечить 100%-тное использование логических ресурсов, благодаря разветвлённой схеме внутренних соединений и возможности комбинировать ресурсы логических генераторов. Семейство CoolRunner отличается от семейства XC9500 пониженным энергопотреблением (статический ток не превышает 100 мкА). Функциональные блоки ПЛИС CoolRunner содержат матрицу PLA(ПЛМ), в отличие от PAL-матрицы в XC9500. Различие между ними заключается в том, что PLA-матрица состоит из элементов И, за которыми располагается матрица элементов ИЛИ. Применение матрицы PLA позволяет оптимизировать использование ресурсов микросхемы при реализации сложных проектов. Более подробно с архитектурой CPLD можно ознакомиться по источникам приведенным в конце данного пособия, а также на сайтах www.plis.ru и www.xilinx.ru в разделе документации. Контрольные вопросы Помимо вопросов,перечисленных в описании лаб.работы номер 2 для FPGА при защите добавляются вопросы,специфические для ПЛИС и САПР CPLD.

1.Сравните быстродействие вашего проекта при реализации на ПЛИС типа FPGA и CPLD 2.Сравните сложность схем вашего проекта при реализации на FPGA и CPLD 3.Сравните затраты мощности, потребляемой от источника питания вашего проекта при реализации на FPGA и CPLD. 4. Почему в отчете синтезатора САПР при реализации проектов на CPLD нет оценок задержек и быстродействия и как их узнать? 5.Насколько сложную функцию может реализовать макроячейка CPLD? 6.В блоках ввода-вывода ПЛИС типа FPGA и CPLD есть триггера двойной скорости передачи данных – что дает их использование и как они построены? 7. В каком типе ПЛИС конфигурация не теряется при отключении питания? Вопросы и упражнения по схемотехнике для тех,кто плохо учился на 3- м курсе см в приложении Г.

Лабораторная работа № 3 Типичные ошибки Помимо ошибок, указанных в описании лабораторной работы № 2, к типичным для работы № 3 можно отнести следующие: 1) При реализации УУ в виде конечного автомата студенты используют несинтезабельное подмножество языка VHDL (см. рекомендации в HELP САПР ISE и [7-9]) и не соблюдают строгий стиль описания автоматов; 2) Надо вспомнить изученные на младших курсах типы автоматов ─ МУРА или МИЛИ─ и различия способов кодирования состояний автоматов (САПР позво

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-12-17; просмотров: 780; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.5 (0.047 с.) |