Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Набор команд для управления системойСодержание книги

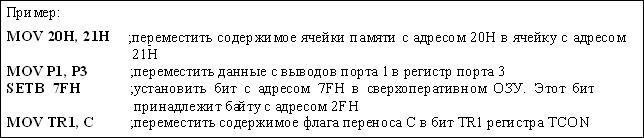

Поиск на нашем сайте Конфигурируемая система на кристалле поддерживает все команды семейства микроконтроллеров стандарта 8051. Выполнение этих команд, установка флагов и битов состояния являются аналогичными за исключением синхронизации, отличие которой определяется двумя причинами: 1. Машинный цикл ускоренного микроконтроллера стандарта 8051 составляет 4 такта, в отличие от машинного цикла оригинального микроконтроллера стандарта 8051, который составляет 12 тактов; 2. Ускоренный микроконтроллер выполняет за один машинный цикл одну выборку, т.е. на одну выборку приходятся 4 такта, а оригинальный микроконтроллер осуществляет две выборки за машинный цикл, и на одну выборку приходятся 6 тактов. Преимуществом ускоренного микроконтроллера является то, что за один машинный цикл он выполняет только одну выборку. В большинстве случаев число машинных циклов равно числу операндов, приходящихся на команду. Команды безусловного перехода и вызова подпрограммы требуют дополнительный цикл для определения нового адреса. В целом ускоренный микроконтроллер значительно уменьшает число ложных выборок и, как следствие, число циклов, тем самым, повысив эффективность в сравнении с оригинальным микроконтроллером стандарта 8051. Способы адресации Микроконтроллер стандарта 8051 поддерживает 8 различных способов адресации, описание которых будет представлено ниже: 1. регистровая адресация; 2. прямая адресация; 3. косвенно-регистровая; 4. непосредственная; 5. косвенно-индексная; 6. относительная адресация; 7. абсолютная; 8. длинная адресация. Регистровая адресация В регистровой адресации используются 8 рабочих регистров (R0-R7) активного на данный момент банка регистров, размещенного в сверхоперативном ОЗУ. Последние три бита в коде команды указывают на выбранный регистр. Существуют 4 банка рабочих регистров, активным из которых может быть один и выбирается через два бита RS1-RS0 в регистре слова состояния PSW. Таким образом, одна и та же команда может получить доступ к различным регистрам, если менять номер активного банка. Аккумулятор АСС, регистр B, текущий указатель данных DPTR, определяемый битом DPS.0, и CY могут быть также адресуемы, как регистры.

Прямая адресация Прямая адресация является единственным способом обращения к регистрам специального назначения SFR и обеспечивает доступ к целой области нижних 128 байтов сверхоперативного ОЗУ. Прямая адресация также используется для обращения к бит-адресуемой области памяти, которая занимает адресное пространство 20H-2FH в сверхоперативном ОЗУ. Эти биты имеют индивидуальный адрес от 00H до 7FH, необходимый для прямого обращения к ним. Несколько регистров специального назначения также являются бит-адресуемыми. Адрес отдельных битов таких регистров указывается добавлением битовой позиции к адресу регистра.

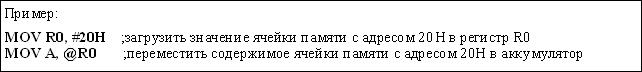

Косвенно-регистровая адресация Этот способ адресации используется для доступа к ячейкам памяти сверхоперативного ОЗУ в пределах верхних 128 байт. Адрес целевой ячейки хранится в регистрах R0 и R1 активного на данный момент банка. Изменяя содержимое регистров R0 и R1, одна и та же команда может обращаться к различным ячейкам памяти. Этот способ адресации не может быть использован для обращения к регистрам специального назначения.

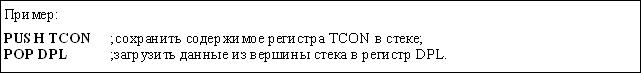

Операции со стеком также являются примером косвенно-регистровой адресации. Но в данном случае вместо рабочих регистров R0 и R1 используется стековый указатель SP для хранения адреса вершины стека. Косвенно-регистровая адресация используется в командах PUSH и POP.

Этот способ адресации также используется для обращения к внешней памяти данных. Для этого предназначена команда MOVX и регистры R0, R1, DPTR или DPTR1. Если в качестве указателей адреса используются регистры R0 и R1, то младшие 8 бит адреса будут содержаться в одном из этих регистров, а старшие 8 бит в регистре специального назначение P2. Для этого содержимое в регистре P2 должно быть определено заранее, до того, как будет использована команда обращения к внешней памяти данных. Если в качестве указателей адреса используются регистры DPTR и DPTR1, то в одном из них будет содержаться целый 16-ти битный адрес.

Непосредственная адресация Этот способ адресации используется для непосредственного задания константы в коде команды. Широко применяется для конфигурации рабочих регистров и регистров специального назначения, а также для проведения операций маскирования.

Косвенно-индексная адресация Применяется для доступа к байту памяти программ косвенным путем. Адрес целевой ячейки памяти вычисляется как сумма содержимого счетчика команд PC или DPTR/DPTR1 и индекса в аккумуляторе ACC. Значение результата всегда сохраняется в аккумуляторе поверх значения индекса.

Относительная адресация Относительная адресация применима в командах короткого перехода на ячейку памяти программ в пределах 128 байт относительно текущего адреса в счетчике команд. Адрес перехода состоит из двух дополнительных адресов смещения, которые прибавляются к содержимому счетчика команд. Относительный адрес занимает по размеру один байт памяти, таки образом, смещение может быть в пределах от -128 до +127 байт.

Абсолютная адресация Этот способ адресации используется в командах перехода ACALL и AJMP. Операндом этих команд являются 11 бит адреса, открывающих доступ к любой ячейки памяти программ в пределах 2К текущей страницы. 16-ти битный адрес перехода складывается из 5 старших битов адреса следующей команды (РС+2) и 11 младших битов кода текущей команды. Полученный адрес будет указывать на байт в памяти программ в пределах страницы, размером 2 Кбайт, относительно первого байта следующей команды.

Длинная адресация Используется в командах LJMP и LCALL для организации длинных переходов и ветвлений в любую ячейку памяти программ в пределах 64 Кбайт.

Система прерываний Конфигурируемая система на кристалле Е5 имеет структуру прерываний с тремя уровнями приоритета и с 12-тью возможными источниками прерываний, каждый из которых имеет индивидуальный флаг, вектор прерывания и бит разрешения. Прерывания микроконтроллера стандарта 8051 также имеют индивидуальные биты приоритета. Кроме того, все виды прерываний – за исключением высокоприоритетного прерывания, – могут быть глобально разрешены или запрещены. Источники прерываний Внешние сигналы прерываний INR0 и INR1 могут быть активны как по срезу, так и по уровню, в зависимости от конфигурации битов IТ0 и IТ1 в регистре TCON. В этом регистре флаги IE0 и IE1 выставляются в случае появления сигнала на соответствующем выводе и являются генераторами прерываний. Соответствующий флаг будет очищен после выполнения программы по обслуживанию прерывания, если внешний сигнал прерывания активен по срезу, и состояние флага будет контролироваться источником прерывания, а не аппаратными ресурсами системы, если внешний сигнал прерывания активен по уровню. Для прерываний, активных по срезу и уровню, флаги IE0 и IE1 должны очищаться программным обеспечением. Флаги TF0 и TF1 в регистре TCON выставляются в случае переполнения таймеров 0 и 1 соответственно и тоже являются источниками прерываний. Очищаются аппаратно после выполнения программы по обслуживанию прерывания. Источником прерывания также является таймер 2. В результате его переполнения, захвата или перезагрузки выставляется флаг TF2, а в случае появления внешнего сигнала на выводе T2EX – флаг EXF2. В случае выставления одного из этих флагов генерируется вектор прерывания, а после его обслуживания программное обеспечение должно очистить соответствующий флаг. Аппаратно эти флаги не очищаются. Сторожевой таймер может работать как системный смотритель или обычный таймер. В любом случае, по достижению счета таймера определенного значения выставляется флаг WDIF в регистре WDCON и, если прерывание от сторожевого таймера разрешено через бит EIE.4, то оно произойдет. Следующим источником прерываний является последовательный порт, который в составе блока последовательного интерфейса является единственным источником прерываний. Прерывания генерируются в момент получения или передачи данных, после того как будет выставлен соответствующий флаг RI или TI в регистре специального назначения SCON. Флаги очищаются программным обеспечением после обслуживания прерывания. Аппаратно флаги не очищаются. Внешний сигнал прерывания HPINT имеет самый высокий приоритет среди других прерываний. Его появление на соответствующем выводе микросхемы приводит к выставлению флага HPI в регистре WDCON. Прерывание произойдет, если оно разрешено через бит EHPI. Пользователь не может изменить уровень приоритета этого прерывания, но может разрешить или запретить его выполнение через бит EHPI. Глобальное управление всеми видами прерываний EA не влияет на разрешение или запрет этого прерывания. Поскольку стандартные флаги прерываний для семейства 8051, являясь причиной самих прерываний, могут быть программно установлены или сброшены, то прерывание может быть вызвано программным обеспечением. Дополнительные источники прерываний такие, как контроллер прямого доступа к памяти, блок JTAG интерфейса, условия программного и аппаратного останова, могут быть обеспечены только программным обеспечением. Индивидуально каждый вид прерывания может быть разрешен или запрещен через соответствующие биты в регистрах специального назначения IE и EIE. Все виды прерываний, за исключением высокоприоритетного прерывания HPI, могут быть одновременно запрещены, если очистить бит EA в регистре IE. Структура уровней приоритета Существуют три уровня приоритета для прерываний: самый высокий, высокий и низкий. Только сигнал HPI имеет самый высокий приоритет и не может быть прерван сигналами более низкого уровня. Тем не менее, все прерывания объединены в одной иерархии приоритетов, которую они предопределяют сами. Это распределение позволяет контроллеру прерываний разрешать проблему возникновения одновременных запросов с одинаковыми уровнями приоритета и разводить их во времени, избегая внутренних конфликтов. Иерархия приоритетов изначально предусмотрена по умолчанию и представлена в таблице 35. В ней все виды прерываний расположены в порядке убывания приоритетов и некоторые из них располагают индивидуальными битами приоритета, позволяющими назначить этот вид прерывания более высокого уровня. Прерывания, для которых по умолчанию предусмотрен высокий уровень приоритета, сохраняют за собой этот уровень. Флаги прерываний опрашиваются во втором такте каждого машинного цикла, и в этом же цикле опрашиваются все обозначенные источники прерываний и оценивается их уровень приоритета. В случае появления запроса на прерывание аппаратное обеспечение выполняет сгенерированную системой команду длинного перехода LCALL на соответствующий адрес векторного прерывания, но при следующих условиях: 1. если на данный момент не обслуживается прерывание равного или более высокого приоритета; 2. если текущий цикл опроса источников прерываний является последним машинным циклом выполняемой команды; 3. если текущая команда не включает в себя модификацию содержимого одного из регистров IP, IE, EIP или EIE и не является командой возврата из подпрограммы RETI. Для обслуживания прерывания обязательным является выполнение всех трех условий. Прерывание не может быть обслужено, если какое-то из условий не выполнятся на момент выставленного флага прерывания, и его сохранение в памяти не предусмотрено, для того, чтобы запустить процедуру обслуживания прерывания в момент выполнения всех трех условий, когда флаг уже будет снят. В каждом цикле опрос состояния флагов происходит заново. Иерархия приоритетов прерываний Таблица 35

Процессор выполняет команду перехода на адрес, по которому расположена подпрограмма обслуживания прерывания, в случае выставления флага этого прерывания. По окончании выполнения подпрограммы соответствующий флаг должен быть очищен. Это может произойти автоматически аппаратными средствами системы или требует затрат средств программного обеспечения в соответствии с таблицей 36. Флаги прерывания TF0 или TF1 таймеров 0 и 1 очищаются аппаратно после каждого выполнения подпрограммы обслуживания прерывания. Что касается внешних сигналов прерывания INTR0 и INTR1, то флаги очищаются аппаратно, только если сигналы активны по срезу. Прерывания от последовательного порта возникают в результате получения или передачи данных, поэтому требуются затраты программного обеспечения для предварительного определения вызвавшего прерывание флага и его очистку. Флаги прерывания таймера 2 и сторожевого таймера могут быть очищены только программным обеспечением. Аппаратно вызванная команда перехода LCALL действует аналогично команде LCALL программного обеспечения. При ее выполнении текущее значение счетчика команд сохраняется в стеке, но не сохраняется содержимое регистра слова состояния. Источники прерываний и метод сброса Таблица 36

Счетчик команд загружается новым значением адреса, на который указывает вектор прерывания согласно таблице 37. Для каждого источника прерывания предусмотрен индивидуальный адрес вектора прерывания, и адреса этих векторов распределены в памяти неравномерно. Подпрограмма обслуживания прерывания начинается с адреса, на который указывает вектор прерывания, и заканчивается командой RETI. После выполнения команды RETI процессор выгружает содержимое стека и, прежде всего, возвращает счетчику команд адрес, с которого была прервана основная программа, из вершины стека. Программным обеспечением должно быть предусмотрено восстановление содержимого необходимых регистров к моменту возвращения микроконтроллера к выполнению основной программы. Команда RET действует аналогично команде RETI, отличие состоит только в том, что команда RETI сообщает контроллеру прерываний о том, что процедура обслуживания прерывания окончена. Адреса векторов прерывания для различных источников Таблица 37

Внешние прерывания Существуют три источника внешних прерываний для процессора конфигурируемой системы на кристалле. Первый из них – сигнал HPINT с самым высоким уровнем приоритета. Он не может быть прерван другими сигналами и обычно используется как сигнал сбоя питания. Два других сигнала внешнего прерывания – INTR0 и INTR1. Эти сигналы могут быть запрограммированы по срезу или по уровню через биты IT0 и IT1 в регистре специального назначения TCON. ! Полярность сигналов INTR0 и INTR1 микроконтроллера стандарта 8051 отличается от полярности сигналов конфигурируемой системы на кристалле. В стандарте 8051 эти сигналы активны по спадающему фронту или низкому уровню, в то время как сигналы системы на кристалле, активны по нарастающему фронту или высокому уровню. Состояние сигналов INTR0 и INTR1 опрашивается в четвертом такте каждого машинного цикла. Если в одном цикле был зарегистрирован сигнал низкого уровня, а в другом – высокого, значит, сигнал прерывания активен по нарастающему фронту, и прерывание регистрируется флагом IE0 или IE1 в регистре TCON, в зависимости от источника. Поскольку один машинный цикл длится 4 такта, то необходимым условием для регистрации сигнала внешнего прерывания является его продолжительность. Таким образом, минимальная длительность сигнала внешнего прерывания, активного по срезу, составляет один полный машинный цикл. Достаточной длительностью этого сигнала считаются 5 тактов. Флаг IE0 или IE1 очищается автоматически после выполнения программы обслуживания прерывания. Для сигнала, активного по уровню, обязательным условием его регистрации является удержание высокого уровня сигнала на выводе микросхемы до тех пор, пока запрос на прерывание не будет обслужен. Флаг IE0 или IE1 не очищается автоматически и требует очистки из программного обеспечения. ! Внешние сигналы прерывания, активные по срезу, должны удерживать каждое из двух состояний на выводе микросхемы как минимум один машинный цикл. Достаточной длительностью считается время удержания сигнала в течение 5 тактов. Если сигнал внешнего прерывания не будет снят по окончании выполнения программы обслуживания прерывания, то процессор интерпретирует его как другой сигнал прерывания от того же источника. Время ответа на запрос от источника прерывания Реакция процессора на появление запроса от источника прерывания зависит от нескольких факторов: от природы самого прерывания, от команды, выполняемой на данный момент, от готовности системной шины. Флаги прерываний выставляются в третьем такте машинного цикла. Для внешних прерываний это флаги IE0 и IE1, для последовательного порта – флаги RI и TI, а для таймеров 0 и 1 – TF0 и TF1. Опрос этих флагов произойдет только в следующем машинном цикле, и, если запрос на прерывание останется активным в следующем цикле при выполненных трех условиях, то аппаратное обеспечение организует переход на соответствующий адрес векторного прерывания в следующем цикле. Команда длинного перехода выполняется за четыре машинных цикла. Таким образом, между моментом установки флага и началом выполнения подпрограммы обслуживания прерывания пройдет, как минимум, пять машинных циклов. Это время может оказаться и больше при следующих условиях: 1. если на данный момент обслуживается прерывание равного или более высокого приоритета; 2. если текущий цикл опроса источников прерываний не является последним машинным циклом выполняемой команды; 3. если текущая команда включает в себя модификацию содержимого одного из регистров IP, IE, EIP или EIE или является командой возврата из подпрограммы RETI. В первом случае время ответа на запрос зависит от времени выполнения подпрограммы обслуживания прерывания. Во втором случае время ответа увеличится из-за введения дополнительной временной задержки. Максимальное время ответа на запрос может возникнуть в третьем случае, а также при выполнении команд деления DIV и умножения MUL. В итоге, максимальное время ответа на запрос может занять 12 машинных циклов, которые будут состоять из следующих циклов: 1. один цикл для регистрации запроса на прерывание; 2. два цикла для завершения выполнения команды модификации одного из регистров IP, IE, EIP или EIE; 3. пять циклов для завершения команды деления или умножения; 4. четыре цикла для выполнения команды длинного перехода LCALL. Согласно таблице 38, время ответа на запрос в конфигурируемой системе может быть в пределах от 5 до 12 машинных циклов, что в переводе на такты составит от 20 до 48 тактов. Для микроконтроллера стандарта 8051 максимальное время ответа на поступивший запрос от источника прерывания составляет 8 машинных циклов или 96 тактов, что в 2 раза медленнее, чем для ускоренного микроконтроллера компании Trisend. Время ответа на запрос для конфигурируемой системы Таблица 38

Условия системного сброса Существует несколько источников системного сброса, и все они воздействуют на систему на кристалле по-разному. Типы системного сброса и их воздействие на устройства Таблица 39

Например, сброс системы при включении питания приводит к сбросу всех функциональных устройств, включая ускоренный 8051 микроконтроллер, периферию, подключенную к внутренней системной шине, регистры (блок конфигурирующих регистров), систему тактирования и блок JTAG – интерфейса. В другом случае, появление сигнала на выводе RST приведет к сбросу большинства устройств, но при этом состояние регистров системы тактирования и JTAG – интерфейса останется неизменным. И, наконец, сброс, вызванный сторожевым таймером или прикладным сигналом RSTC, подействует только на микроконтроллер, оставив другую системную логику неизменной. Таблица 39 объединила в себе перечень возможных видов сбросов и их воздействие на функциональные устройства системы. Также, в таблице показано поведение устройств после сброса: одни заново инициализируются и перезапускают выполнение кодов с адреса 0000Н, другие только перезапускают выполнение кодов. Сброс системы после включения питания Встроенные на кристалле аналоговые цепи постоянно следят за уровнем питания VCC, фиксируя любые его изменения: скачки и провалы. До тех пор, пока уровень питания VCC будет находиться ниже допустимого порогового значения VRST, аналоговые цепи будут удерживать устройство в состоянии сброса. Как только питание превысит пороговый уровень, система перейдет в нормальный режим работы. При этом логический блок системы произведет очередной ее сброс, в результате которого произойдет сброс всех возможных ресурсов устройства. Это состояние будет удерживаться два такта, пока не станет доступным генератор тактовых импульсов. После сброса системы при включении питания установится флаг POR, который должен быть в последствии очищен программным обеспечением. Иначе окажется невозможным корректное определение будущих источников системного сброса. В случае провала питания, то есть занижения его уровня ниже порогового VRST, устройство снова войдет в состояние сброса, а как только питание достигнет надлежащего действующего уровня, произойдет очередной сброс системы, и снова выставится флаг POR. Сигнал сброса - RST Появившийся на выводе RST сигнал низкого уровня приведет к сбросу всех внутренних ресурсов, исключая контрольные регистры системы тактирования и JTAG – интерфейс. Система может быть сброшена сигналом RST в любой момент времени, но выход ее из этого состояния будет автоматически синхронизирован тактовым сигналом BCLK. Специальный фильтр предотвращает ошибочное восприятие сигнала сброса, удерживаемого на выводе RST менее 2 нс. Главное требование к сигналу является его длительность, которая не должна быть менее 8 нс. Сигнал на выводе RST может игнорироваться в двух случаях: 1. если система на кристалле введена в безопасный режим, и при этом установлен бит MIU (SECURITY.0) в регистре SECURITY; 2. если в процессе отладки через JTAG – интерфейс системе была передана команда FORCE_NOBRST, при этом команда должна удерживаться определенное время, чтобы быть функционально действующей. Сброс через JTAG – интерфейс В целях отладки блок JTAG – интерфейса может вызвать сброс системы или микроконтроллера. Существуют три взаимосвязанные команды, которые используются для этих целей и могут быть переданы системе на кристалле через JTAG-интерфейс: 1. J_RESET – сброс микроконтроллера; 2. FORCE_BRST – сброс всех узлов системы кроме сторожевого таймера, контрольных регистров системы тактирования и JTAG – интерфейса; 3. FORCE_NOBRST – блокировка вывода RST от сигналов возможного сброса. Эта команда превосходит предыдущую команду по функциональному значению. Дополнительный сброс системы через сигнал RSTC RSTC – входной сигнал сброса, активный по высокому уровню. После его появления произойдет сброс только микроконтроллера, а периферия и другие системные ресурсы останутся в активном состоянии. Что касается сторожевого таймера, то его положение до сброса сохранится и после, но с некоторыми изменениями. Обычно сигнал RSTC генерируется функциями логической матрицей либо поступает от разрядов портов ввода/вывода. Сброс, вызванный сторожевым таймером Сторожевой таймер используется микроконтроллером в основном в качестве системного смотрителя, сопровождающего выполнение определенных системных операций. Является свободно запускаемым таймером с программируемыми интервалами времени блокировки. Программное обеспечение пользователя может его сбросить и перезапустить в любой момент времени. По достижению таймером заданной границы устанавливается флаг прерывания. Если сброс от сторожевого таймера разрешен, то он вызывается им при следующих условиях: 1. бит EWT (WDCON.1) установлен; 2. таймер достиг заданного блокировочного значения; 3. бит RWT (WDCON.0) не был установлен программным обеспечением в течение 512 тактов после достижения блокировочного значения. Сброс, вызванный сторожевым таймером, повлияет только на работу микроконтроллера. Условия сброса поддерживаются аппаратно в течение двух машинных циклов. Поведение системы после сброса В зависимости от того, каким образом был вызван сброс, система может повести себя по-разному: либо произвести реконфигурацию и перезапуск выполнения кодов, либо только перезапуск. Реконфигурация Некоторые виды сброса, как показано в таблице 39, могут спровоцировать систему на кристалле к запуску или перезапуску процесса конфигурации, обычно длящемуся от 10 до нескольких сотен миллисекунд, в зависимости от генератора тактовых сигналов и действующего режима. После окончания процесса конфигурации пользовательские программы начинают свое выполнение с адреса 0000Н. Перезапуск выполнения кодов После сброса микроконтроллера, пользовательская программа возвращается к выполнению с адреса 0000Н. В этом случае никакой речи о реконфигурации не идёт. Микроконтроллер в состоянии сброса Большинство регистров специального назначения и регистры общего назначения при сбросе теряют свои значения и обнуляются. Счетчик команд также сбрасывается и удерживает значение 0000h до тех пор, пока сохраняется условие сброса. Между тем, данные в ОЗУ сохраняются на протяжении всего времени пребывания системы в этом состоянии. Стековый указатель принимает значение 07h, а данные в стековой памяти теряются. Содержимое ОЗУ тоже может быть утеряно, если уровень питания упадет ниже 2 вольт, поскольку это минимальный уровень требуемого питания для нормальной работы оперативной памяти. Поэтому после первого сброса системы при включении питания, данные ОЗУ будут считаться неопределенными. А при дальнейшем сбое питания, когда его уровень не будет превышать 2-х вольт, данные будут потеряны. Содержимое регистров после системного сброса отображено в таблице 40. Таймеры и прерывания при этом запрещены. После сброса при включении питания сторожевой таймер становится неактивным. Биты его контрольного регистра WDCON устанавливаются и очищаются в зависимости от источника сброса, как показано в таблице 41. Символом ‘х’ обозначены биты, значения которых не изменяются. Бит WDCON.6 устанавливается только при сбросе после включения питания, а WDCON.4 – при снижении уровня питания ниже порогового. Бит WDCON.2 устанавливается, когда сброс организован сторожевым таймером, и очищается при сбросе системы после включения питания. Бит EWT (WDCON.1) также очищается при сбросе питания и не изменяется при сбросе, вызванном сторожевым таймером или внешним сигналом. Содержимое регистров SFR после сброса Таблица 40

Значения контрольного регистра WDCON сторожевого таймера при сбросе от различных источников Таблица 41

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 451; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 216.73.216.119 (0.014 с.) |