Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Конфигурируемая система на кристалле E5 компании TriscendСодержание книги

Поиск на нашем сайте

Конфигурируемая система на кристалле (CSoC) семейства E5 компании Triscend Основные аппаратные блоки семейства Е5 2.1. «Ускоренный» 8051 микроконтроллер Конфигурируемая система на кристалле Е5 является полностью совместимой с промышленными стандартами 8051/8052 и поддерживает их полный перечень команд. Содержит ресурсы стандартного 8051 микроконтроллера, включая три таймера/счетчика, дуплексный последовательный порт и 12 источников прерывания с тремя уровнями приоритета. Особенность системы на кристалле Е5 – это высокопроизводительный 8–разрядный микроконтроллер с реконфигурируемым процессором, который обеспечивает выполнение машинного цикла за 4 такта (для большинства команд) в отличие от микроконтроллера стандарта 8051, который реализует 12 тактовые машинные циклы. Таким образом, производительность Е5 превосходит в 1,5 – 3 раза. Система на кристалле Е5 обеспечивает наибольшую скорость выполнения команд даже при использовании того же резонатора, что и 8051, а также способна функционировать от низкочастотного резонатора с сохранением высокой производительности, что способствует уменьшению энергопотребления. Конфигурируемая система имеет в распоряжении двойной указатель данных, удобный для передачи данных блоками. Программируемые порты ввода/вывода В распоряжении стандартного 8051 микроконтроллера имеются четыре 8-разрядных порта ввода/вывода, что составляет 32 линии. На кристалле Е5 процессор реализован с расширенными функциональными возможностями, поэтому реально его подключение к стольким разрядам портов ввода/вывода, сколько того запрашивают приложения. Асинхронный интерфейс (UART) Последовательный порт конфигурируемой системы представляет собой улучшенную модель UART 8051 (при сохранении временной совместимости). UART в Е5 имеет следующие особенности: автоматическое распознавание адреса и обнаружение кадровых ошибок. Таймеры В распоряжении микроконтроллера на кристалле Е5 имеются три 16-разрядных таймера, которые функционируют аналогично таймерам стандартного 8051. В режиме таймера производиться подсчет каждых 4-х или 12-ти тактов, что дает возможность функционирования аналогично стандартному 8051 микроконтроллеру. Дополнительный сторожевой таймер используется как системный смотритель или таймер, программируемый на большие интервалы времени. Прерывания Структура прерываний системы на кристалле Е5 практически не отличается от структуры прерываний стандартного 8051 микроконтроллера, за исключением того, что источников и векторов прерываний больше, ввиду расширенных возможностей и периферии. Указатель данных Микроконтроллер стандарта 8051 имеет только один 16-ти битный указатель данных, а Е5 – два за счет дополнительного указателя DPTR (DPL1, DPH1), который занимает два ранее не используемых стандартом 8051 регистра специального назначения (PCH). Управление энергопотреблением Как и 8051, Е5 допускает работу в двух возможных режимах – холостой и энергосберегающий (power-down). В холостом режиме работа микроконтроллера прекращается, в то время как счетчики, последовательный порт и блок прерываний продолжают действовать. Энергосберегающий режим не прерывает работу микросхемы, а лишь вводить ее в режим самого низкого энергопотребления. Сброс при включения питания Конфигурируемая система на кристалле имеет возможность организации системного сброса при включении питания. Это исключает необходимость во внешних емкостно-резистивных связях, которые обязательны для микроконтроллера стандарта 8051. Контроллер прямого доступа к памяти (DMA) Контроллер DMA содержит два независимых канала, по которым осуществляется передача данных со скоростью один байт за такт. Каждый канал автономен и не нуждается в поддержке процессора. Существует несколько режимов передачи данных, как, например, между памятью и устройством в любом направлении. Внешнее устройство самостоятельно связывается с определенным каналом DMA через контрольный регистр DMACTRL, который содержит в себе бит запроса и бит подтверждения. Два канала DMA могут использоваться в паре для обмена данными между различными участками памяти. Главные особенности DMA контроллера: 1) Два независимых канала для передачи данных в любом направлении; 2) Скорость передачи данных достигает 40 Мбайт в секунду; 3) Авто-инициализация каналов; 4) Программируемые параметры передачи данных; 5) Наличие нескольких способов адресации; 6) Возможность прерываний; 7) Возможность обмена данными между различными участками памяти; 8) Возможность поблочной передачи данных; 9) Обслуживание запросов программного обеспечения; 10) Наличие четырехбайтной области FIFO; 11) Асинхронность сигналов запрос, подтверждение; 12) Сопровождение передачи данных по DMA каналу подсчетом циклической контрольной суммы.

Рис.2. Блок-схема DMA контроллера

Функциональное описание Блочная структура DMA каналов представлена на рис.2. Заданный набор параметров определяет режим работы для каждого DMA канала в отдельности и включает в себя стартовый адрес размещения данных в памяти, начальный счет передачи, направление передачи и другие параметры. Каждый канал имеет свой набор регистров. Блок логического контроля состоит из адресного счетчика, счетчика передачи, счетчика ожидаемых запросов и логики контроля над каналами. Область FIFO служит временным буфером между входным/выходным устройством и памятью. Каждый канал DMA интерпретируется системной магистралью как независимый мастер. Инициализация и прекращение прямого доступа к памяти Управлять процессом передачи данных по каналу DMA можно через специальные программируемые регистры. После того, как параметры передачи будут программно определены, для активизации канала необходимо установить бит EN в соответствующем регистре DMA_CTRLх_0. Бит EN является битом разрешения для приема запросов на прямой доступ к памяти. Для того, чтобы запросы обслуживались, необходимо установить бит INIT в том же регистре DMA_CTRLх_0. После инициализации, с первым запросом предварительно заданные значения стартового адреса и начального счета передачи загрузятся в их соответствующие регистры. После чего бит INIT аппаратно очистится, и контроллер DMA приступит к обслуживанию запроса. Следующие параметры передачи могут быть обновлены и бит INIT заново установлен. Сигнал запроса длится один такт. Запросы более одного такта интерпретируются как многократные. В случае, когда DMA контроллер не успевает обслуживать все входящие запросы, специальный счетчик ожидаемых запросов сохраняет их количество. Всего, возможно, сохранить до 64 Кбайт запросов (65535). Если в процессе передачи блока данных бит EN окажется сброшенным, то последующие запросы будут игнорироваться как DMA контроллером, так и счетчиком ожидаемых запросов. Значения счетчиков могут быть считаны программным обеспечением. Очистка регистров производиться установкой бита CRL или при активизации канала (EN=1). В случае нестабильной работы канала его можно повторно инициализировать, установив бит CRL в контрольном регистре. Очистка бита позволит снова использовать канал для передачи данных. Бит CRL устанавливается после системного сброса или сброса при включении питания. Передача блока данных считается завершенной, если счетчик передачи достигнет нуля. В таком случае, в зависимости от режима работы DMA канала, процесс передачи данных либо прекратится, либо продолжится. DMA контроллер продолжит передачу данных, если бит INIT был повторно установлен или активизирован режим непрерывной передачи. Если канал DMA окажется сброшенным, то передача блока данных прекратится. Прекращение прямого доступа к памяти. Пользователь может прекратить прямой доступ к памяти в любой момент времени, очистив бит EN (EN=0), а затем установив бит CLR. Для сброса логики канала DMA необходим всего один такт. После очистки бита CLR, канал DMA будет опять готов к использованию. При этом значения конфигурирующих регистров останутся неизменными, за исключением нескольких функциональных битов, которые будут утеряны после сброса логики канала. Установив несколько командных битов в контрольном регистре, можно будет повторить предыдущую передачу. Процесс обмена данными DMA контроллер всегда сначала считывает данные и сохраняет их во временном буфере FIFO, откуда данные потом следуют на запись. Способы передачи данных Конфигурируемая система на кристалле поддерживает несколько способов передачи данных в режиме прямого доступа к памяти. Их описание и особенности приведены ниже. 1. Режим передачи одного байта данных. В этом режиме с каждым запросом передается только один байт данных. Если запросы поступают в течение каждого машинного цикла, то контроллер DMA будет обслуживать их так быстро, как сможет, и до тех пор, пока счетчик передачи не достигнет нуля, после чего передача данных прекратится. Этот режим предусмотрен по умолчанию. 2. Режим передачи блока данных. В этом режиме с каждым запросом передается целый блок данных. После получения запроса DMA контроллер приступает к процессу передачи данных, который будет длиться до тех пор, пока счетчик передачи не достигнет нуля. Если в какой-то момент времени в процессе передачи блока данных поступит новый запрос, то он запишется в счетчик ожидаемых запросов, и будет обслужен по окончании текущей передачи блока данных. 3. Запросы, реализуемые программным обеспечением. В этом режиме контроллер DMA обслуживает запросы, поступающие от программного обеспечения. Разрешение этого режима осуществляется установкой бита SFTREQ в контрольном регистре канала DMA. Запросы, которые не могут быть обслужены на текущий момент, записываются в счетчик ожидаемых запросов. Если запрос поступил в момент неактивного состояния канала DMA, то он игнорируется. 4. Одиночная инициализация. Осуществляется установкой бита INIT. После получения первого запроса бит INIT аппаратно очищается, и передача данных осуществляется до тех пор, пока счетчик передачи не достигнет значения нуля. После этого контроллер DMA будет ожидать новой команды по обслуживанию запроса на прямой доступ к памяти. 5. Непрерывная инициализация. Осуществляется установкой бита CONT. Аналогично биту INIT, бит CONT автоматически инициализирует следующую передачу данных, как если бы заново был установлен, бит INIT. 6. Обмен данными между различными областями памяти. Этот режим возможен при использовании обоих каналов одновременно. Канал, по которому происходит считывание данных из памяти, является мастером, или ведущим; канал, по которому происходит запись данных в память – подчиненным, или ведомым. Для активизации режима необходимо в контрольных регистрах обоих каналов установить бит PAIR. Передача инициализируется через контрольный регистр ведущего канала, но при этом ведомый канал должен быть активизирован, и параметры передачи в его регистрах установлены должным образом. 7. Непрерывная поблочная передача данных. Этот режим возможно осуществить только с использованием одиночной инициализации. Параметры первого блока передаваемых данных загружаются в соответствующие контрольные регистры, и передача осуществляется после установки битов INIT и SFTREQ. После аппаратной очистки бита INIT (значит, канал приступил к передаче данных), программное обеспечение загружает адрес и счет передачи следующего блока данных. После загрузки этих параметров, программно устанавливаются биты INIT и SFTREQ. После завершения передачи первого блока данных, DMA канал загружает новые параметры и инициализирует новую передачу. Программное обеспечение будет повторять предыдущие шаги до тех пор, пока “список” всех передаваемых блоков данных не подойдет к концу. Адресное распределение в памяти Канал DMA генерирует в памяти адрес для каждого запроса. Первый адрес передачи блока данных – это стартовый адрес, который хранится в контрольном регистре начального адреса размещения данных в памяти. После первого запроса этот адрес загружается в счетчик текущего адреса, значение которого будет обновляться с каждым следующим запросом. Режимы адресации конфигурируются двумя битами контрольного регистра DMA канала (см. табл.2) В целях отладки программы, значения счетчика текущего адреса данных в блоке и счетчика текущей передачи доступны программному обеспечению. Область FIFO Служит временным буфером между запрашивающим DMA входным/выходным устройством и памятью. Наличие четырехбайтной области FIFO необходимо из-за структуры системной шины и возможности реализации режима Multi-мастера. Циклический подсчет контрольной суммы (ЦПКС) Циклический подсчет контрольной суммы может быть осуществлен для одиночного потока данных. Логика ЦКПС отслеживает данные, поступающие с шины в область FIFO; разделена между двумя каналами DMA и становится активной только для того, в контрольном регистре которого установлен бит CRC_EN. При изменении значения бита CRC_EN с 0 на 1 произойдет сброс регистра ЦПКС. Подсчет контрольной суммы – подсчет каждого бита, записываемого в FIFO. По окончании передачи, значение регистра может быть считано для сравнения с ожидаемым значением. Логика ЦПКС использует 16-разрядный полиномный делитель CRC-CCITT (см. формулу 2.1), который позволяет определить любой один, два или четное число ошибочных битов. Х16+Х12+X5+1 (2.1) Прерывания DMA контроллер может организовывать прерывания в следующих трех случаях: 1. По окончании передачи блока данных, когда счетчик передачи достигнет нулевого значения; 2. После первого запроса на передачу блока данных, когда установится бит INIT; 3. В случае переполнения счетчика ожидаемых запросов, когда DMA контроллер будет не в состоянии больше сохранять поступающие запросы. Статус любого из вышеуказанных прерываний отмечается в регистре состояния прерываний, независимо от разрешающих эти прерывания битов. Биты состояния сбрасываются программным обеспечением путем записи в них логической единицы. Запись нуля не имеет функционального значения. Некоторые биты состояния могут быть очищены также некоторыми аппаратными действиями (см. регистр прерываний DMA). Конфигурирующие регистры Каждый канал имеет набор из 21 байта контрольных регистров и регистров состояния. Некоторые регистры используются для программирования выбранного DMA канала и проверки его состояния. Регистр начального адреса (один на канал) Набор регистров определяет стартовый адрес передачи данных. К началу передачи значение загружается в адресный счетчик. DMA контроллер оперирует с 32-разрядными физическими адресами, в то время как микроконтроллер - с 16-битными логическими. Физический адрес автоматически определяется системой Triscend и представлен в заголовочном файле для пользователя. Регистры доступны для чтения и записи. Канал 0: Регистр начального адреса DMA канала 0 (А[7:0])

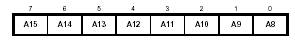

Мнемоника: DMASADR0_0 Адрес:FF20H Регистр начального адреса DMA канала 0 (А[15:8])

Мнемоника: DMASADR0_1 Адрес: FF21Н Регистр начального адреса DMA канала 0 (А[23:16])

Мнемоника: DMASADR0_2 Адрес: FF22Н Регистр начального адреса DMA канала 0 (А[31:24])

Мнемоника: DMASADR0_3 Адрес: FF23Н Канал 1: Регистр начального адреса DMA канала 1 (А[7:0])

Мнемоника: DMASADR1_0 Адрес:FF34H Регистр начального адреса DMA канала 1 (А[15:8])

Мнемоника: DMASADR1_1 Адрес: FF35Н Регистр начального адреса DMA канала 1 (А[23:16])

Мнемоника: DMASADR1_2 Адрес: FF36Н Регистр начального адреса DMA канала 1 (А[31:24])

Мнемоника: DMASADR1_3 Адрес: FF37Н Счетчик передачи (один на канал) Этот регистр содержит количество байтов данных предназначенных для передачи. Действительное значение регистра – число байтов минус один, так как значение загружается в счетчик прежде, чем начинается сама передача. Регистры доступны для чтения и записи. Канал 0: Счетчик передачи DMA канала 0 (CNT[7:0])

Мнемоника: DMASCNT0_0 Адрес: FF24Н Счетчик передачи DMA канала 0 (CNT[15:8])

Мнемоника: DMASCNT0_1 Адрес: FF25Н Счетчик передачи DMA канала 0 (CNT[23:16])

Мнемоника: DMASCNT0_2 Адрес: FF26Н Канал 1: Счетчик передачи DMA канала 1 (CNT[7:0])

Мнемоника: DMASCNT1_0 Адрес: FF38Н Счетчик передачи DMA канала 1 (CNT[15:8])

Мнемоника: DMASCNT1_1 Адрес: FF39Н Счетчик передачи DMA канала 1 (CNT[23:16])

Мнемоника: DMASCNT1_2 Адрес: FF40Н Регистр текущего адреса передачи данных (один на канал) Этот регистр используется для отслеживания текущего состояния определенного канала или при отладке. Первоначально содержит значение регистра начального адреса, которое загружается перед началом передачи. Затем происходит инкремент или декремент содержимого с каждым переносимым байтом, в зависимости от битов ADRM1 и ADRM0, определяющих режим адресации. Регистры доступны только для чтения. Канал 0: Текущий адрес DMA канала 0 (A[7:0])

Мнемоника: DMACADR0_0 Адрес: FF2BН Текущий адрес DMA канала 0 (A[15:8])

Мнемоника: DMACADR0_1 Адрес: FF2СН Текущий адрес DMA канала 0 (A[23:16])

Мнемоника: DMACADR0_2 Адрес: FF2DН Текущий адрес DMA канала 0 (A[31:24])

Мнемоника: DMACADR0_3 Адрес: FF2ЕН Канал 1: Текущий адрес DMA канала 1 (A[7:0])

Мнемоника: DMACADR1_0 Адрес: FF3FН Текущий адрес DMA канала 1 (A[15:8])

Мнемоника: DMACADR1_1 Адрес: FF40Н Текущий адрес DMA канала 1 (A[23:16])

Мнемоника: DMACADR1_2 Адрес: FF41Н Текущий адрес DMA канала 1 (A[31:24])

Мнемоника: DMACADR1_3 Адрес: FF42Н Счетчик текущего значения передачи (один на канал) Первоначально содержит значение счетчика передачи. Отображает количество переданных байтов данных. Регистры доступны только для чтения. Канал 0: Текущий счет DMA нулевого канала (CNT[7:0])

Мнемоника: DMACCNT0_0 Адрес: FF2FН Текущий счет DMA нулевого канала (CNT[15:8])

Мнемоника: DMACCNT0_1 Адрес: FF30Н Текущий счет DMA нулевого канала (CNT[23:16])

Мнемоника: DMACCNT0_2 Адрес: FF31Н Канал 1: Текущий счет DMA первого канала (CNT[7:0])

Мнемоника: DMACCNT1_0 Адрес: FF43Н Текущий счет DMA первого канала (CNT[15:8])

Мнемоника: DMACCNT1_1 Адрес: FF44Н Текущий счет DMA первого канала (CNT[23:16])

Мнемоника: DMACCNT1_2 Адрес: FF45Н

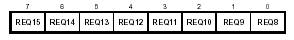

Контрольный регистр прямого доступа к памяти (один на канал) Канал 0:

Мнемоника: DMACTRL0_0 Адрес: FF27Н

Мнемоника: DMACTRL0_1 Адрес: FF28Н Канал 1:

Мнемоника: DMACTRL1_0 Адрес: FF3BН

Мнемоника: DMACTRL1_1 Адрес: FF3CН

Регистры доступны для чтения и записи. Бит CLR отвечает за сброс логики канала DMA. Когда бит CLR=1, произойдет сброс счетчика передачи и счетчика ожидаемых запросов, после чего канал перейдет в неактивное состояние. После очистки бита CLR, канал DMA будет опять готов к использованию. Очищается сбросом. Бит EN – бит разрешения приема запросов для канала. Когда бит EN=1, счетчик ожидаемых запросов очистится, и канал DMA будет готов принимать запросы. Когда EN=0, все входящие запросы будут игнорироваться. Очищается сбросом. Бит INIT – бит инициализации процесса передачи данных. Установка обязательна для передачи каждого блока данных. Когда INIT=1, в начале процесса передачи первоначальные данные загрузятся в их соответствующие регистры, после чего бит INIT аппаратно очистится. Программное обеспечение может установить бит INIT снова в процессе текущей передачи, чтобы подготовить канал к следующему блоку данных. Очистка бита приведет к тому, что процесс передачи данных прекратиться после завершения текущей передачи. Очищается сбросом. Бит CONT – бит режима непрерывной инициализации. Когда CONT=1, передача данных будет осуществляться до тех пор, пока бит не будет очищен. Очистка бита производится сбросом. Бит SFTREQ – бит запроса на прямой доступ к памяти от программного обеспечения. Очищается аппаратно в течение следующего такта. Бит BLOCK – бит передачи блока данных, вызываемой одиночным запросом. Когда бит установлен, организуется передача целого блока данных. Сбросом не очищается. Бит PAIR – бит режима обмена данными между различными областями памяти. Должен быть установлен в регистрах обоих каналов. Сбросом не очищается. Бит W/R – бит определения направления данных при передаче. Если W/R=1, то производится запись из памяти в устройство, если W/R=0 – чтение данных из устройства. Сбросом не очищается. Биты ADRM0 и ADRM1 определяют режим адресации, как показано в таблице 2. Сбросом не очищаются.

Настройки режима адресации DMA Таблица 2

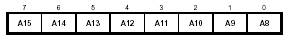

Бит CRC_EN разрешает циклический подсчет контрольной суммы. Когда CRC_EN=1, активизируется логика подсчета. В момент установки бита, а именно, в момент перехода 0-1, логика подсчета контрольной суммы сбрасывается в ноль. Все биты очищаются после сброса системы при включении питания или других системных сбросах. Регистр ожидаемых запросов (один на канал) Регистр содержит число запросов DMA, ожидающих обслуживание. Максимальное число запросов 64 Кбайта. Регистр очищается после сброса при включении питания и других аппаратных сбросов. Регистр доступен только для чтения. Канал 0: Регистр ожидаемых запросов канала 0 (REQ[7:0])

Мнемоника: DMAPREQ0_0 Адрес: FF32Н Регистр ожидаемых запросов канала 0 (REQ[15:8])

Мнемоника: DMAPREQ0_1 Адрес: FF33Н Канал 1: Регистр ожидаемых запросов канала 1 (REQ[7:0])

Мнемоника: DMAPREQ1_0 Адрес: FF46Н Регистр ожидаемых запросов канала 1 (REQ[15:8])

Мнемоника: DMAPREQ1_1 Адрес: FF47Н Регистр прерываний (один на канал) Регистр разрешает один из трех видов прерывания для каждого канала в отдельности. Регистры доступны для чтения и записи. Канал 0:

Мнемоника: DMAEINT0 Адрес: FF29Н Канал 1:

Мнемоника: DMAEINT1 Адрес: FF3DН Бит TC_EN=1 разрешает прерывание, если счетчик передачи достигнет своего конечного значения. Бит INIT_EN =1 разрешает прерывание после инициализации передачи. Бит OVR_EN=1 разрешает прерывание в случае переполнения регистра ожидаемых запросов. Биты очищаются после сброса системы при включении питания или других системных сбросах. Регистр состояния (один на канал) Канал 0:

Мнемоника: DMAINT0 Адрес: FF2AН Канал 1:

Мнемоника: DMAINT1 Адрес: FF3ЕН Регистр состояния содержит флаги прерываний для контроллера DMA. Флаг TC устанавливается, когда счетчик передачи достигает своего конечного значения. Устанавливается аппаратно и очищается программным обеспечением, путем записи в ТС значения логической единицы. Также очищается, когда бит INIT устанавливается в соответствующем контрольном регистре DMA канала программным обеспечением. Флаг INIT устанавливается, когда происходит инициализация процесса передачи данных. Устанавливается аппаратно и очищается программным обеспечением, путем записи в INIT значения логической единицы. Также очищается, когда бит INIT устанавливается в соответствующем контрольном регистре DMA канала программным обеспечением. Флаг OVR устанавливается, когда происходит переполнение счетчика ожидаемых запросов. Устанавливается аппаратно и очищается программным обеспечением, путем записи в OVR значения логической единицы. Также очищается, когда происходит сброс счетчика ожидаемых запросов в соответствующем контрольном регистре DMA канала. ! Флаги OVR, INIT, TC в регистре состояния очищаются путем записи в них логической “1”. Запись логического “0” не имеет функциональной значимости. Биты очищаются после сброса системы при включении питания или других системных сбросах. Регистр циклического подсчета контрольной суммы (один на 2 канала) После завершения процесса передачи данных значение регистра может быть считано программным обеспечением для сравнения с ожидаемым значением. Очищается после сброса системы при включении питания или других системных сбросах.

Регистр подсчета контрольной суммы (CRC[7:0])

Мнемоника: DMACRC_0 Адрес: FF48Н Регистр подсчета контрольной суммы (CRC[15:8])

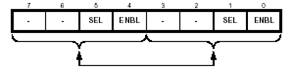

Мнемоника: DMACRC_1 Адрес: FF49Н Взаимодействие периферии, реализованной в логической матрице, с DMA контроллером Устройство, реализованное в конфигурируемой логической матрице, полностью располагает ресурсами прямого доступа к памяти. Доступ обеспечивается через распределяющий контрольный регистр DMA, который направляет сигнал запроса от периферии к соответствующему DMA каналу и возвращает сигнал подтверждения от соответствующего DMA канала обратно периферии, как показано на рис.3.

Рис.3. Контрольные регистры отвечают за распределение сигналов между программным модулем логической матрицы и каналами DMA Распределяющий контрольный регистр DMA является одной из функций программируемого адресного селектора, который исполняет также функции адресного дешифратора и чип селектора. Адрес регистра программируется и является одним и тем же для любых функций, использующих селектор. Символический адрес назначается в процессе проектирования, а действительный – программной средой FastChip. Все контрольные регистры DMA 8-разрядные и должны быть расположены либо в памяти данных, либо в памяти регистров специального назначения (SFR). Индивидуальные контрольные регистры каналов DMA определяют направление передачи данных, а именно, процесс чтения их из устройства в память или записи из памяти в устройство. Поскольку распределяющий контрольный регистр может связываться только с одним каналом DMA через бит SEL, то для процессов чтения и записи данных требуются два таких регистра. Также, распределяющий регистр разрешает либо запрещает обращение программного модуля, реализованного в логической матрице, к каналам DMA через биты ENBL. Распределяющий контрольный регистр Адрес и имя регистра определяются пользователем. Неиспользуемые биты при чтении возвращают значение логического нуля.

Две тетрады дублируют друг друга ! Две дублирующие друг друга тетрады необходимы для определения действительного значения битов разрешения и выбора канала, для чего значения тетрад логически складываются. Одинаковые значения должны быть занесены в обе тетрады, но только одна из них будет взаимодействовать с шиной данных. Бит SEL – бит выбора канала DMA. Когда SEL=1, то программный модуль в логической матрице будет взаимодействовать с каналом 0, когда SEL=1 – с каналом 1. Бит занимает позиции 1 и 5, при чтении значения битов складываются. Бит ENBL – бит разрешения программному модулю обращаться к контроллеру прямого доступа к памяти. В случае, когда ENBL=0, контроллер DMA будет игнорировать запросы. Бит занимает позиции 0 и 4, при чтении значения битов складываются. После сброса регистр загружается значением 00h. Обладает неограниченным доступом для записи и чтения. Сигнал запроса REQSEL Устройство, реализованное в логической, матрице направляет сигнал запроса REQSEL к контрольному регистру, как показано на рис.4. Если бит ENBL установлен, то сигнал проходит дальше по DMA каналу, определяемому битом SEL (см. распределяющий контрольный регистр DMA).

Рис.4. Контрольный регистр направляет запросы соответствующему каналу Сигнал подтверждения ACKSEL DMA канал после получения запроса на прямой доступ к памяти запрашивает системную шину и устанавливает сигнал подтверждения ACKSEL, направленный к запрашивающему устройству. Логика процесса показана на рис.5.

Рис.5. DMA канал устанавливает сигнал подтверждения, направленный к запрашивающему устройству Когда ACKSEL=1, контроллер выражает готовность к обмену. С момента получения сигнала ACKSEL устройство, реализованное в логической матрице, должно либо выставить данные на шину, либо их считать. Поскольку DMA контроллер спроектирован на максимальную скорость передачи данных, то запрашивающее устройство должно быть готовым получить подтверждение в течение такта сразу после того, как был отправлен запрос. Пример процесса записи данных во внешнее устройство На рис.6. представлена диаграмма процесса записи данных из памяти во внешнее устройство. При этом один из каналов настроен на запись, а распределяющий регистр содержит значение, разрешающее прием запросов от программного модуля и определяющее рабочий канал.

Рис.6. Временная диаграмма записи данных

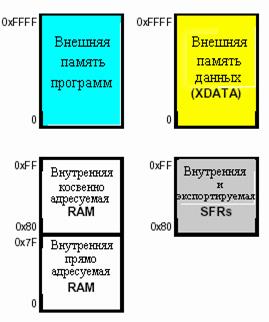

На диаграмме указаны следующие позиции: 1. устройство выставляет сигнал запроса для соответствующего DMA канала; 2. организация временной задержки, подготовка шины данных; 3. DMA контроллер предоставляет адрес передачи и данные и выставляет сигнал подтверждения, который затем поступает в устройство. По этому сигналу устройство активизирует регистр и считывает данные с шины. Использование DMA контроллера как промежуточного мастера Поскольку устройство, реализованное в логической матрице, не может самостоятельно запрашивать и контролировать шину данных, поэтому использует контроллер DMA в качестве промежуточного мастера. При этом DMA контроллер снабжен встроенной логикой, позволяющей связываться с арбитром на системной шине, отслеживать адреса и контролировать процесс обмена данными, не используя ресурсы логической матрицы. Адресные координаторы Адресные координаторы преобразуют адреса, по которым микроконтроллер обращается к памяти программ, данных и регистрам специального назначения (SFR), в адреса, допустимые на системной шине системы на кристалле Е5 компании Trisend. Микроконтроллер 8051 поддерживает следующие адресные пространства: внешняя память программ, внешняя память данных, внутренняя прямо адресуемая память, внутренняя косвенно-адресуемая память, внутренняя экспортируемая область регистров специального назначения, как показано на рис.32.

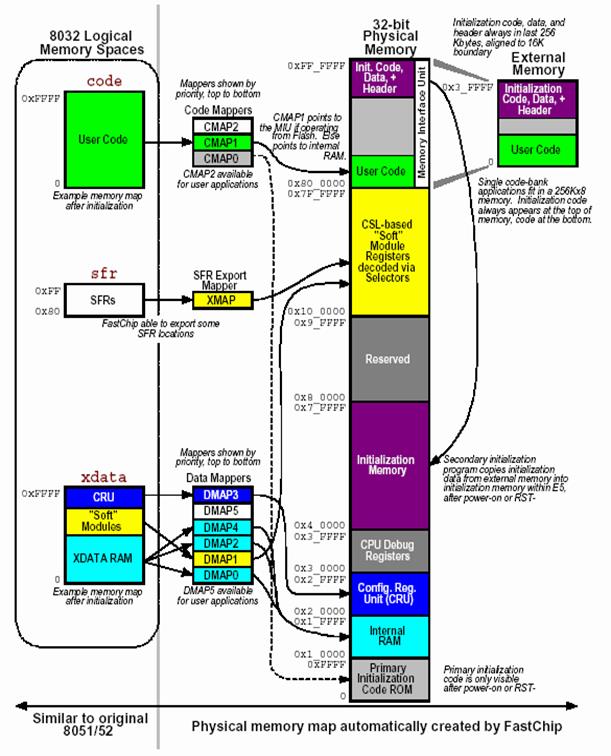

рис. 32 Адресное пространство микроконтроллера 8051 Внешняя память программ и память данных занимают по 64 Кбайт адресного пространства каждая. Память программ предназначена для хранения команд и аргументов, используемых в процессе выборки кода, а память данных - для хранения различных пользовательских данных. Обращение к внешней памяти программ и памяти данных, а также к определяемым пользователем SFR (закрашенные прямоугольники на рис.32) по системной шине может быть осуществлено напрямую. Внутреннее ОЗУ микроконтроллера состоит из прямо и косвенно-адресуемых областей и содержит такие встроенные регистры, как аккумулятор, регистр В, регистры контроля питанием, таймерами и последовательного порта, доступ к которым может быть осуществлен только внутри микроконтроллера. Обращение к внутренней памяти за пределами микроконтроллера недопустимо, поскольку это может привести к программной несовместимости. Адресные координаторы преобразуют 8-ми или 16-ти битный логический адрес микроконтроллера в 32-х битный физический адрес системной шины и обеспечивают связь микроконтроллера с внешней памятью. Координаторы распределены между зонами логических адресов. Каждая из этих зон занимает от 256 байт до 64 Кбайт памяти и ссылается на определенную область физических адресов. Зона начинается с любого логического адреса и занимает объем в соответствии с её размерами. В случае найденного соответствия между адресом, микроконтроллера и адресом, на который ссылается координатор, логический адрес будет преобразован в физический.

Рис. 33 Программная среда FastChip использует внутренние кодовые координаторы и координаторы данных для организации 16 Мб карты памяти.

Координаторы разделены по функциональному назначению: кодовые координаторы преобразуют адрес только кодов, координаторы данных - адрес только данных, а координаторы SFR – адрес SFR. Значение координаторов определяется в конфигурирующих регистрах. Каждый координатор имеет: 1. 8 бит адреса зоны, значение которого используются для определения соответствия с ожидаемым логическим адресом A{15:8}; 2. 5 бит смещения, которое определяется как логарифм с основанием два от значения размера зоны в байтах; 3. 24 бита - являются старшими битами физического адреса A{31:8}; 4. один бит разрешения.

Рис.34. Блок-диаграмма принципа работы адресного координатора Значение смещения (5 бит) определяет количество младших бит логического адреса, которые не будут учитываться в операции сравнения с целевым адресом зоны в координаторе. Ввиду того, что все зоны должны иметь размер от 256 байт и больше, то младшие 8 бит логического адреса в процессе сравнения не учитываются. В таком случае, координатор сравнивает старшие 8 бит логического адреса с 8-ю битами целевого адреса зоны и маскирует в соответствии со значением смещения определенное количество младших бит. После того, как адреса сравнены при установленном бите разрешения координатора, преобразованный адрес выставляется на системную шину. Младшие биты представленного физического адреса яв

|

||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 315; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.146.37.242 (0.011 с.) |