Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Архитектура микроконтроллераСодержание книги

Поиск на нашем сайте

Ускоренный 8051 микроконтроллер основан на стандартном 8051 ядре. Система на кристалле Е5 построена вокруг 8-битного АЛУ, которое использует внутренние регистры для временного хранения данных и для контроля периферийными устройствами. Поддерживает набор команд для 8051 и содержит блоки, краткое описание которых приводится ниже. АЛУ Является основой микроконтроллера и выполняет арифметические и логические операции. Организует команды перехода JUMP и рассчитывает при этом смещения. АЛУ не доступно для пользователя, но является необходимым элементом цепи, по которой проходят данные, представленные пользователем, и в регистрах которого генерируется результат. АСС (аккумулятор) и регистр В являются широко используемыми и относятся к регистрам специального назначения. АЛУ вырабатывает несколько сигналов состояния, которые сохраняются в регистре слова состояния (PSW). Аккумулятор Аккумулятор является основным регистром, используемым в арифметических и логических операциях, а также при перемещении данных в конфигурируемой системе на кристалле. Поскольку аккумулятор находится в памяти микроконтроллера, то большинство высокоскоростных операций выполняется через него. Регистр В 8-битный регистр, предназначен для операций умножения и деления. Для всех других команд является регистром общего назначения. PSW 8-битный регистр специального назначения, предназначен для хранения флагов состояния АЛУ. Содержит следующие биты: бит переноса, бит вспомогательного переноса, биты общего назначения, бит выбора регистрового банка, бит переполнения и бит четности. Указатели данных Используются при выполнении команд MOVX в обмене данными между внешней и внутренней памятью микроконтроллера. Поскольку данные могут перемещаться в обоих направлениях, то система на кристалле снабжена двумя указателями данных. Пользователь имеет возможность выбора между ними, что при минимальных программных затратах значительно повышает системную производительность. Сверхоперативное ОЗУ микроконтроллера В распоряжении микроконтроллера находятся 256 байт сверхоперативной памяти, удобной для временного хранения данных в процессе выполнения программы. Часть памяти является бит-адресуемой и непосредственно адресуемой микроконтроллером при выполнении булевых операций. Стековый указатель 8-битный регистр, указывающий на вершину стека. Стек размещается в сверхоперативной памяти микроконтроллера, поэтому его максимальный размер может быть 256 байт. Таймеры/счетчики Конфигурируемая система на кристалле располагает тремя 16-битными таймерами/счетчиками, каждый из которых занимает по два регистра специального назначения (SFR), доступных для чтения и записи. Другие SFR, связанные с таймерами, контролируют их режим и работу. Последовательный порт. 8051 микроконтроллер имеет один последовательный порт ввода/вывода, который может работать в одном из режимов: синхронный и асинхронный. Для управления им предусмотрено несколько SFR. Организация памяти 8051 микроконтроллер – это классическое устройство Гарвардской архитектуры, память которого разделена на 2 области: память программ и память данных. Память программ предназначена для хранения кодов операций, а память данных – для хранения данных. Память программ 8051 микроконтроллер поддерживает до 64 Кбайт адресного пространства, предназначенного для хранения программ. Эта память может быть внешней – Flash память – или внутренней – с использованием внутреннего системного ОЗУ. Все команды предусмотрены для выполнения из этой памяти. Команда MOVC предназначена для обращения к ней. Память данных 8051 микроконтроллер поддерживает до 64 Кбайт адресного пространства, предназначенного для хранения данных. Эта память доступна через команду MOVX. Также, для хранения данных отводятся 256 байт сверхоперативной памяти микроконтроллера и 8 Кбайт внутреннего ОЗУ системы, размер которого варьируется в зависимости от устройства. Сверхоперативная память микроконтроллера доступна путем прямой или косвенной адресации, а память регистров специального назначения – только прямой. Регистровая память Микроконтроллер стандарта 8051 располагает отдельно памятью программ и памятью данных, также встроенным на кристалле сверхоперативным ОЗУ, в дополнение к системному ОЗУ, и неопределенным числом внешних устройств памяти. Во внутреннем ОЗУ микроконтроллера располагаются SFR, которые могут быть доступны только путем прямой адресации. Сверхоперативное ОЗУ доступно путем прямой или косвенной адресации и занимает объем 256 Байт, как показано на рис. 44. Используется для хранения небольших по объему данных. Данные большим размером могут быть сохранены либо во внутреннем ОЗУ системы, либо во внешней памяти данных. Однако внутренняя память отличается быстрым доступом в отличие от внешней памяти. Внутри сверхоперативного ОЗУ микроконтроллера есть несколько областей специального назначения, описанные ниже.

рис.44. Карта регистровой памяти Рабочие регистры Область рабочих регистров состоит из четырех секторов, называемых банками. Каждый из банков содержит по восемь регистров. Банки имеют идентификационный номер от 0 до 3, а их регистры - R0, R1,…, R7. При обращении к регистрам используется прямая адресация. Они являются регистрами общего назначения, и при обращении к ним может быть активизирован только один банк через биты RS1– RS0 в регистре слова состояния PSW. Регистры R0 и R1 используются при косвенной адресации. Бит - адресуемые ячейки памяти Располагаются по адресам 20Н–2FH и могут быть доступны побайтно или побитно. Обращение к отдельному биту осуществляется соответствующей командой. Некоторые SFR также бит - адресуемы. Дешифратор команд способен различить доступ к биту или байту, ориентируясь на тип команды. SFR, чей адрес оканчивается цифрой от 0 до 8, является бит – адресуемым. Стековая память Сверхоперативная память микроконтроллера может использоваться в качестве стековой памяти. Область определяется указателем стека SP, который содержит адрес вершины. Всякий раз, когда происходит переход на другой адрес, вызов подпрограммы или прерывание, адрес возврата размещается в стековой памяти. Стек может располагаться по любому адресу во внутренней памяти микроконтроллера. По умолчанию, стековый указатель содержит адрес 07H, но пользователь может изменить его на любой другой. Стековый указатель указывает на последнее размещение. Поэтому, сначала происходит инкремент содержимого указателя, а затем только адрес помещается в стек. При чтении данных из стека – сначала происходит чтение, а затем содержимое указателя декрементируется. Регистры специального назначения SFR 8051 микроконтроллер использует SFR для контроля и слежения за периферией и ее режимами работы. SFR располагаются по адресам 80Н – FFH, и обращение к ним осуществляется способом прямой адресации. Некоторые из SFR бит - адресуемы. Это позволяет программе менять значение одного конкретного бита, не изменяя при этом значения других. В адресе таких регистров последний бит указывает на номер модифицируемого бита {0:7}. Все регистры специального назначения представлены в таблице 30. Незанятые ячейки памяти при чтении возвращают значении логической единицы. Расположение регистров специального назначения (SFR) Таблица 30

модуль

Указатель стека

Мнемоника: SP Адрес:81H SP – указывает на текущую вершину стека, размещенного в ОЗУ микроконтроллера. После сброса загружается значением 07Н. Обладает неограниченным доступом для чтения и записи. Первый указатель данных (младший байт)

Мнемоника: DPL Адрес:82H Младший байт первого 16-битного указателя данных. После сброса загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Первый указатель данных (старший байт)

Мнемоника: DPН Адрес:83H Старший байт первого 16-битного указателя. После сброса загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Второй указатель данных (младший байт)

Мнемоника: DPL1 Адрес:84H Второй указатель данных (старший байт)

Мнемоника: DPН1 Адрес:85H Пользователь может выбирать между указателями данных через бит DPS.0 в регистре выбора. Если регистры не используются по назначению, то они могут быть использованы в качестве регистров общего назначения. После сброса загружаются значением 00H. Обладают неограниченным доступом для чтения и записи. Регистр выбора указателя данных DPS

Мнемоника: DPS Адрес:86H Биты DPS.1-7 зарезервированы и при считывании выдают значение логического нуля. Бит DPS.0 – бит выбора пары регистров действующего указателя данных. DPS.0=1 - DPL1/DPH1 и DPS.0=0 - DPL/DPH. После сброса загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр управления питанием

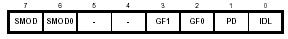

Мнемоника: PCON Адрес:87H Бит SMOD, если установлен, то указывает на удвоенную скорость передачи данных в бодах последовательного порта в режимах 1, 2 и 3. Бит SMOD0 – бит разрешения определения ошибки кадровой синхронизации. Его значение определяет поведение бита SCON.7 в контрольном регистре последовательного порта. Если SMOD0=1, то бит SCON.7 действует как флаг FE и указывает на наличие ошибки кадровой синхронизации. Если SMOD0=0, то бит SCON.7 ведет себя как стандартная для 8051 микроконтроллера функция и участвует в определении режима работы последовательного порта. GF.1- 0 – биты общего назначения для пользователя. Бит PD – бит выбора режима Power Down для конфигурируемой системы на кристалле. Когда бит PD установлен (PD=1), система входит в режим пониженного энергопотребления, прекращается генерирование тактовых сигналов и выполнение программы. Бит IDL – бит выбора холостого режима работы для микроконтроллера. При этом прекращается выполнение программы и генерирование тактовых сигналов для микроконтроллера и продолжается генерирование тактовых сигналов для последовательного порта, таймеров и блока прерывания. После сброса регистр загружается значением 00110000b. Обладает неограниченным доступом для чтения и записи. Контрольный регистр таймера

Мнемоника: ТCON Адрес:88H TF1 – флаг переполнения таймера 1. Очищается автоматически после выполнения программы по обслуживанию прерывания. Возможно программным путем устанавливать или очищать этот бит. TR1 – бит запуска таймера 1. Возможно программным путем устанавливать или очищать этот бит, чтобы запустить таймер или отключить соответственно. TF0 – флаг переполнения таймера 0. Очищается автоматически после выполнения программы по обслуживанию прерывания. Возможно программным путем устанавливать или очищать этот бит. TR0 – бит запуска таймера 0. Возможно программным путем устанавливать или очищать этот бит, чтобы запустить таймер или отключить соответственно. IE1 – флаг прерывания от таймера 1. Устанавливается аппаратно по фронту 0-1 (или по уровню логической единицы) на внешнем контакте INTR1 и аппаратно очищается после обслуживания вектора прерывания. Отслеживает состояние INIT1 сигнала. IT1 –бит управления прерыванием для таймера 1. Если бит установлен (IT1=1), то прерывание организуется по фронту 0-1, если сброшен (IT1=0), то прерывание организуется по уровню логической единицы на внешнем контакте прерывания INTR1. IE0 – флаг прерывания от таймера 0. Устанавливается аппаратно по фронту 0-1 (или по уровню логической единицы) на внешнем контакте INTR0 и аппаратно очищается после обслуживания вектора прерывания. Отслеживает состояние INIT0 сигнала. IT0 –бит управления прерыванием для таймера 0. Если бит установлен (IT0=1), то прерывание организуется по фронту 0-1, если сброшен (IT0=0), то прерывание организуется по уровню логической единицы на внешнем контакте прерывания INTR0. ! Внешние сигналы прерывания INTR0 и INTR1 отличны от сигналов для микроконтроллера стандарта 8051 тем, что их активное состояние определяется уровнем логической единицы или срезом 0-1, а не наоборот, как в стандарте 8051. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр управления режимом работы таймера/счетчика

Мнемоника: TMOD Адрес: 89h Бит GATE определяет момент запуска таймера/счетчика. Если GATE=1 при соответствующем установленном бите TRx в контрольном регистре, то таймер/счетчик запустится при появлении на выводе INTRx уровня логической единицы. Когда GATE=0, то запуск счетчика/таймера будет определяться состоянием бита TRx. Бит С/Т – бит выбора между функцией таймера и счетчика. Когда С/Т=0, активизируется таймер. Его значение будет инкрементироваться с тактовыми сигналами внутренней системы синхронизации. Когда С/Т=1, активизируется счетчик. Его значение будет инкрементироваться с каждым спадающим фронтом сигнала на выводе Tx. Режимы работы таймера 0 и таймера 1 Таблица 31

М1 и М2 – биты выбора режима работы для таймеров/счетчиков. Описание режимов приведено в табл. 31. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Младший байт счетчика/таймера 0 Мнемоника: TL0 Адрес: 8Ah После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Младший байт счетчика/таймера 1 Мнемоника: TL1 Адрес: 8Bh После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Старший байт счетчика/таймера 0 Мнемоника: TH0 Адрес: 8Ch После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Старший байт счетчика/таймера 1 Мнемоника: TH1 Адрес: 8Dh После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Этот бит также управляет скоростью передачи данных в бодах для последовательного порта, который может работать с различными скоростями в режиме 1 и 3. Расчет для скорости показан ниже с учетом того, что SMOD – это бит PCON.7 в контрольном регистре PCON, F – тактовая частота процессора и Baud – бод, желаемый показатель скорости.

Значение может дробным, поэтому требует округления в сторону ближайшего целого значения. В некоторых случаях, меняя тактовую частоту, можно добиться желаемой скорости в бодах для последовательного порта. Регистр управления временными параметрами таймеров

Мнемоника: CKCON Адрес: 8Eh Биты WD1-0 – биты выбора режима работы для сторожевого таймера. Они определяют время, по истечению которого генерируется вектор на прерывание. Время сброса таймера определяется как сумма приведенного во второй колонке времени (см. табл. 32) и 512 тактов. Режимы работы сторожевого таймера Таблица 32

Бит T2M – бит выбора режима работы для таймера 2. Когда T2M=1, таймер отсчитывает каждые 4 такта, а когда T2М=0 – каждые 12 тактов, как для стандартного 8051 микроконтроллера. Бит T1M – бит выбора режима работы для таймера 1. Когда T1M=1, таймер отсчитывает каждые 4 такта, а когда T1М=0 – каждые 12 тактов, как для стандартного 8051 микроконтроллера. Бит T0M – бит выбора режима работы для таймера 0. Когда T0M=1, таймер отсчитывает каждые 4 такта, а когда T0М=0 – каждые 12 тактов, как для стандартного 8051 микроконтроллера. Биты CKCON.2-0 зарезервированы. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Контрольный регистр последовательного порта

Мнемоника: SCON Адрес: 98h Бит SM0/FE – бит выбора режима работы последовательного порта или флаг ошибки кадровой синхронизации. Назначение бита определяется битом SMOD0 в регистре управления питанием. Режимы работы последовательного порта представлены в табл.33. Флаг FE устанавливается при появлении недопустимого стопового бита и должен очищаться программным обеспечением. Бит SM1 – первый бит определения режима работы последовательного порта. Бит SM2 – второй бит определения режима работы последовательного порта, регулирует передачу данных в различных режимах. В режимах 2 и 3, когда бит SM2 установлен, в многопроцессорной системе организуется «полнометражная» передача данных без фиксации стоповых битов. При этом девятый бит данных (RB8), равный нулю, не будет влиять на значение бита RI. В режиме 1, когда бит SM2 установлен, бит RI будет устанавливаться всякий раз при получении допустимого стопового бита. В режиме 0, бит SM2 определяет синхронизацию порта. В случае, когда SM2=0, через порт данные будут передаваться с частотой 1/12, что обеспечивает совместимость со стандартным 8051 микроконтроллером. Когда SM2=1, порт будет действовать с частотой 1/4, обеспечивая высокоскоростную синхронную передачу данных. Режимы работы последовательного порта Таблица 33

Бит REN – бит разрешения получения данных через порт. Когда REN=1, порт открыт для получения последовательности данных, в противном случае, порт блокирован. Бит TB8 – девятый бит данных, экспортируемых через последовательный порт в режимах 2 и 3. Устанавливается и очищается программным обеспечением. Бит RB8 – отражает значение девятого бита импортируемых данных в режимах 2 и 3. В режиме 1, если SM2=0, RB8 отображает значение стопового бита. В режиме 0 не имеет функционального назначения. Бит TI – флаг прерывания передачи данных. Устанавливается аппаратно после передачи восьмого бита в режиме 0 или в начале передачи стопового бита во всех других режимах. Этот флаг должен очищаться программным обеспечением. Бит RI – флаг прерывания приема данных. Устанавливается аппаратно после приема восьмого бита в режиме 0 или в течение приема стопового бита во всех других режимах. Этот флаг может быть очищен только программным обеспечением. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Буфер данных последовательного порта Мнемоника: SBUF Адрес: 99h Биты SBUF.7-0 – область размещения данных, импортируемых или экспортируемых через последовательный порт. Фактически буфер состоит из двух 8-ми разрядных регистров, один из которых является принимающим, а другой – передающим. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр разрешения прерываний

Мнемоника: IE Адрес: A8h Бит ЕА – бит разрешения всех прерываний. Когда EA = 0, все прерывания, кроме HPINT, запрещены. Бит IE.6 – нереализованный бит. При чтении возвращает значение логической единицы. Бит ET2 – бит разрешения прерывания от таймера 2. Когда бит установлен, прерывание разрешено. Бит ES – бит разрешения прерывания от последовательного порта. Когда бит установлен, прерывание разрешено. Бит ET1 – бит разрешения прерывания от таймера 1. Когда бит установлен, прерывание разрешено. Бит EX1 – бит разрешения внешнего прерывания 1. Когда бит установлен, прерывание разрешено. Бит ET0 – бит разрешения прерывания от таймера 0. Когда бит установлен, прерывание разрешено. Бит EX0 – бит разрешения внешнего прерывания 0. Когда бит установлен, прерывание разрешено. После сброса регистр загружается значением 01000000b. Обладает неограниченным доступом для чтения и записи. Регистр хранения адреса подчиненного Мнемоника: SADDR Адрес: A9h Используется только в операциях микроконтроллера, задействующих последовательный порт. Загружается значением полученного или передаваемого адреса для последовательного порта, когда система на кристалле Е5 используется в качестве подчиненного устройства в многопроцессорной системе. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр определения приоритета прерываний

Мнемоника: IP Адрес: B8h Биты IP.7-6 – нереализованные биты, при чтении возвращают значение логической единицы. Бит PT2 – бит определения приоритета прерывания от таймера 2. Когда бит установлен, указывает на высокий приоритет. Бит PS – бит определения приоритета прерывания от последовательного порта. Когда бит установлен, указывает на высокий приоритет. Бит PT1 – бит определения приоритета прерывания от таймера 1. Когда бит установлен, указывает на высокий приоритет. Бит PX1 – бит определения приоритета внешнего прерывания 1. Когда бит установлен, указывает на высокий приоритет. Бит PT0 – бит определения приоритета прерывания от таймера 0. Когда бит установлен, указывает на высокий приоритет. Бит PX0 – бит определения приоритета внешнего прерывания 0. Когда бит установлен, указывает на высокий приоритет. После сброса регистр загружается значением 11000000b. Обладает неограниченным доступом для чтения и записи. Регистр-маска для адреса подчиненного Мнемоника: SADEN Адрес: B9h Этот регистр используется для автоматического распознавания адреса последовательного порта. Если бит в регистре SADEN содержит единицу, то соответствующий его расположению бит в регистре SADDR сравнивается с битом входящих данных. Если бит в регистре SADEN содержит логический ноль, то соответствующий бит в регистре SADDR не участвует в сравнении. Если все биты регистра SADEN содержат ноль, то прерывание вырабатывается для любого входящего адреса. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр доступа к контрольному регистру сторожевого таймера Мнемоника: TA Адрес: C7h Этот регистр отвечает за доступ к защищенным от случайной записи битам контрольного регистра сторожевого таймера. Другой специальный регистр PROTECT поддерживает безопасный режим инициализации. Для доступа к охраняемым битам, программным обеспечением должна быть предусмотрена предварительная запись в регистр TA значения AAh, за которой незамедлительно следует запись другого значения – 55h. Эти действия позволят открыть окно из трех машинных циклов, в течение которых охраняемые биты могут быть изменены программным обеспечением. При чтении регистр TA возвращает значение FFh. Обладает неограниченным доступом для записи, чтение регистра не требуется. Пример организации доступа к охраняемым битам контрольного регистра сторожевого таймера:

Контрольный регистр таймера 2

Мнемоника: T2CON Адрес: C8h Бит TF2 – флаг переполнения таймера 2. Этот бит устанавливается, в случае переполнения таймера или по достижению им фиксированного значения при обратном отсчете. Флаг устанавливается только, если биты RLCK и TCKL имеют нулевые значения. Очищается только программным обеспечением. Программное обеспечение может его и устанавливать. Бит EXF2 – флаг внешнего прерывания для таймера 2. Этот бит устанавливается в случае появления на выводе T2EX спадающего фронта импульса внешнего сигнала или в случае переполнения таймера 2 при прямом или обратном отсчете в соответствии с положением, определяемым битами CP/RL2, EXEN2 и DCEN. Если бит установлен по причине появления внешнего сигнала на выводе T2EX, то он должен быть очищен программным обеспечением. Установка бита внешним сигналом или программным обеспечением приведет к генерации прерывания для таймера, если прерывание разрешено. Бит RCLK – флаг синхронизации последовательного порта в режиме приема. Этот бит определяет источник задания скорости получения данных в бодах в режимах 1 или 3. Если бит не установлен, тогда скорость в бодах будет определяться переполнением таймера 1, в другом случае, когда RCLK=1, скорость будет определяться переполнением таймера 2. Установка этого бита введет таймер 2 в режим задания скорости приема данных в бодах через последовательный порт. Бит ТCLK – флаг синхронизации последовательного порта в режиме передачи. Этот бит определяет источник задания скорости передачи данных в бодах в режимах 1 или 3. Если бит не установлен, тогда скорость в бодах будет определяться переполнением таймера 1, в другом случае, когда ТCLK=1, скорость будет определяться переполнением таймера 2. Установка этого бита введет таймер 2 в режим задания скорости передачи данных в бодах через последовательный порт. Бит EXEN2 – бит разрешения внешнего прерывания для таймера 2. Этот бит разрешает функцию захвата/перезагрузки таймера при появлении внешнего сигнала на выводе T2EX, но в том случае, если таймер 2 не является источником задания скорости приема/передачи данных через последовательный порт. Если бит EXEN2=0, то внешний сигнал будет игнорироваться. Если EXEN2=1, то появление спадающего фронта импульса внешнего сигнала на выводе T2EX приведет к перезагрузке или фиксации значения таймера. Бит TR2 – контрольный бит запуска таймера 2. Этот бит разрешает или запрещает работу таймера. После остановки таймера, путем очистки бита TR2, текущее значение таймера сохраняется в регистрах TH2, TL2. Бит C/T2 – бит выбора между функцией счетчика и таймера. Независимо от этого бита, таймер отсчитывает два такта за импульс, когда работает в качестве источника задания скорости приема/передачи данных через последовательный порт. Когда бит не установлен (С/Т2=0), таймер 2 работает как таймер, скорость которого определяется значением бита Т2М в регистре управления временными параметрами таймеров CKCON. Когда С/Т2=1, таймер 2 работает как счетчик импульсов сигнала Т2. Бит CP/RL2 – бит выбора функции захвата/перезагрузки для таймера 2. В том случае, когда биты RCLK и ТCLK будут установлены, бит CP/RL2 не будет иметь функционального значения, поскольку таймер будет работать в режиме авто-перезагрузки после каждого переполнения. В другом случае, если бит CP/RL2=0, то таймер будет перезагружаться каждый раз, когда произойдет его переполнение или на выводе T2EX появится спадающий фронт импульса внешнего сигнала при установленном бите EXEN2 (EXEN2=1). Если бит CP/RL2=1, то после появления внешнего сигнала на T2EX (спадающий фронт импульса) при установленном бите EXEN2 произойдет захват таймера. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр управления режимом работы таймера 2

Мнемоника: T2MOD Адрес: С9h Бит DCEN – бит разрешения обратного отсчета для таймера 2. Направление отсчета зависит от сигнала на выводе T2EX. Когда бит DCEN установлен, и на выводе T2EX присутствует сигнал логической единицы, то значение таймера инкрементируется. Если на выводе T2EX присутствует сигнал логического нуля, то значение таймера декрементируется. Если бит DCEN не установлен, то значение таймера будет изменяться только в сторону увеличения. После сброса регистр загружается значением FEH. Обладает неограниченным доступом для чтения и записи. Регистр хранения младшего байта фиксированного значения таймера 2 Мнемоника: RCAP2L Адрес: САh Этот регистр используется для хранения младшего байта значения таймера 2, работающего в режиме захвата. Также используется для хранения младшего байта 16-ти разрядного значения для таймера 2, работающего в режиме авто-перезагрузки. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр хранения старшего байта фиксированного значения таймера 2 Мнемоника: RCAP2H Адрес: СBh Этот регистр используется для хранения старшего байта значения таймера 2, работающего в режиме захвата. Также используется для хранения старшего байта 16-ти разрядного значения для таймера 2, работающего в режиме авто-перезагрузки. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистры RCAP2L и RCAP2H потенциально могут управлять скоростью передачи данных в бодах для последовательного порта, который может работать с различными скоростями в режиме 1 и 3. Расчет для скорости показан ниже с учетом того, что SMOD – это бит PCON.7 в контрольном регистре PCON, F – тактовая частота процессора и Baud – бод, желаемый показатель скорости.

Значение результата может дробным, поэтому требует округления в сторону ближайшего целого значения. В некоторых случаях, меняя тактовую частоту, можно добиться желаемой скорости в бодах для последовательного порта. Младший байт таймера 2 Мнемоника: TL2 Адрес: СCh После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Старший байт таймера 2 Мнемоника: TH2 Адрес: СDh После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Регистр слова состояния

Мнемоника: PSW Адрес: D0h Бит CY – флаг переноса. Устанавливается в результате арифметических операций, генерирующих перенос в АЛУ. Также используется как аккумулятор для битовых операций. Бит АС – вспомогательный бит переноса. Устанавливается после операции сложения или вычитания, в результате которой произошел перенос бита в старшую тетраду или заем из старшей тетрады. Бит F0 – флаг пользователя, является битом общего назначения. Может быть установлен или очищен пользователем через программное обеспечение. Биты RS.1-0 – биты выбора банка регистров общего назначения, как показано в таблице 34. Определение рабочего банка регистров через биты RS1 и RS2 Таблице 34

Бит OV – флаг переполнения. Устанавливается в результате арифметических операций и указывает на то, что результат превысил разрядность аккумулятора. Бит F1 – флаг пользователя, является битом общего назначения. Может быть установлен или очищен пользователем через программное обеспечение. Бит Р – флаг четности результата арифметических действий. Устанавливается и очищается аппаратно, сигнализирует о четности либо нечетности первого бита в аккумуляторе. После сброса регистр загружается значением 00H. Обладает неограниченным доступом для чтения и записи. Контрольный регистр сторожевого таймера

Мнемоника: WDCON Адрес: D8h Бит WDCON.7 – нереализованный бит. При чтении возвращает значение логической единицы. Бит POR – флаг возникновения сброса после включения питания. Устанавливается аппаратно. Очистка флага может быть осуществлена только программным обеспечением. Также, программным обеспечением можно установить этот флаг. Бит EHPI – бит разрешения высокоприоритетного прерывания. Если EHPI=1, то прерывание разрешено. Если EHPI=0, то сигнал прерывания HPINT игнорируется. Бит HPI – флаг высокоприоритетного прерывания. Устанавливается аппаратно при появлении сигнала HPINT. Флаг должен быть очищен программным обеспечением. Если бит EHPI установлен, то запись логической единицы в бит HPI вызовет прерывание. ! Некоторые биты регистра WDCON защищены от случайной записи, которая может произойти в результате выполнения ошибочной программы. Для того чтобы изменить значение битов RWT, EWT, WDIF или POR, необходимо записать в определенной последовательности данные в регистр доступа TA. Бит WDIF – флаг прерывания сторожевого таймера. Если прерывание разрешено, то бит устанавливается аппаратно после генерации прерывания. Если прерывание не разрешено, то флаг сигнализирует об истечении времени блокировки. Бит WTRF – флаг сброса сторожевого таймера. Устанавливается аппаратно после сброса таймера. Флаг должен быть очищен программным обеспечением. Системный сброс после включения питания также очистит этот бит. Когда бит EWT=0, то бит WTRF не имеет функционального назначения. Бит EWT – бит разрешения сброса сторожевого таймера. Установка этого бита разрешает функцию сброса таймера. Бит RWT – бит сброса сторожевого таймера. Обычно устанавливается программным обеспечением до истечения времени блокировки. Если в соответствующий момент бит RWT не будет установлен, то произойдет одно из двух возможных событий: 1. если был установлен бит EWDI (EIE.4), и время блокировки сторожевого таймера истекло, то произойдет генерация прерывания; 2. если был установлен бит EWT, и время блокировки сторожевого таймера истекло, то через 512 тактов произойдет сброс микроконтроллера. Если в течение этих 512 тактов установить бит RWT, то сброс произойдет только для сторожевого таймера. После внешнего сброса регистр загружается значением 1x0x0xx0b, где символом «х» обозначены биты, неподверженные изменениям. После сброса сторожевого таймера установится бит WTRF, а после сброса системы при включении/выключении питания - очистится. Также, после сброса системы при включении питания установится бит POR, а EWT обнулится (EWT=0), и его значение (EWT) не будет подвержено влиянию других сбросов. ! После системного сброса многие из битов регистра WDCON останутся неизменными. И если сторожевой таймер был активизирован до сброса, то это положение сохранится и после. Однако время блокировки таймера изменится на минимально допустимое, поскольку оно определяется регистром управления временными параметрами CKCON, значение которого сбросится вместе с системой. Все разряды регистра имеют неограниченный доступ для чтения. Биты RWT, EWT, WDIF или POR требуют доступ для записи через специальный регистр ТА. Остальные

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 349; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.179.30 (0.013 с.) |

бит - адресуемые ячейки памяти

бит - адресуемые ячейки памяти неиспользуемые SFR, доступные пользователю через программный

неиспользуемые SFR, доступные пользователю через программный – порты ввода-вывода Р0 - Р3, реализованные в логической матрице. Их SFR экспортируемы.

– порты ввода-вывода Р0 - Р3, реализованные в логической матрице. Их SFR экспортируемы.