Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Блок сопряжения с внешней памятью MIUСодержание книги

Поиск на нашем сайте

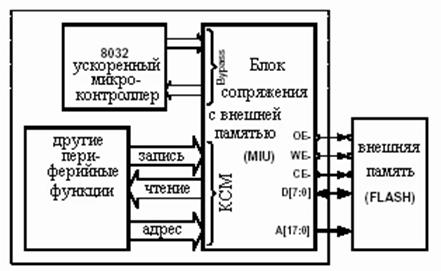

Блок сопряжения с внешней памятью представляет собой гибкий, непривязанный интерфейс между конфигурируемой системой на кристалле и устройствами внешней памяти, как показано на рис.27. Обеспечивает связь с такими устройствами памяти, как Flash ППЗУ, которое содержит данные конфигурации и пользовательские программы, статическое ОЗУ или СППЗУ. Сигналы управления для всех устройств памяти идентичны.

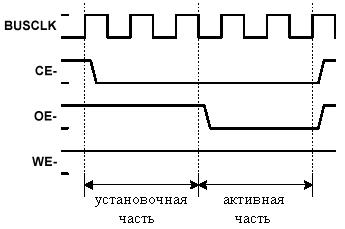

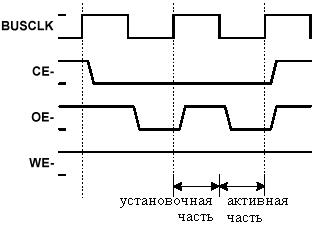

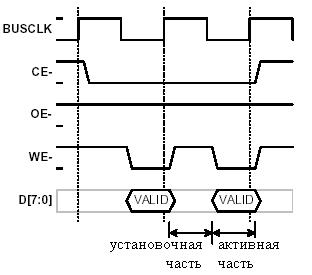

Рис.27. Интерфейс блока сопряжения с внешней памятью обеспечивает связь между микроконтроллером, функциями его периферии и устройствами внешней памяти Блок сопряжения с внешней памятью предназначен для выполнения двух задач: 1. предоставить гибкую многоканальную шину данных и адреса для подключения устройств внешней памяти, не используя при этом дополнительные порты ввода/вывода; 2. обеспечить удобный порт для доступа внешних функций из других периферийных устройств, включая конфигурируемую логическую матрицу. Как показано на рис.27, MIU обеспечивает прямую связь между микроконтроллером и внешней памятью. Не используя ресурсов внутренней шины, конфигурируемая система на кристалле поддерживает синхронизацию, аналогичную для микроконтроллера стандарта 8051. Синхронизация доступа к внешней памяти может быть различной, но допустимой в рамках конфигурируемой системы на кристалле Е5, предполагая возможность оптимизации или замедления процесса доступа к различным устройствам внешней памяти с различными динамическими характеристиками. MIU может также взаимодействовать с внешним ППЗУ с последовательной выборкой для конфигурации программируемых вентильных матриц со структурой статического ОЗУ. Выводы адреса, данных и управления блока сопряжения с внешней памятью могут контролироваться другими периферийными функциями, включая конфигурируемую логическую матрицу, чтобы разрешить и обеспечить доступ к внешним устройствам периферии и памяти. При этом блок MIU затрачивает минимальные ресурсы организационной логики конфигурируемой матрицы. Главные особенности блока сопряжения с внешней памятью: 1. поддерживает интерфейс с внешней памятью стандарта 256К´8; 2. возможность расширения внешней памяти до 4G´8 через программируемые порты ввода/вывода; 3. возможность программирования процесса синхронизации для операций чтения и записи; 4. возможность режима прямого доступа микроконтроллером к внешней памяти; 5. возможность подключения внешних устройств памяти с последовательным интерфейсом; 6. возможность расширения системы через режим Multi-chip. Функциональное описание Блок сопряжения с внешней памятью обеспечивает взаимодействие внутренней системной шины с внешней памятью. Отслеживая внутреннюю шину, блок MIU следит за состоянием внешнего устройства, чтобы определить момент, когда оно будет доступно для записи или для чтения. В момент, когда устройство окажется готовым к обмену, блок сопряжения выставит соответствующие сигналы записи, чтения и управления. Как было сказано ранее, процесс синхронизации для операций чтения и записи может быть запрограммирован пользователем. Три бита в регистре MIUCTRL0 определяют синхронизацию для каждой части внешних циклов. Цикл чтения разделен на 2 части: установочную и активную, как показано на рис.28. Для того, чтобы поддержать один цикл чтения, минимальные значения установочной и активной частей должны быть соответственно 0 и 1. Передний фронт сигнала ОЕ возникает в момент спадающего фронта тактового сигнала, а задний фронт – в момент нарастающего фронта тактового сигнала. В одном цикле чтения, в зависимости от количества рабочих тактов, время установки и длительность сигнала ОЕ первоначально составляют приблизительно по полтакта и могут быть увеличены до 7 ½ тактов. В конечном счете, цикл чтения может быть запрограммирован на время 25 ÷ 375 нс с кратностью 25 нс (время одного такта) при тактовой частоте 40 МГц.

Рис.28. Обобщенный цикл чтения данных через блок MIU

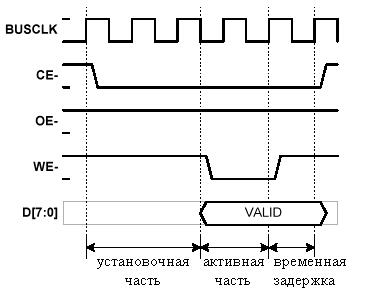

Рис.29. Один такт цикла чтения данных через блок MIU Цикл записи разделен на три части: установочная, активная и временная задержка, как показано на рис.30. Последняя часть является необязательной. Первые две части аналогичны тем, что были описаны для цикла чтения, только в данном случае активизируется сигнал разрешение записи WE. Время удержания данных на шине необходимо для устройств, не отвечающих заданному быстродействию системы, поэтому в зависимости от быстродействия устройства третья часть может занимать в цикле записи от 0 до 7 тактов. Вариант самой быстрой записи реализуется за один такт, где по полтакта приходится на первую и вторую части. Поскольку каждая из этих частей может быть увеличена до 7 ½ тактов, то в целом, цикл записи без задержки может быть запрограммирован на время 25 ÷ 375 нс с кратностью 25 нс. Если учесть время максимальной временной задержки, которое составляет 7 тактов, или 175 нс, то цикл записи может быть запрограммирован на время 25 ÷ 550 нс с кратностью 25 нс. при тактовой частоте 40 МГц.

Рис.30. Обобщенный цикл записи через блок MIU

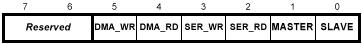

Рис.31. Один такт цикла записи данных через блок MIU Поддержка циклов ожидания Необходимость во временной задержке возникает при каждой операции чтения данных из устройства внешней памяти, исключая случаи сопряжения с быстродействующим устройством, когда цикл чтения может быть организован за один такт. Операция записи данных во внешнее устройство может быть реализована за любое время. Поскольку в процессе записи адрес и данные сохраняются в буфере, то блок сопряжения с внешней памятью не нуждается в ресурсах системной шины для постоянного предоставления данных. Организация временной задержки необходима в том случае, когда во время записи данных в устройство внешней памяти возникает необходимость в очередном доступе к памяти. Поскольку блок сопряжения с внешней памятью поддерживает режим прямого доступа микроконтроллера к устройству внешней памяти без затрат ресурсов внутренней шины, то временная задержка возникает из-за того, что каждый протокол обмена по обходному пути дублируется на внутренней шине в целях отладки. Сигнал ожидания синхронизируется в соответствии с копией протокола на шине. Арбитраж запросов Существуют три потенциальных источника, которые во взаимодействии с блоком сопряжения с внешней памятью выступают в роли мастера: 1. любой мастер, который через системную шину может иметь доступ к блоку MIU; 2. микроконтроллер, который, не используя ресурсов внутренней шины, может иметь прямой доступ к блоку MIU; 3. программируемые адресные селекторы, которые могут генерировать запросы внешней памяти. Режим запроса внешней памяти Программный модуль, реализованный в логической матрице, используя ресурсы блока MIU, также может получить доступ к внешней памяти. Функции логической матрицы могут неоднократно использовать сигналы адреса и данных, а также некоторые сигналы управления ОЕ и WE. Логическая матрица может запросить цикл обмена с внешней памятью, используя специальный режим селектора для генерации сигнала активизации устройства CE, направленного к устройству внешней памяти. Сигналы управления WE, ОЕ, адреса и данных генерируются через блок MIU. Сигналы WE и OE были рассмотрены ранее, как и то, что передний фронт этих сигналов возникает в момент спадающего фронта тактового сигнала, а задний фронт – в момент нарастающего фронта тактового сигнала. Поэтому становится возможным протекание операций чтения и записи за один такт. По сигналу WAITNEXT блок MIU оценивает готовность устройства внешней памяти принять или предоставить данные и при необходимости увеличивает длительность сигналов управления (OE, WE), а также определяет момент времени, когда можно закончить текущий цикл обмена и организовать новый. Установочная часть цикла записи составляет всегда ½ такта, но при необходимости, она может быть расширена на целое число тактов до 7. Временная задержка, которая организуется во время цикла записи, обусловлена только задержкой на линиях адреса и данных, запрашивающих внешнюю память с нулевым временем удержания. Если для приложения требуется индивидуальная синхронизация, то сигналы OE и WE генерируются логической матрицей, для чего необходимо, чтобы вывода порта были соединены с соответствующими выводами устройства внешней памяти. Инициализация блока MIU После сброса системы при включении питания или других аппаратных сбросов блок сопряжения с внешней памятью начинает работать как мастер на системной шине. При этом он оказывается в состоянии готовности получать команды от устройства внешней памяти, что удобно при инициализации системы в режиме Slave. Если вывод SLAVE- подтянут к питанию, то в процессе инициализации системы блок MIU станет подчиненным. В случае сброса системы при включении питания или других аппаратных сбросов вывод CE- оказывается подтянутым к питанию через нагрузочный резистор с целью исключить процесс случайной записи. Описание регистров блока сопряжения с внешней памятью Блок MIU и режимы его работы программируются через четыре регистра. Регистр определения режима работы блока MIU Этот регистр определяет текущий режим работы блока MIU.

Мнемоника: MIUMODE Адрес: FE30H Бит SLAVE, когда установлен, определяет режим подчиненного для блока MIU. Для большинства отдельных приложений этот режим используется после конфигурации. Бит очищается после сброса системы. Бит MASTER, когда установлен, назначает блок MIU мастером на внутренней системной шине. Этот режим является первоначальным на момент включения питания. Бит устанавливается после сброса системы. Бит SER_RD, когда установлен, определяет режим работы блока MIU, при котором данные конфигурации считываются из внешнего ППЗУ с последовательной выборкой. Бит очищается после сброса системы при включении питания или других аппаратных сбросов. Бит SER_WR используется для программирования внешних устройств памяти типа FLASH или ППЗУ с последовательной выборкой, основанного на структуре СППЗУ. Бит очищается после сброса системы при включении питания или других аппаратных сбросов. Биты DMA_RD и DMA_WR необходимо оставлять очищенными. Они являются битами зарезервированного режима MIU, используемого в процессе производства. Бит очищается после сброса системы при включении питания или других аппаратных сбросов. ! Контрольные регистры блока MIUявляются частью набора «скрытых» контрольных регистров конфигурируемой системы на кристалле Е5. Для того, чтобы получить к ним доступ, необходимо установить бит BLOCKSIZE в регистре DMAP3_CTL. Контрольные регистры обычно не модифицируются пользовательским кодом. Контрольные регистры синхронизации Регистр этого типа определяют синхронизацию процессов чтения и записи, определяют длительность сигналов управления, генерируемых блоком MIU. Значение временной задержки в цикле записи определяется тремя битами WHT[2:0], которые распределены между двумя контрольными регистрами.

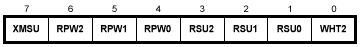

Мнемоника: MIUCTRL0 Адрес:FE31H Биты WSU [2:0] определяют длительность первой части цикла записи, т.е. определяют число дополнительных тактов, которые будут добавлены к первоначальному минимальному значению установочной части цикла. Фактическое значение времени определяется как произведение суммы определяемого тремя битами значения и ½ такта на период одного такта, т.е. (WSU[2:0] + ½) * TCLOCK. Все биты устанавливаются после сброса системы при включении питания или других аппаратных сбросов, что соответствует максимальному значению длительности установочной части цикла записи, принятому для самых медленных устройств. Длительность установочной части цикла записи Таблица 15

Биты WPW [2:0] определяют длительность второй части цикла записи. Фактическое значение времени определяется как (WPW[2:0] + ½) * TCLOCK. Все биты устанавливаются после сброса системы при включении питания или других аппаратных сбросов, что соответствует максимальному значению длительности активной части цикла записи, принятому для самых медленных устройств. Длительность активной части цикла записи Таблица 16

Биты WHT [2:0] определяют длительность третьей части цикла записи. Фактическое значение времени определяется как WHT[2:0] * TCLOCK. Все биты устанавливаются после сброса системы при включении питания или других аппаратных сбросов, что соответствует максимальному значению временной задержке в цикле записи, принятому для самых медленных устройств. Примечание: Бит WHT2 расположен в регистре MIUCTRL1. Установка длительности задержки Таблица 17

Мнемоника: MIUCTRL 1 Адрес:FE32H Биты RSU [2:0] определяют длительность первой части цикла чтения, т.е. определяют число дополнительных тактов, которые будут добавлены к первоначальному минимальному значению установочной части цикла. Фактическое значение времени определяется как произведение суммы определяемого тремя битами значения и ½ такта на период одного такта, т.е. (RSU[2:0] + ½) * TCLOCK. Все биты устанавливаются после сброса системы при включении питания или других аппаратных сбросов, что соответствует максимальному значению длительности установочной части цикла чтения, принятому для самых медленных устройств. Установка длительности неактивной части цикла чтения Таблица 18

Биты RPW [2:0] определяют длительность второй части цикла чтения. Фактическое значение времени определяется как (RPW[2:0] + ½) * TCLOCK. Все биты устанавливаются после сброса системы при включении питания или других аппаратных сбросов, что соответствует максимальному значению длительности активной части цикла чтения, принятому для самых медленных устройств. Установка длительности импульса ОЕ Таблица 19

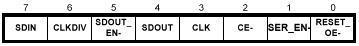

Бит XMCU разрешает дополнительный такт для установочной части в расширенных циклах. Очищается после сброса системы при включении питания и других аппаратных сбросов. Регистр управления работой MIU с внешними устройствами памяти с последовательным интерфейсом Этот регистр обеспечивает управление последовательным режимом конфигурации системы и внешним программируемым устройством ППЗУ с последовательной выборкой, основанным на структуре Flash или СППЗУ памяти.

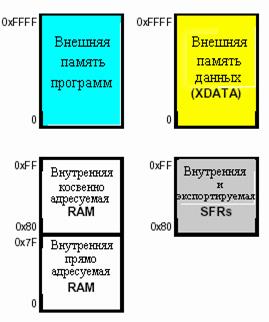

Мнемоника: MIUSCTL Адрес: FE33H Бит RESET_OE управляет выводом RESET/OE устройства внешней памяти через вывод ОЕ блока MIU. Устанавливается после сброса системы при включении питания и других аппаратных сбросов. Бит SER_EN управляет выводом WE внешнего устройства ППЗУ, основанного на структуре Flash или СППЗУ памяти, во время программирования. Устанавливается после сброса системы при включении питания и других аппаратных сбросов. Бит CE управляет выводом активизации устройства внешней памяти ППЗУ с последовательной выборкой. Устанавливается после сброса системы при включении питания и других аппаратных сбросов. Бит SDOUT является битом последовательных данных устройства внешней памяти. Используется только при программировании внешнего устройства памяти ППЗУ с последовательной выборкой. Сброс никакого влияния на значение бита не оказывает. Бит SDOUT_EN разрешает вывод последовательных данных для записи во внешнее устройство памяти. В режиме последовательной записи этот бит осуществляет прямой контроль над трехстабильными линиями буферов, содержащих выходные данные. Очищается после сброса системы при включении питания и других аппаратных сбросов. Бит CLKDIV предназначен для задания синхронизации только процесса чтения последовательных данных. SCLK=BUSCLK/4, если CLKDIV=0, и SCLK=BUSSCLK/64, если CLKDIV=1. Этот бит устанавливается по умолчанию для режима медленного считывания после сброса системы при включении питания и других аппаратных сбросов. Бит SDIN является битом последовательных данных, читаемых из устройства внешней памяти. Бит SDIN доступен только для чтения. Адресные координаторы Адресные координаторы преобразуют адреса, по которым микроконтроллер обращается к памяти программ, данных и регистрам специального назначения (SFR), в адреса, допустимые на системной шине системы на кристалле Е5 компании Trisend. Микроконтроллер 8051 поддерживает следующие адресные пространства: внешняя память программ, внешняя память данных, внутренняя прямо адресуемая память, внутренняя косвенно-адресуемая память, внутренняя экспортируемая область регистров специального назначения, как показано на рис.32.

рис. 32 Адресное пространство микроконтроллера 8051 Внешняя память программ и память данных занимают по 64 Кбайт адресного пространства каждая. Память программ предназначена для хранения команд и аргументов, используемых в процессе выборки кода, а память данных - для хранения различных пользовательских данных. Обращение к внешней памяти программ и памяти данных, а также к определяемым пользователем SFR (закрашенные прямоугольники на рис.32) по системной шине может быть осуществлено напрямую. Внутреннее ОЗУ микроконтроллера состоит из прямо и косвенно-адресуемых областей и содержит такие встроенные регистры, как аккумулятор, регистр В, регистры контроля питанием, таймерами и последовательного порта, доступ к которым может быть осуществлен только внутри микроконтроллера. Обращение к внутренней памяти за пределами микроконтроллера недопустимо, поскольку это может привести к программной несовместимости. Адресные координаторы преобразуют 8-ми или 16-ти битный логический адрес микроконтроллера в 32-х битный физический адрес системной шины и обеспечивают связь микроконтроллера с внешней памятью. Координаторы распределены между зонами логических адресов. Каждая из этих зон занимает от 256 байт до 64 Кбайт памяти и ссылается на определенную область физических адресов. Зона начинается с любого логического адреса и занимает объем в соответствии с её размерами. В случае найденного соответствия между адресом, микроконтроллера и адресом, на который ссылается координатор, логический адрес будет преобразован в физический.

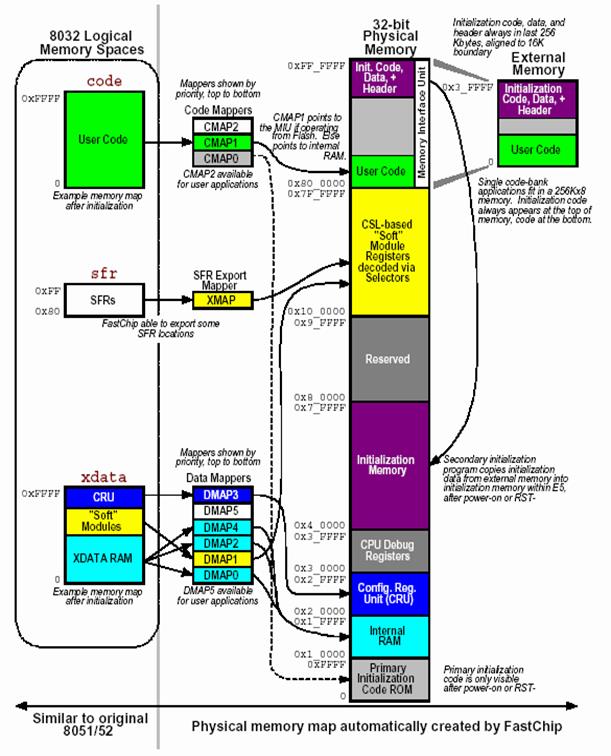

Рис. 33 Программная среда FastChip использует внутренние кодовые координаторы и координаторы данных для организации 16 Мб карты памяти.

Координаторы разделены по функциональному назначению: кодовые координаторы преобразуют адрес только кодов, координаторы данных - адрес только данных, а координаторы SFR – адрес SFR. Значение координаторов определяется в конфигурирующих регистрах. Каждый координатор имеет: 1. 8 бит адреса зоны, значение которого используются для определения соответствия с ожидаемым логическим адресом A{15:8}; 2. 5 бит смещения, которое определяется как логарифм с основанием два от значения размера зоны в байтах; 3. 24 бита - являются старшими битами физического адреса A{31:8}; 4. один бит разрешения.

Рис.34. Блок-диаграмма принципа работы адресного координатора Значение смещения (5 бит) определяет количество младших бит логического адреса, которые не будут учитываться в операции сравнения с целевым адресом зоны в координаторе. Ввиду того, что все зоны должны иметь размер от 256 байт и больше, то младшие 8 бит логического адреса в процессе сравнения не учитываются. В таком случае, координатор сравнивает старшие 8 бит логического адреса с 8-ю битами целевого адреса зоны и маскирует в соответствии со значением смещения определенное количество младших бит. После того, как адреса сравнены при установленном бите разрешения координатора, преобразованный адрес выставляется на системную шину. Младшие биты представленного физического адреса являются маскированными битами логического адреса и занимают адресные линии A{15:0}. Но ввиду того, что зоны имеют минимальный размер 256 байт, младший байт логического адреса неизменно переводиться в младший байт физического адреса. Старшие байты физического адреса представлены немаскированными значениями 24 бит координатора. В случае несоответствия логического адреса с целевым адресом зоны следующий ниже приоритетом координатор проверяет этот логический адрес. Данный процесс будет повторяться для всех координаторов одного типа (данных или кода) до тех пор, пока для логического адреса не найдется соответствие, которое всегда гарантирует координатор самого низкого приоритета. Выделенные ресурсы системной шины дешифрируют только 24 адресные линии A{23:0}, поскольку старшие 8 линий A{31:24} могут нести диагностическую информацию, используемую в целях отладки. Смещение, предусмотренное в координаторе, формирует маску, которая используется в процессе определения физического адреса. Смещение определяется как логарифм с основанием два от значения размера зоны в байтах. Маска же рассчитывается по формуле: Маска=2Смещение-1 Поскольку размер зоны варьируется от 256 байт до 64 Кбайт, то значение смещения равно числу от 8 до 16 (т.е. маскируются либо 8, либо 16 младших бит логического адреса). Различные системные ресурсы занимают адресные пространства, состоящие из нескольких несмежных участков в 4-х Гбайтовом пространстве, доступном через конфигурируемую системную шину. Программная среда FastChip автоматически формирует 16 Мбайтовую карту памяти, как показано в таблице 20 и на рис.33. Эта карта памяти представляет полные 4 Гбайт, поскольку старшие 8 бит физического адреса имеют значения, представленные в табл.23 и используемые в целях отладки. Адреса размещенные в системных ресурсах Таблица 20

Кодовые координаторы Предназначены для переадресации в процессе выборки кода. Существует всего три кодовых координатора, включая кодовый координатор для инициализационных программ, хранящихся во встроенном на кристалле ПЗУ, и два полностью программируемых координатора, как показано в таблице 21. Кодовые координаторы Таблица 21

С0 – кодовый координатор ПЗУ Имеет самый низкий приоритет. В случае системного сброса микроконтроллер всегда может обратиться к внутреннему ПЗУ. Размер ПЗУ составляет 1 Кбайт, и в памяти программ ПЗУ реализовано в 64 копиях, повторяющих 1 Кбайт. По окончании программы инициализации другие два кодовых координатора C1 и С2 могут быть запрограммированы на перерегулирование координатора С0. Кодовый координатор С0 имеет два регистра CMAP0_TAR и CMAP0_ALT, которые находятся в памяти регистров конфигурирующего назначения. В процессе преобразования логического адреса в физический через координатор С0, старший байт физического адреса A{31:24} будет содержать значение одного из регистров, т.е. содержать код операции либо операнд. Это предусмотрено в целях отладки, когда выборки кода операции и операнда различимы. С0 всегда активизирован.

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 454; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.145.202.60 (0.013 с.) |