Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

SFR export целевой адрес (средний байт)Содержание книги

Поиск на нашем сайте

Мнемоника: XMAP TAR 1 Адрес:FЕ21H SFR export целевой адрес (LATCH-команда)

Мнемоника: XMAP TAR 2 Адрес:FЕ22H SFR export целевой адрес (PIN-команда)

Мнемоника: XMAP ALT Адрес:FЕ24H Предусмотренные значения старшего байта адреса координаторов В таблице 23 представлены принятые по умолчанию значения старших адресных битов для каждого из координаторов. Эти значения загружаются в соответствующие регистры в процессе инициализации. Программная среда FastChip использует их при назначении 32-х битного физического адреса для адресных селекторов логической матрицы. Значения, представленные по умолчанию в таблице 23, и значения регистров адресных координаторов позволяют селекторам логической матрицы выборочно реагировать на различные типы команд. Например, если устройство FLASH памяти подключено к MIU (устройство сопряжения с внешней памятью), то по некоторому адресу можно обратиться как к сегменту кода или данных. В процессе обычных операций сегмент Flash памяти используется для хранения кода, а в процессе программирования Flash память расценивается как сегмент данных. Различие между кодом и данными отмечено в старшем байте адреса и используется при доступе к одному и тому же физическому адресу. В другом примере, предположим, что адресный селектор используется для активизации внешней памяти ПЗУ, на которую ссылается кодовый адресный координатор С1. Селектору необходимо реагировать как на выборку операнда, так и на выборку кода операции. В виду того, что регистры координатора имеют следующие значения CMAP1_TAR_2=00101000В (операнд) и CMA1_ALT=000010000В (код), то среда FastChip запрограммирует старший байт регистра маски селектора значением 0010000, делающим способным селектор реагировать на обе выборки кода операции и операнда. Значения адресных координаторов также используется блоком внутрисхемной отладки, чтобы различать выборки кода операций и операнда при доступе к памяти. Необходимость различать команды latch и pin возникает, если проектировщик выбирает 8051-совместимые порты ввода-вывода из модульной библиотеки программной среды. Для адресных селекторов логической матрицы нет никакой необходимости различать команды latch и pin. Значения старших байтов адреса адресных координаторов Таблица 23

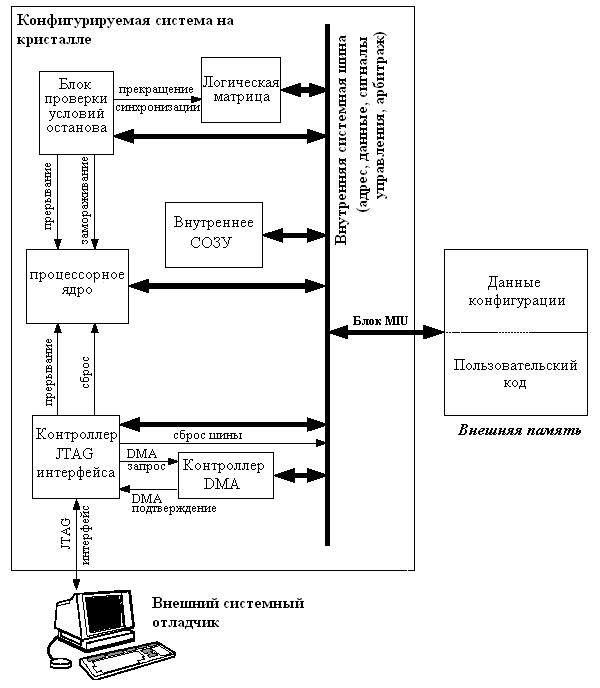

Система отладки Поддержка режима внутрисхемной отладки Персональный компьютер (ПК), используемый для проверки системы и проведения отладочных мероприятий, может взаимодействовать с конфигурируемой системой на кристалле Е5 через порт JTAG интерфейса при помощи кабеля, соединяющего параллельный порт ПК и целевую плату, как показано на рис.35. Блок JTAG интерфейса, являясь мастером на системной шине, имеет доступ ко всем адресуемым ресурсам системы, преобразует последовательность битов в параллельные коды шины адреса, шины данных и шины управления, поддерживая протоколы системной шины. Также блок JTAG интерфейса имеет доступ ко всем внутренним регистрам микроконтроллера и данным конфигурации логической матрицы с видимостью для функций, недоступных из прикладных программ. Кроме того, блок JTAG интерфейса может организовать сброс микроконтроллера через команду J_RESET или всей системы через команды FORCE_BRST и FORCE_NOBRST. Взаимодействует с микроконтроллером через механизм радиальных прерываний J_INTR. Во взаимодействии с контроллером DMA блок JTAG интерфейса выступает в роли подчиненного, руководствуясь его сигналами запроса и подтверждения. Предварительно, как мастер, он программирует блок DMA на процесс обмена данными, после чего передает ему шину. Это значительно упрощает задачу JTAG интерфейса, поскольку он не отвечает за адресное распределение и не управляет информацией в операциях прямого доступа к памяти. По отношению к блоку внутрисхемной отладки блок JTAG интерфейса является ведущим и может задавать различные условия останова. При этом блок внутрисхемной отладки поддерживает только два независимых условия останова. Первым из них могут являться определенные пользователем комбинации адресов, данных, сигналы управления и сигналы блока DMA, а вторым условием могут быть события логической матрицы, также заданные пользователем. Всего блок внутрисхемной отладки может насчитывать до 64К-1 событий, принимаемых за различные точки останова. В случае выполнения условия останова и в зависимости от своей текущей конфигурации микроконтроллер либо «замораживается» на конец текущей операции либо получает прерывание от блока внутрисхемной отладки и сосредотачивается на выполнении программы по обслуживанию прерывания. В случае замораживания микроконтроллера тактирование логической матрицы и глобальные сигналы могут быть прекращены с целью облегчения отладочного процесса. Программная среда FastChip позволяет пользователю выборочно назначить те сигналы, которые будут прекращены в момент останова микроконтроллера. Во время неактивного состояния микроконтроллера блок JTAG интерфейса может опросить любое адресное пространство в пределах системы и вне ее и послать необходимую информацию в компьютер для дальнейшего ее отображения и анализа.

Рис.35. Блок-схема реализации системной отладки По окончанию отладочного процесса блок JTAG интерфейса очищает вызвавшее останов условие, и микроконтроллер возвращается к выполнению операций, с которых его работа была временно прекращена. Кроме того, блок JTAG интерфейса может перезапустить выполнение кода с адреса 0000H с помощью команды J_RESET, данной микроконтроллеру, или ввести микроконтроллер в режим пошагового выполнения команд, при этом передавая компьютеру соответствующую текущему состоянию информацию. Порт JTAG интерфейса может быть также использован для конфигурации системы или для обновления устройств внешней памяти, подключенных к блоку сопряжения с внешней памятью. Блок JTAG интерфейса способствует тому, что алгоритмы для программирования устройства внешней Flash памяти загружаются во внутреннее ОЗУ системы. После этого он вступает в контакт с микроконтроллером, разрешая процессору контролировать действующие программные и тестовые алгоритмы, алгоритмы стирания, пока в JTAG порт поступают новые данные для программирования или команды, необходимые микроконтроллеру. Системные требования для реализации процесса отладки В отличие от отладчиков для традиционного микроконтроллера стандарта 8051 отладочная среда для конфигурируемой системы на кристалле Е5 не требует каких-либо дополнительных системных ресурсов, а именно, не нуждается в дополнительной памяти и услугах последовательного порта. Все отладочные операции осуществляются через четырех выводной разъем JTAG интерфейса. Внешний вид рекомендуемого слота представлен на рис. 36. Он имеет выводы диаметром 0,1 дюйма.

Рис.36 Внешняя часть слота JTAG интерфейса Также встроенный на кристалле блок внутрисхемной отладки не требует специальных внутрисхемных эмуляторов, поскольку содержит возможности, доступные большинству из них.

|

|||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 284; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.15.26.231 (0.009 с.) |