Заглавная страница Избранные статьи Случайная статья Познавательные статьи Новые добавления Обратная связь FAQ Написать работу КАТЕГОРИИ: ТОП 10 на сайте Приготовление дезинфицирующих растворов различной концентрацииТехника нижней прямой подачи мяча. Франко-прусская война (причины и последствия) Организация работы процедурного кабинета Смысловое и механическое запоминание, их место и роль в усвоении знаний Коммуникативные барьеры и пути их преодоления Обработка изделий медицинского назначения многократного применения Образцы текста публицистического стиля Четыре типа изменения баланса Задачи с ответами для Всероссийской олимпиады по праву

Мы поможем в написании ваших работ! ЗНАЕТЕ ЛИ ВЫ?

Влияние общества на человека

Приготовление дезинфицирующих растворов различной концентрации Практические работы по географии для 6 класса Организация работы процедурного кабинета Изменения в неживой природе осенью Уборка процедурного кабинета Сольфеджио. Все правила по сольфеджио Балочные системы. Определение реакций опор и моментов защемления |

Конфигурируемая системная шина (CSI)Содержание книги

Поиск на нашем сайте

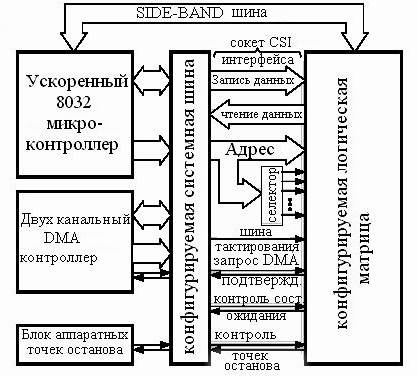

Конфигурируемая системная шина, представленная на рис.7, связывает микроконтроллер с его периферией и устройствами, реализованными в логической матрице. Представляет собой независимую от процессора шину будущих поколений конфигурируемых систем на кристалле. Программные модули, имеющиеся в наличие библиотек этой системы и созданные пользователем, могут быть переданы будущим семействам систем на кристалле без каких-либо значительных изменений. Сокет системной шины обеспечивает простой и синхронный интерфейс с программными модулями, реализованными в логической матрице, как показано на рис.8. Интерфейс системной шины содержит следующие элементы: 1. 8-разрядный порт, предназначенный для записи данных из памяти в логическую матрицу; 2. 8-разрядный порт, предназначенный для чтения данных из логической матрицы; отдельный сигнал разрешения чтения позволяет считывать данные из памяти; 3. 32-разрядный адресный порт; 4. набор специализированных селекторов, число которых варьируется в зависимости от модификации устройства; через селекторы, в основном, проходят сигналы запроса на прямой доступ к памяти от логического устройства, реализованного в матрице, и сигналы подтверждения от контроллера DMA; 5. шина тактирования; 6. сигналы слежения и контроля состоянием ожидания; 7. сигналы слежения и контроля процессом внутрисхемной отладки. Шина данных для чтения После того, как функция логической матрицы или программный модуль выставит сигнал разрешения чтения, данные будут выставлены на шину. Поскольку данные от всех функций логически складываются, то не задействованные модули предоставляют нулевые значения, и только выбранные – действительные. Данные для чтения могут выставляться с каждым тактом.

Рис. 2.7. Конфигурируемая системная шина (CSI) и интерфейс сокета с программным модулем конфигурируемой логической матрицы(CSL)

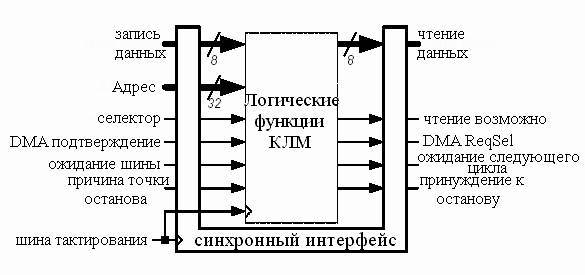

Рис.8. Интерфейс сокета системной шины, реализующий логические функции в КЛМ Шина данных для записи На сокет системной шины поступают 8 бит данных, предназначенных для записи. Данные для записи могут выставляться с каждым тактом. Адресная шина На сокет системной шины выходят 32 адресные линии. Устройства, реализованные в логической матрице, обычно используют только несколько адресных битов, а действительное значение адреса определяется адресными селекторами. Адресный селектор Интерфейс системной шины полностью исключает необходимость использования ресурсов матрицы на распознавание шинных протоколов. Одним из наиболее важных элементов интерфейса CSI является программируемая функция адресного дешифратора, называемая селектором. Селектор также исполняет функцию чип селектора или адресного дешифратора в устройстве со структурой PAL. Принцип действия адресного селектора Селектор читает протоколы для определенной области адресов. Распознает полный 32-рязрядный адрес, и, если протокол получен для его целевой области адресов, то селектор выставляет один из своих выходных сигналов с фронтом того же такта, в течение которого система предоставляет данные для записи и адрес размещения их в матрице. Это существенно упрощает логику доступа к устройствам, реализованным в логической матрице. Все действия селектора синхронизированы тактовыми сигналами системы. Число селекторов зависит от модификации устройства и растет с увеличением размера логической матрицы, как показано в табл.3. Один селектор приходится на 16 ячеек логической матрицы. Число селекторов в устройстве Таблица 3

Все селекторы имеют одинаковую функциональную структуру, как показано на рис.9. Каждый селектор содержит два 32-разрядных регистра, определяющих целевой адрес. Регистр MATCH0 предназначен для определения позиций нулевых битов в предоставленном адресе, а MATCH1 – позиций единичных битов адреса. Если один и тот же бит установлен в обоих регистрах, то соответствующий бит адреса не принимается во внимание. В случае соответствия всех битов адреса со значениями битов в регистрах MATCH0 и MATCH1 селектор определяет тип операции: чтение или запись. В случае чтения данных, селектор выставляет сигнал RDSEL, в случае записи – WRSEL. Адресная спецификация Значения регистров MATCH0 и MATCH1 автоматически определяются системой Triscend в процессе проектирования и не могут быть изменены программным обеспечением. Адреса, загружаемые в MATCH0 и MATCH1, являются символическими и назначаются пользователем в процессе аппаратного проектирования. Пользователь назначает: 1. символическое имя адресуемой области; 2. размер адресуемой области, который должен быть кратный двум и находиться в пределах от 1 до 16М байт; 3. адресное пространство или несколько пространств, которым селектор сможет отвечать, поскольку вместе с адресным координатором селектор распознает протоколы для определенного адресного пространства. Система на кристалле Е5, основанная на ядре стандарта 8051, поддерживает следующие адресные пространства: - DATA – память данных, соответствует памяти данных XDATA в 8051; - SFR – память размещения регистров специального назначения, занимает объем 128 байт и является уникальной в 8051. Программная среда FastChip проверяет эти установки для всех селекторов, назначенных при аппаратном проектировании. Таким образом определяется и назначается физический адрес для каждого селектора. Соответствующие логические адреса фиксируются в заголовочном файле и используются пользовательской программой. Значения регистров MATCH0 и MATCH1, определяемые средой FastChip, загружаются в селекторы в процессе конфигурации. Программная среда FastChip также определяет значения, первоначально загружаемые в регистры координаторов адреса. Функциональные возможности селектора Селектор выполняет одну из трех потенциальных функций, представленных в таблице 4. Функции адресного селектора Таблица 4

Селектор Селектор различает отдельно операции чтения и записи для целевой адресной области, как показано на рис.9. Выходной сигнал RDSEL свидетельствует об операции чтения, а WRSEL – записи.

Рис.9. Структура адресного селектора позволяет избежать построения адресных дешифраторов, использующих ресурсы логической матрицы Чип-селектор В этом режиме селектор определяет одну из операций чтение или запись для целевой адресной области, как показано на рис.10. Сигнал SEL – сигнал выбора микросхемы, сигнал RDSEL выставляется только при операции чтения. В библиотеке проектов это функция названа CHIPSEL.

Рис.10. В этом режиме селектор определяет одну из операций чтение или запись для целевой адресной области Контроль DMA В этом режиме селектор выполняет функцию контрольного распределяющего регистра DMA и фильтрует сигналы запроса REQSEL и подтверждения ACKSEL для выбранного канала. Внешний доступ через блок сопряжения с внешней памятью Программный модуль может получить доступ к внешним устройствам через выводы портов ввода/вывода или через блок сопряжения с внешней памятью (MIU). Специальный режим работы селектора позволяет функциям логической матрицы участвовать в обмене протоколами с внешним устройством через блок MIU, как показано на рис.11.

Рис.11.Внешние устройства разделяют сигналы блока сопряжения с внешней памятью. Flash-память подключается к системе по сигналу СЕ-, а все другие устройства реагируют на сигнал выбора микросхемы, генерируемый функцией внутри логической матрицы Поддержка циклов ожидания Интерфейс системной шины включает сигналы слежения и контроля состоянием ожидания внутренней системной шины. Сигнал ожидания WAITED Сигнал ожидания WAITED является выходным по отношению к сокету системной шины и указывает на то, что в течение предыдущего такта был запрос на организацию временной задержки. Используется обычно в контрольной логике таких функций, как FIFO или буфер двунаправленного порта. Сигнал WAITNEXT СигналWAITNEXT является входным по отношению к сокету системной шины. Некоторые устройства, реализованные в логической матрице, не поддерживают высокую скорость передачи данных, поэтому не в состоянии ответить за один такт. В этом случае селектор автоматически вызывает дополнительный такт временной задержки. Сигнал WAITNEXT требуется для организации задержек на более длительный период. С каждым передним фронтом тактового сигнала проверяется состояние сигнала WAITNEXT, и, если он активен, то следующий такт будет тактом временной задержки. Таким образом, когда возникает необходимость организации длительной временной задержки, программный модуль должен выставить сигнал WAITNEXT до следующего переднего фронта тактового сигнала, чтобы вызвать временную задержку в следующем такте. Организация тактов временной задержки Требуется, когда устройство, реализованное в логической матрице, участвует в обмене данными с асинхронным устройством или не обладает соответствующей скоростью, чтобы отвечать за один такт. Селектор настроен таким образом, чтобы в случае необходимости организовать первый такт временной задержки. Это произойдет, если система обращается к целевой адресной области селектора. В случае необходимости длительной временной задержки, программный модуль логической матрицы должен выставить сигнал WAITNEXT. Поддержка внутрисхемной отладки Интерфейс системной шины включает сигналы слежения и контроля процессом внутрисхемной отладки. Сигнал BREAK СигналBREAK является входным по отношению к сокету системной шины и позволяет программному модулю логической матрицы связаться с блоком внутрисхемной отладки. Блок внутрисхемной отладки в основном предназначен для слежения за протоколами системной шины. Программный модуль может обратиться к блоку внутрисхемной отладки через сигнал BREAK. Это даст возможность функции логической матрицы следить за потоком информационных пакетов, проходящих по системной шине, и в случае обнаружения ошибки вызвать останов всей системы. После этого через JTAG-интерфейс можно отследить состояние системы и логической матрицы. Сигнал EVENT СигналEVENT является выходным по отношению к сокету системной шины и позволяет программному модулю логической матрицы следить за состоянием блока внутрисхемной отладки. Когда сигнал EVENT активен, то останов системы произойдет при выполнении одного из условий останова, заданных в блоке внутрисхемной отладки, или по инициативе модуля логической матрицы. Протоколы системной шины В данном разделе описаны примеры протоколов системной шины, демонстрирующие взаимодействие устройства, реализованного в логической матрице, и интерфейса системной шины. Операция записи данных В процессе выполнения этой операции происходит запись данных в программный модуль, реализованный в логической матрице. При этом система предоставляет адрес и данные в интерфейс системной шины. На рис.12 показана временная диаграмма одного такта записи данных в модуль матрицы. Адрес дешифрируется селектором. Если протокол направлен к целевой адресной области селектора, то тот выставит сигнал WRSEL. Программный модуль использует этот сигнал для того, чтобы активизировать регистр и захватить данные.

Рис.12. Однотактный протокол записи данных в программный модуль На рис.13 представлена временная диаграмма процесса записи данных в модуль логической матрицы длительностью два такта. Селектор сконфигурирован таким образом, чтобы при необходимости организовать один такт задержки. Если протокол направлен к целевой адресной области селектора, то тот выставит сигнал WRSEL и автоматически вызовет такт задержки. В течение второго такта селектор будет продолжать удерживать сигнал WRSEL, а программный модуль логической матрицы примет данные. При этом сигнал WAITNEXT не выставится, но активизируется сигнал WAITED, регистрирующий запрос такта задержки, вызванный селектором в первом такте. Процесс записи закончится после второго такта, и селектор снимет свой сигнал WRSEL.

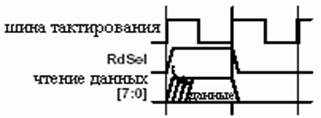

Рис.13. Два такта записи данных в устройство, реализованное в логической матрице Операция чтения данных В процессе выполнения этой операции происходит считывание данных из устройства, реализованного в логической матрице. На рис.14 показана временная диаграмма процесса чтения данных за один такт. Адрес для чтения данных поступает в интерфейс системной шины, после чего дешифрируется селектором. Селектор выставляет сигнал RDSEL, а устройство, реализованное в логической матрице, предоставляет данные для чтения в выходной порт интерфейса системной шины.

Рис.14. Один такт чтения данных из устройства, реализованного в логической матрице На рис.15 представлена временная диаграмма процесса чтения данных из модуля логической матрицы длительностью два такта. Селектор сконфигурирован таким образом, чтобы при необходимости организовать один такт задержки. Если протокол направлен к целевой адресной области селектора, то тот выставит сигнал RDSEL и автоматически вызовет такт задержки. В течение второго такта селектор будет продолжать удерживать сигнал RDSEL, а программный модуль логической матрицы предоставит данные. При этом сигнал WAITNEXT не выставится, но активизируется сигнал WAITED, регистрирующий запрос такта задержки, вызванный селектором в первом такте. Процесс чтения закончится после второго такта, и селектор снимет свой сигнал RDSEL.

Рис.15. Два такта чтения данных из устройства, реализованного в логической матрице Использование сигнала WAITNEXT Существуют четыре основных правила организации временной задержки в зависимости от быстродействия устройства, реализованного в логической матрице: 1. временная задержка не требуется, если устройство способно ответить в течение одного такта; 2. устройству, реализованному в логической матрице, требуется один такт задержки, который автоматически организует селектор; 3. устройству требуется больше, чем один такт временной задержки, три и более, из которых первый такт организует селектор, а остальные – устройство, реализованное в логической матрице, с помощью сигнала WAITNEXT; 4. если для одного протокола, чтения или записи, требуется несколько тактов временной задержки, а для другого, записи или чтения, по крайней мере, один, то первоначальная временная задержка будет организовываться селектором для обоих протоколов. На рис.16 представлена временная диаграмма чтения данных с применением сигнала WAITNEXT. В течение первого такта селектор выставит сигнал RDSEL. В этом примере устройству потребуется, по меньшей мере, один такт задержки, поэтому первую задержку организует селектор. Устройство в течение первого такта определит, что не готово предоставить данные во втором такте, и выставит сигнал WAITNEXT, который вызовет второй такт задержки, или третий такт цикла обмена. В течение второго такта система будет удерживать адрес на шине, а селектор – удерживать сигнал RDSEL. Устройство определит, что готово представить данные в следующем такте и снимет сигнал WAITNEXT. При этом активизируется сигнал WAITED, регистрирующий запрос такта задержки, вызванный селектором в первом такте. На третьем такте устройство выставит данные на шину, после чего селектор снимет сигнал RDSEL. Сигнал WAITED будет удерживаться до конца третьего такта, поскольку временная задержка реализована за два такта.

Рис.16. Пример протекания процесса чтения данных с использованием сигнала WAITNEXT Специализированные сигналы Side-band Все сигналы интерфейса системной шины являются процессоро-независимыми. Программные модули логической матрицы, спроектированные с использованием этого интерфейса, могут использоваться другими семействами конфигурируемых систем на кристалле, совместимых с компанией Trisend. Несмотря на вышесказанное, некоторые сигналы свойственны только данному процессору и называются сигналами Side-band. Для семейства Trisend Е5 эти сигналы включают функции, уникальные для 8051 микроконтроллера. Например, для ядра стандарта 8051 некоторые из выводов портов ввода/вывода имеют разделенные функциональные назначения. Например, внешний вход таймера 0 – это 4 вывод порта 3. В Е5 такие сигналы могут быть подведены к любому выводу портов и даже к устройствам, реализованным в логической матрице. Сигналы Side-band для семейства Е5 представлены в таблице 5.

SIDEBAND сигналы семейства Е5 Таблица.5

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2016-08-26; просмотров: 574; Нарушение авторского права страницы; Мы поможем в написании вашей работы! infopedia.su Все материалы представленные на сайте исключительно с целью ознакомления читателями и не преследуют коммерческих целей или нарушение авторских прав. Обратная связь - 3.133.157.163 (0.01 с.) |